越來越多的嵌入式和物聯(lián)網設備需要更多的程序存儲器,而不是使用嵌入式閃存或SRAM在片上經濟地實現(xiàn)的存儲器。對于這些設計,越來越多的設計正在轉向就地執(zhí)行(XiP)操作,其中代碼直接從外部NOR閃存設備執(zhí)行,通過這種方式可以實現(xiàn)其系統(tǒng)的可擴展性。

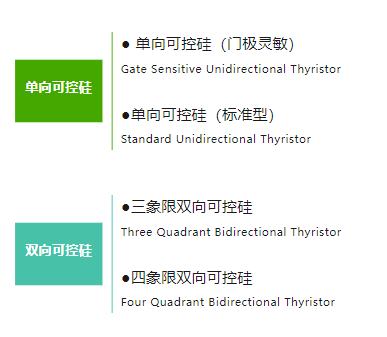

大多數(shù)設計人員通常會為其 XiP 系統(tǒng)選擇四通道串行外設接口 (SPI) 存儲器,因為它是成本最低的選擇。但是,根據具體應用,設計人員在使用四通道器件時可能無法滿足性能要求。

他們可以通過進行軟件優(yōu)化來解決這個問題,但這種更改通常需要軟件團隊花費數(shù)周甚至數(shù)月來優(yōu)化設計,即使這樣,優(yōu)化仍然可能還不夠。最終可能有必要從設計中消除特征。另一種選擇是提高處理器的時鐘速度以實現(xiàn)所需的性能,但這可能會提供遞減的回報并增加系統(tǒng)能耗,并增加潛在的電池尺寸,從而降低成本。當然,一些設計已經讓處理器以最大時鐘速度運行,在這種情況下,可能需要升級到更快、更昂貴的處理器。

設計人員應考慮的一個選項是從四通道SPI器件轉向八通道SPI器件進行設計。雖然此舉不會對所有應用程序產生巨大影響,但有一些應用程序將受益匪淺。在那些對閃存性能敏感的應用中可以看到這種優(yōu)勢。

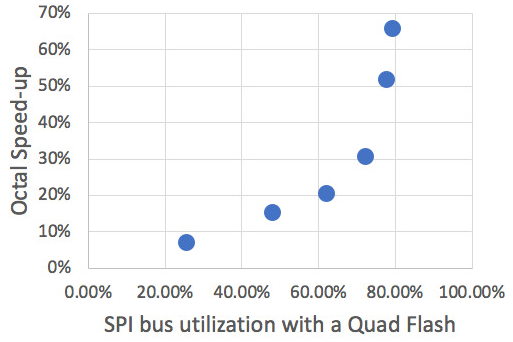

預測這一點的簡單方法是查看SPI總線上的流量。如果應用程序大部分都在緩存中運行,則不會在總線上看到大量事務。當您開始看到總線的大量流量/高利用率時,您就會知道它更依賴于閃存。如果總線利用率很高,切換到像Adesto的EcoXiP這樣的八通道器件的收益是相當可觀的。最終,這可以轉化為顯著的能源和成本節(jié)約。

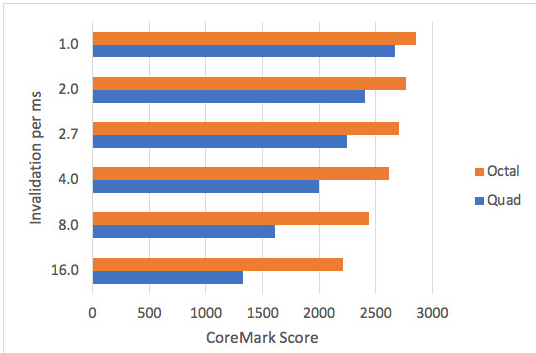

我們 使用 邏輯 分析 器 來 測量 四 通道 模式 的 SPI 總 線 利用率, 以 觀察 在 切換 到 八 通道 器件 時 其 與 系統(tǒng) 加速 的 關聯(lián) 關系。我們運行了 CoreMark 基準測試,通過以固定間隔清除緩存的內容(緩存失效),在總線上生成更多/更少的流量。這些緩存失效旨在模擬任務切換和中斷頻繁的實時系統(tǒng)場景。通過使間隔越來越短,我們增加了公共汽車上的交通量。

您可以看到,在某些領域,四元和八進制性能之間的差異并不大,但隨后它會向上擺動。在這一點上,值得考慮轉向八進制設備。當應用程序演示SPI總線利用率達到60%或更高時,您可以看到其優(yōu)勢。

在許多系統(tǒng)中,功率是一個重要的考慮因素。我們希望確保使用八進制器件可以獲得的額外性能不會與更高的系統(tǒng)級功耗相權衡。我們使用相同的設置來測量恩智浦 i.MX RT1050 MCU在就地擴展模式下運行時的功耗。我們使用相同的技術,以固定的時間間隔注入緩存失效,并測量MCU和閃存的功率。下圖顯示,在我們測試的所有場景中,Octal EcoXiP 比傳統(tǒng)的 Quad 設備更節(jié)能。EcoXiP 在每種情況下都提供了更多的每 mW 核心標記。同樣有趣的是,EcoXiP 的功耗優(yōu)勢隨著工作負載的加劇而增加,工作負載的緩存未命中次數(shù)更多,從而在 SPI 總線上產生更多流量。

如果您使用的是恩智浦 i.MX RT1050這樣的器件,您可以輕松地將Quad器件換成八進制器件,因為該芯片的架構巧妙,可以同時支持兩者。

審核編輯:郭婷

-

嵌入式

+關注

關注

5068文章

19021瀏覽量

303326 -

存儲器

+關注

關注

38文章

7453瀏覽量

163608 -

物聯(lián)網

+關注

關注

2903文章

44284瀏覽量

371308

發(fā)布評論請先 登錄

相關推薦

PCIe延遲對系統(tǒng)性能的影響

基于TI AM62x的Debian系統(tǒng)正式發(fā)布,豐富的軟件生態(tài),讓您的應用開發(fā)更便利!

全志T507-H國產平臺Ubuntu系統(tǒng)正式發(fā)布,讓您的應用開發(fā)更便捷!

如何評估機床測頭的性能是否滿足特定行業(yè)的需求?

搭建光學相干斷層掃描(OCT)系統(tǒng)您需要知道

邏輯器件四路二輸入是什么意思

搭載新款VPC-5640S,您專案的幕后推手

電源模塊可以實現(xiàn)哪些功能 保護您的設備,避免過載和短路!高效電源模塊,穩(wěn)定供電

噪聲如何影響高速信號鏈的總動態(tài)系統(tǒng)性能

您的四路設備是否可以滿足您的系統(tǒng)性能

您的四路設備是否可以滿足您的系統(tǒng)性能

評論