據(jù)Hyperion Research 公司按照系統(tǒng)驗(yàn)收的時(shí)間估算,2021至2026年期間,全球?qū)⒔ǔ?8~38臺(tái)E級(jí)或接近 E 級(jí)的超級(jí)計(jì)算機(jī)。

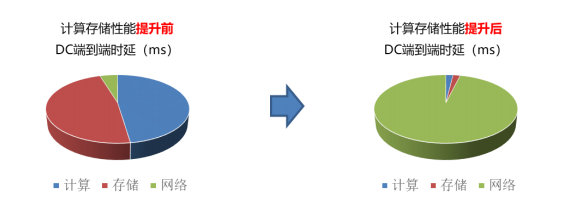

在原先傳統(tǒng)數(shù)據(jù)中心內(nèi),計(jì)算存儲(chǔ)性能未提升前,端到端的時(shí)延主要在端側(cè),即計(jì)算和存儲(chǔ)所消耗的時(shí)延占比較大,而當(dāng)計(jì)算存儲(chǔ)器件性能大幅提升后,網(wǎng)絡(luò)成為了數(shù)據(jù)中心內(nèi)端到端的性能瓶頸。下圖顯示了計(jì)算存儲(chǔ)性能提升前后,端到端時(shí)延的占比變化。

01RDMA 技術(shù)實(shí)現(xiàn)業(yè)務(wù)加速

但制式種類繁多

存儲(chǔ)和計(jì)算性能提升后,數(shù)據(jù)中心內(nèi)二者的訪問(wèn)時(shí)延已經(jīng)從 10ms優(yōu)化達(dá)到了 20us 的水平量級(jí),相比原來(lái)有了近千倍的提升。而此時(shí),如若仍舊采用基于 TCP 協(xié)議的網(wǎng)絡(luò)傳輸機(jī)制,由于 TCP 的丟包重傳機(jī)制,其網(wǎng)絡(luò)時(shí)延仍舊維持在 ms 級(jí)水平,無(wú)法滿足高性能計(jì)算存儲(chǔ)對(duì)于時(shí)延的要求。此時(shí),RDMA 技術(shù)的出現(xiàn),為網(wǎng)絡(luò)性能的提升提供了新的技術(shù)思路。

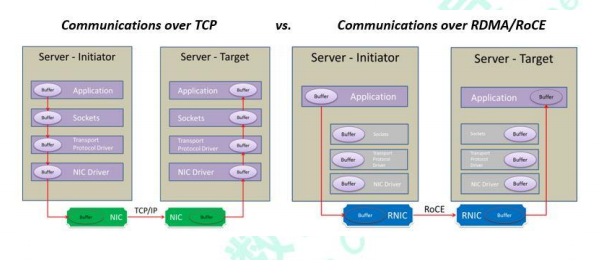

RDMA 是一種概念,在兩個(gè)或者多個(gè)計(jì)算機(jī)進(jìn)行通訊的時(shí)候使用 DMA, 從一個(gè)主機(jī)的內(nèi)存直接訪問(wèn)另一個(gè)主機(jī)的內(nèi)存。傳統(tǒng)的 TCP/IP 技術(shù)在數(shù)據(jù)包處理過(guò)程中,要經(jīng)過(guò)操作系統(tǒng)及其他軟件層,需要占用大量的服務(wù)器資源和內(nèi)存總線帶寬,數(shù)據(jù)在系統(tǒng)內(nèi)存、處理器緩存和網(wǎng)絡(luò)控制器緩存之間來(lái)回進(jìn)行復(fù)制移動(dòng),給服務(wù)器的 CPU 和內(nèi)存造成了沉重負(fù)擔(dān)。尤其是網(wǎng)絡(luò)帶寬、處理器速度與內(nèi)存帶寬三者的嚴(yán)重“不匹配性”,更加劇了網(wǎng)絡(luò)延遲效應(yīng)。

RDMA 是一種新的直接內(nèi)存訪問(wèn)技術(shù),RDMA 讓計(jì)算機(jī)可以直接存取其他計(jì)算機(jī)的內(nèi)存,而不需要經(jīng)過(guò)處理器的處理。RDMA 將數(shù)據(jù)從一個(gè)系統(tǒng)快速移動(dòng)到遠(yuǎn)程系統(tǒng)的內(nèi)存中,而不對(duì)操作系統(tǒng)造成任何影響。

在實(shí)現(xiàn)上,RDMA 實(shí)際上是一種智能網(wǎng)卡與軟件架構(gòu)充分優(yōu)化的遠(yuǎn)端內(nèi)存直接高速訪問(wèn)技術(shù),通過(guò)將 RDMA 協(xié)議固化于硬件(即網(wǎng)卡)上,以及支持 Zero-copy和 Kernel bypass 這兩種途徑來(lái)達(dá)到其高性能的遠(yuǎn)程直接數(shù)據(jù)存取的目標(biāo)。下圖為 RDMA 工作的原理圖,其通信過(guò)程使得用戶在使用 RDMA 時(shí)具備如下優(yōu)勢(shì):

?零拷貝(Zero-copy) - 應(yīng)用程序能夠直接執(zhí)行數(shù)據(jù)傳輸,在不涉及到網(wǎng)絡(luò)軟件棧的情況下。數(shù)據(jù)能夠被直接發(fā)送到緩沖區(qū)或者能夠直接從緩沖區(qū)里接收,而不需要被復(fù)制到網(wǎng)絡(luò)層。

?內(nèi)核旁路(Kernel bypass) - 應(yīng)用程序可以直接在用戶態(tài)執(zhí)行數(shù)據(jù)傳輸,不需要在內(nèi)核態(tài)與用戶態(tài)之間做上下文切換。

?不需要 CPU 干預(yù)(No CPU involvement) - 應(yīng)用程序可以訪問(wèn)遠(yuǎn)程主機(jī)內(nèi)存而不消耗遠(yuǎn)程主機(jī)中的任何 CPU。遠(yuǎn)程主機(jī)內(nèi)存能夠被讀取而不需要遠(yuǎn)程主機(jī)上的進(jìn)程(或 CPU)參與。遠(yuǎn)程主機(jī)的 CPU 的緩存(cache)不會(huì)被訪問(wèn)的內(nèi)存內(nèi)容所填充。

?消息基于事務(wù)(Message based transactions) - 數(shù)據(jù)被處理為離散消息而不是流,消除了應(yīng)用程序?qū)⒘髑懈顬椴煌?事務(wù)的需求。

?支持分散/聚合條目(Scatter/gather entries support) - RDMA 原生態(tài)支持分散/聚合。也就是說(shuō),讀取多個(gè)內(nèi)存緩沖區(qū)然后作為一個(gè)流發(fā)出去或者接收一個(gè)流然后寫(xiě)入到多個(gè)內(nèi)存緩沖區(qū)里去。

目前,RDMA 技術(shù)在超算、AI 訓(xùn)練、存儲(chǔ)等多個(gè)高性能場(chǎng)景大量部署,已形成廣泛應(yīng)用。但是 RDMA 技術(shù)路線也有很多,用戶及各家廠商對(duì)于 RDMA 技術(shù)路線的選擇也不盡相同。

在三種主流的 RDMA 技術(shù)中,可以劃分為兩大陣營(yíng)。一個(gè)是 IB 技術(shù), 另一個(gè)是支持 RDMA 的以太網(wǎng)技術(shù)(RoCE 和 iWARP)。其中,IBTA 主要聚焦 IB 和 RoCE 技術(shù),而 iWARP 則是在 IEEE/IETF 標(biāo)準(zhǔn)化的技術(shù)。在存儲(chǔ)領(lǐng)域,支持 RDMA 的技術(shù)早就存在,比如SRP(SCSI RDMA Protocol)和iSER(iSCSI Extensions for RDMA)。如今興起的 NVMe over Fabrics 如果使用的不是 FC 網(wǎng)絡(luò)的話,本質(zhì)上就是 NVMe over RDMA。換句話說(shuō),NVMe over InfiniBand, NVMe over RoCE 和 NVMe over iWARP 都是 NVMe over RDMA。

02RoCE 成為主流

但仍難以滿足業(yè)務(wù)需求

以太網(wǎng)自面世以來(lái),其生態(tài)開(kāi)放多元、速率高速增長(zhǎng)、成本優(yōu)勢(shì)明顯,因此業(yè)界應(yīng)用十分廣泛。在 RDMA 的多種技術(shù)路線中,RoCE 技術(shù)的應(yīng)用最為廣泛。在全球著名高性能計(jì)算榜單 Top500 中,以太互聯(lián)技術(shù)占比超過(guò)一半。

然而受限于傳統(tǒng)以太網(wǎng)絡(luò)的性能瓶頸,一般的 RoCE 應(yīng)用在高性能業(yè)務(wù)中,仍然存在擁塞丟包、延遲抖動(dòng)等性能損失,難以滿足高性能計(jì)算和存儲(chǔ)的需求。

在高性能存儲(chǔ)集群中,F(xiàn)C 網(wǎng)絡(luò)具備連接保持技術(shù),網(wǎng)絡(luò)升級(jí)&進(jìn)程故障業(yè)務(wù)不感知,同時(shí) FC 協(xié)議長(zhǎng)幀頭具備傳輸功能保障,協(xié)議開(kāi)銷小,網(wǎng)絡(luò)無(wú)丟包,數(shù)據(jù)幀按序傳送,網(wǎng)絡(luò)可靠、時(shí)延低。相比 FC,傳統(tǒng)以太網(wǎng)容易出現(xiàn)擁塞丟包現(xiàn)象,丟包重傳容易產(chǎn)生數(shù)據(jù)亂序,網(wǎng)絡(luò)抖動(dòng)較大,并且以太網(wǎng)采用的存儲(chǔ)轉(zhuǎn)發(fā)模式,查找流程較為復(fù)雜導(dǎo)致轉(zhuǎn)發(fā)時(shí)延較高,多打一場(chǎng)景會(huì)導(dǎo)致隊(duì)列積壓加劇,隊(duì)列時(shí)延不可忽視。在 HPC 應(yīng)用中,傳統(tǒng)以太消息封裝能力較弱,查表流程復(fù)雜導(dǎo)致轉(zhuǎn)發(fā)時(shí)延較高,網(wǎng)絡(luò)的傳輸損失會(huì)造成處理器空閑等待數(shù)據(jù),進(jìn)而拖累整體并行計(jì)算性能,根據(jù) 2017 年 ODCC 組織的測(cè)試結(jié)果,傳統(tǒng)以太和專網(wǎng)相比,在超算集群應(yīng)用下,性能最高相差 30%。

03總線級(jí)數(shù)據(jù)中心網(wǎng)絡(luò)

DCN全以太超融合發(fā)展

高性能計(jì)算在金融、證券、教育、工業(yè)、航天、氣象等行業(yè)廣泛應(yīng)用,而時(shí)延是關(guān)鍵性能指標(biāo)之一。由于以太網(wǎng)丟包、傳輸轉(zhuǎn)發(fā)機(jī)制等諸多原因,基于傳統(tǒng)以太的數(shù)據(jù)中心網(wǎng)絡(luò)時(shí)延大多處于毫秒級(jí)水平,無(wú)法支撐高性能計(jì)算業(yè)務(wù)。要使得 DC as a Computer 成為可能,數(shù)據(jù)中心網(wǎng)絡(luò)時(shí)延需要向總線級(jí)看齊。

04總線級(jí)數(shù)據(jù)中心網(wǎng)絡(luò)內(nèi)涵

傳統(tǒng)以太時(shí)延較高,無(wú)法滿足以高性能計(jì)算的性能要求。更為嚴(yán)峻的是,當(dāng)前我國(guó)高性能存儲(chǔ)和高性能計(jì)算所采用的高端網(wǎng)絡(luò)互聯(lián)設(shè)備,均被國(guó)外廠商壟斷,價(jià)格昂貴、專網(wǎng)設(shè)備互通性差,并存在關(guān)鍵供貨被卡脖子的風(fēng)險(xiǎn)。

由于以太網(wǎng)的丟包、傳輸、轉(zhuǎn)發(fā)等諸多原因,傳統(tǒng)的數(shù)據(jù)中心網(wǎng)絡(luò)時(shí)延大多處于 ms 級(jí)水平,無(wú)法支撐高性能計(jì)算業(yè)務(wù)。隨著高性能業(yè)務(wù)的飛速發(fā)展,計(jì)算設(shè)備已由原先以 CPU 為代表的通用器件,轉(zhuǎn)而發(fā)展為以 GPU 為主的高性能器件,器件的性能大幅提升,這對(duì)以太網(wǎng)絡(luò)的性能提出了更高的要求。網(wǎng)絡(luò)時(shí)延由四部分組成:

動(dòng)態(tài)時(shí)延:主要由排隊(duì)時(shí)延產(chǎn)生,受端口擁塞影響;

靜態(tài)時(shí)延:主要包括網(wǎng)絡(luò)轉(zhuǎn)發(fā)(查表)時(shí)延和轉(zhuǎn)發(fā)接口時(shí)延,一般為固定值,當(dāng)前以太交換靜態(tài)時(shí)延遠(yuǎn)高于超算專網(wǎng);

網(wǎng)絡(luò)跳數(shù):指消息在網(wǎng)絡(luò)中所經(jīng)歷的設(shè)備數(shù);

入網(wǎng)次數(shù):指消息進(jìn)入網(wǎng)絡(luò)的次數(shù)。總線級(jí)數(shù)據(jù)中心網(wǎng)絡(luò)在動(dòng)態(tài)時(shí)延、靜態(tài)時(shí)延、網(wǎng)絡(luò)跳數(shù)以及入網(wǎng)次數(shù)幾個(gè)方面均作出了系統(tǒng)性的優(yōu)化,大幅優(yōu)化了網(wǎng)絡(luò)性能,已滿足高性能計(jì)算場(chǎng)景的實(shí)際訴求。

05極低靜態(tài)轉(zhuǎn)發(fā)時(shí)延技術(shù),

轉(zhuǎn)發(fā)時(shí)延從us降至百ns

傳統(tǒng)的以太交換機(jī)在轉(zhuǎn)發(fā)層面,因需要考慮兼容性、支持眾多協(xié)議,導(dǎo)致轉(zhuǎn)發(fā)流程復(fù)雜,轉(zhuǎn)發(fā)時(shí)延較大。與此同時(shí),以太查表算法復(fù)雜、查表時(shí)延大,導(dǎo)致整體轉(zhuǎn)發(fā)處理時(shí)延長(zhǎng)。目前業(yè)界主流商用以太交換機(jī)的靜態(tài)轉(zhuǎn)發(fā)時(shí)延大約在600ns-1us 左右。面向大數(shù)據(jù)存儲(chǔ)和高性能計(jì)算業(yè)務(wù),若要以太網(wǎng)做到低時(shí)延,必須優(yōu)化轉(zhuǎn)發(fā)流程,降低數(shù)據(jù)轉(zhuǎn)發(fā)時(shí)延。

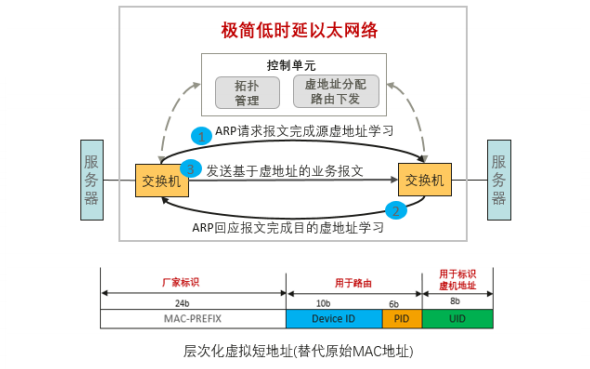

總線級(jí)數(shù)據(jù)中心網(wǎng)絡(luò)技術(shù)提出了一種極簡(jiǎn)低時(shí)延以太轉(zhuǎn)發(fā)機(jī)制,利用虛擬短地址,實(shí)現(xiàn)了快速線性表轉(zhuǎn)發(fā)。基于虛擬地址路由轉(zhuǎn)發(fā)技術(shù),解決了傳統(tǒng)二層環(huán)路和鏈路利用率的問(wèn)題,同時(shí)保證了規(guī)模部署和擴(kuò)展靈活性。

根據(jù)應(yīng)用實(shí)測(cè),目前低時(shí)延機(jī)制轉(zhuǎn)發(fā)機(jī)制能實(shí)現(xiàn) 30ns 以太芯片報(bào)文處理,實(shí)現(xiàn) 100ns 左右端到端單跳轉(zhuǎn)發(fā)靜態(tài)時(shí)延。該時(shí)延相比于業(yè)界主流歐美廠商的以太芯片轉(zhuǎn)發(fā)時(shí)延,提升了 6-10 倍。

06Bufferless 無(wú)阻塞流控技術(shù),

亞us級(jí)動(dòng)態(tài)時(shí)延

網(wǎng)絡(luò)擁塞會(huì)引起數(shù)據(jù)包在網(wǎng)絡(luò)設(shè)備中排隊(duì)甚至導(dǎo)致隊(duì)列溢出而丟棄,是導(dǎo)致網(wǎng)絡(luò)高動(dòng)態(tài)時(shí)延的主要原因。

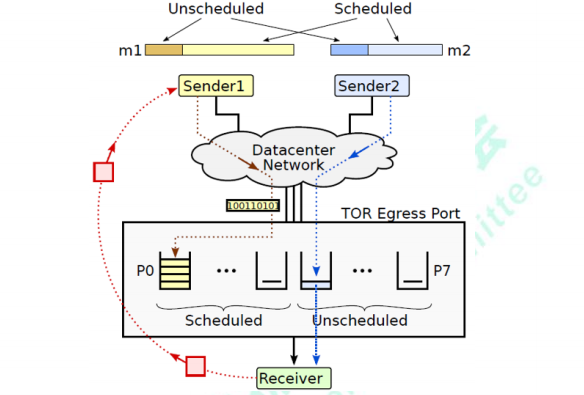

總線級(jí)數(shù)據(jù)中心網(wǎng)絡(luò)技術(shù)創(chuàng)新提出了收發(fā)混合驅(qū)動(dòng)的網(wǎng)絡(luò)擁塞控制機(jī)制。數(shù)據(jù)報(bào)文分為無(wú)調(diào)度(Unscheduled)和有調(diào)度(Scheduled)兩類:無(wú)調(diào)度報(bào)文在端口級(jí)有限窗口控制下直接發(fā)送,快速啟動(dòng),保證高吞吐;有調(diào)度報(bào)文由接收端分配令牌報(bào)文(Token)后繼續(xù)發(fā)送,限制流量注入,提供(近似)零隊(duì)列,支撐更大的網(wǎng)絡(luò)規(guī)模。對(duì)兩類報(bào)文進(jìn)行協(xié)同調(diào)度,進(jìn)一步保證高吞吐低隊(duì)列。收發(fā)混合驅(qū)動(dòng)的網(wǎng)絡(luò)擁塞控制機(jī)制實(shí)現(xiàn)了數(shù)據(jù)中心網(wǎng)絡(luò)高吞吐和近似零隊(duì)列,支撐大規(guī)模網(wǎng)絡(luò)動(dòng)態(tài)實(shí)時(shí)無(wú)阻塞。

最大吞吐保證:僅優(yōu)先發(fā)送部分報(bào)文,同樣提供最大吞吐保證。

極低平均隊(duì)列時(shí)延:通過(guò)接收端調(diào)度,嚴(yán)格控制網(wǎng)絡(luò)注入流量,保證接近于0的平均隊(duì)列時(shí)延。

極低最大隊(duì)列時(shí)延:對(duì)于不由接收端調(diào)度的報(bào)文,通過(guò)窗口限制注入流量,不會(huì)出現(xiàn)大幅震蕩,保證最大隊(duì)列時(shí)延極低。

07DCI 長(zhǎng)距無(wú)損技術(shù)動(dòng)態(tài)時(shí)延,

100KM內(nèi)長(zhǎng)距無(wú)損

在高性能存儲(chǔ)業(yè)務(wù)使用環(huán)境中,數(shù)據(jù)中心交換機(jī)之間涉及到遠(yuǎn)端設(shè)備之間的擁塞問(wèn)題。傳統(tǒng)的鏈路層流控技術(shù)采用粗暴的“停等”機(jī)制,當(dāng)下游設(shè)備發(fā)現(xiàn)接收能力小于上游設(shè)備的發(fā)送能力時(shí),會(huì)主動(dòng)發(fā) Pause 幀給上游設(shè)備,要求暫停流量的發(fā)送。若采用傳統(tǒng)的流控機(jī)制,數(shù)據(jù)中心網(wǎng)絡(luò)遠(yuǎn)端設(shè)備之間的流控會(huì)導(dǎo)致極高時(shí)延,以 100km 舉例,100Gbps 傳輸速率為例,基于傳統(tǒng)的 PFC 機(jī)制的設(shè)備間流控機(jī)制會(huì)產(chǎn)生將近 2ms 的時(shí)延,無(wú)法滿足高性能應(yīng)用的性能要求。

針對(duì)這個(gè)問(wèn)題,總線級(jí)數(shù)據(jù)中心網(wǎng)絡(luò)提出了“點(diǎn)剎”式長(zhǎng)距互聯(lián)的流控機(jī)制。采用細(xì)粒度的周期性掃描方式進(jìn)行流控;每個(gè)周期檢測(cè)入口 buffer 的變化速率,通過(guò)創(chuàng)新算法計(jì)算要求上游停止發(fā)送時(shí)間;構(gòu)造反壓幀,發(fā)送給上游設(shè)備,包含了要求上游停止發(fā)送的時(shí)間。

08網(wǎng)絡(luò)新拓?fù)浼軜?gòu)路由技術(shù),

大規(guī)模組網(wǎng)實(shí)現(xiàn)跳數(shù)下降20%

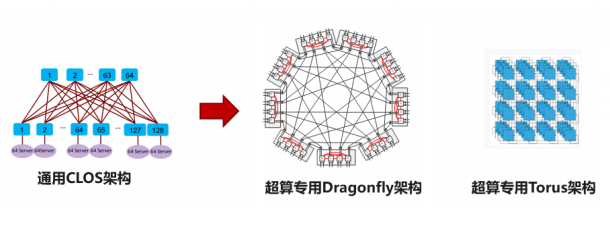

針對(duì)高性能計(jì)算場(chǎng)景,數(shù)據(jù)中心的流量特征關(guān)注靜態(tài)時(shí)延,需要支持超大規(guī)模,傳統(tǒng)的 CLOS 架構(gòu)作為主流的網(wǎng)絡(luò)架構(gòu),其主要關(guān)注通用性,但是犧牲了時(shí)延和性價(jià)比。業(yè)界針對(duì)該問(wèn)題開(kāi)展了多樣的架構(gòu)研究和新拓?fù)涞脑O(shè)計(jì)。

當(dāng)前數(shù)據(jù)中心網(wǎng)絡(luò)架構(gòu)設(shè)計(jì)大多基于工程經(jīng)驗(yàn),不同搭建方式之間難以選擇,缺乏理論指導(dǎo),缺乏統(tǒng)一性設(shè)計(jì)語(yǔ)言。另外網(wǎng)絡(luò)拓?fù)湫阅苤笜?biāo)繁多,不同指標(biāo)之間相互制約,指標(biāo)失衡很難避免。

09網(wǎng)算一體技術(shù),

減少入網(wǎng)次數(shù)提升通信效率

隨著分布式集群規(guī)模的增大,以及單節(jié)點(diǎn)算力的增長(zhǎng),分布式集群系統(tǒng)已經(jīng)逐漸從計(jì)算約束轉(zhuǎn)換為網(wǎng)絡(luò)通信約束。一方面,在過(guò)去 5 年,GPU 算力增長(zhǎng)了近90 倍,而網(wǎng)絡(luò)帶寬僅增長(zhǎng)了 10 倍;另一方面,當(dāng)前的集群系統(tǒng)中,當(dāng) GPU 集群達(dá)到一定規(guī)模以后,即使增加計(jì)算節(jié)點(diǎn)數(shù),但由于分布式集群節(jié)點(diǎn)之間通信代價(jià)的增加,仍可能導(dǎo)致集群每秒訓(xùn)練的圖片數(shù)量不增反減。

10總結(jié)與展望

數(shù)據(jù)中心集合了極其豐富的軟硬件資源,從芯片到服務(wù)器,從存儲(chǔ)設(shè)備到網(wǎng)絡(luò)設(shè)施,從平臺(tái)軟件到應(yīng)用軟件,不一而足。要構(gòu)建強(qiáng)大算力,各類資源需要高度協(xié)同,深度融合。超融合正在成為下一代數(shù)據(jù)中心網(wǎng)絡(luò)架構(gòu)的內(nèi)涵與精髓,政府、金融、運(yùn)營(yíng)商、互聯(lián)網(wǎng)等行業(yè)存在巨大的融合需求。

可以預(yù)見(jiàn),未來(lái)超融合數(shù)據(jù)中心網(wǎng)絡(luò)與垂直行業(yè)的結(jié)合將會(huì)更加緊密。在這個(gè)長(zhǎng)期的探索過(guò)程中,超融合數(shù)據(jù)中心網(wǎng)絡(luò)邁出了堅(jiān)實(shí)的一步。基于總線級(jí)數(shù)據(jù)中心網(wǎng)絡(luò)技術(shù)的超融合數(shù)據(jù)中心打破了異構(gòu)協(xié)議間的屏障,提升數(shù)據(jù)跨資源的流通和處理效率,提高算力能效比。在全國(guó)一體化大數(shù)據(jù)中心建設(shè)的今天,必將為數(shù)據(jù)中心新基建的發(fā)展提供網(wǎng)絡(luò)性能的堅(jiān)實(shí)保障。

審核編輯 :李倩

-

總線

+關(guān)注

關(guān)注

10文章

2869瀏覽量

87995 -

數(shù)據(jù)中心

+關(guān)注

關(guān)注

16文章

4696瀏覽量

71965 -

RDMA

+關(guān)注

關(guān)注

0文章

76瀏覽量

8928

原文標(biāo)題:總線級(jí)數(shù)據(jù)中心網(wǎng)絡(luò)技術(shù)

文章出處:【微信號(hào):算力基建,微信公眾號(hào):算力基建】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

Meta AI數(shù)據(jù)中心網(wǎng)絡(luò)用了哪家的芯片

當(dāng)今數(shù)據(jù)中心新技術(shù)趨勢(shì)

簡(jiǎn)述數(shù)據(jù)中心網(wǎng)絡(luò)架構(gòu)的演變

戴爾科技如何幫助巴克利改造升級(jí)數(shù)據(jù)中心

數(shù)據(jù)中心液冷需求、技術(shù)及實(shí)際應(yīng)用

CXL技術(shù):全面升級(jí)數(shù)據(jù)中心架構(gòu)

數(shù)據(jù)中心加速網(wǎng)絡(luò)技術(shù)優(yōu)勢(shì)與實(shí)施策略

#MPO預(yù)端接 #數(shù)據(jù)中心機(jī)房 #機(jī)房布線

總線級(jí)數(shù)據(jù)中心網(wǎng)絡(luò)技術(shù)

總線級(jí)數(shù)據(jù)中心網(wǎng)絡(luò)技術(shù)

評(píng)論