本文主要闡述了在驅動芯片應用中,半橋中點出現的負壓,分析其原因并且通過實驗如何正確處理。

驅動芯片與VS負壓的產品

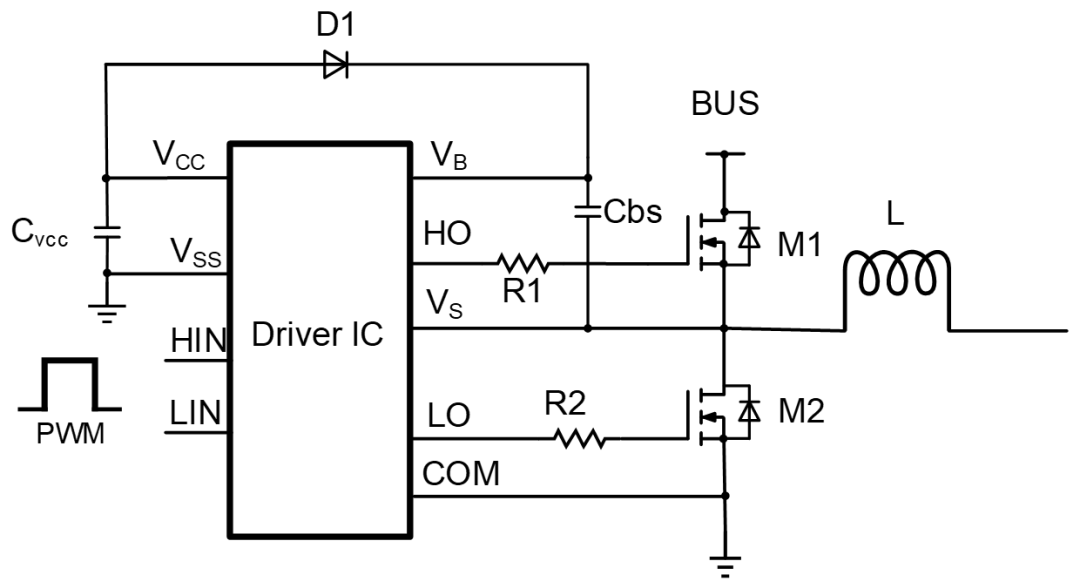

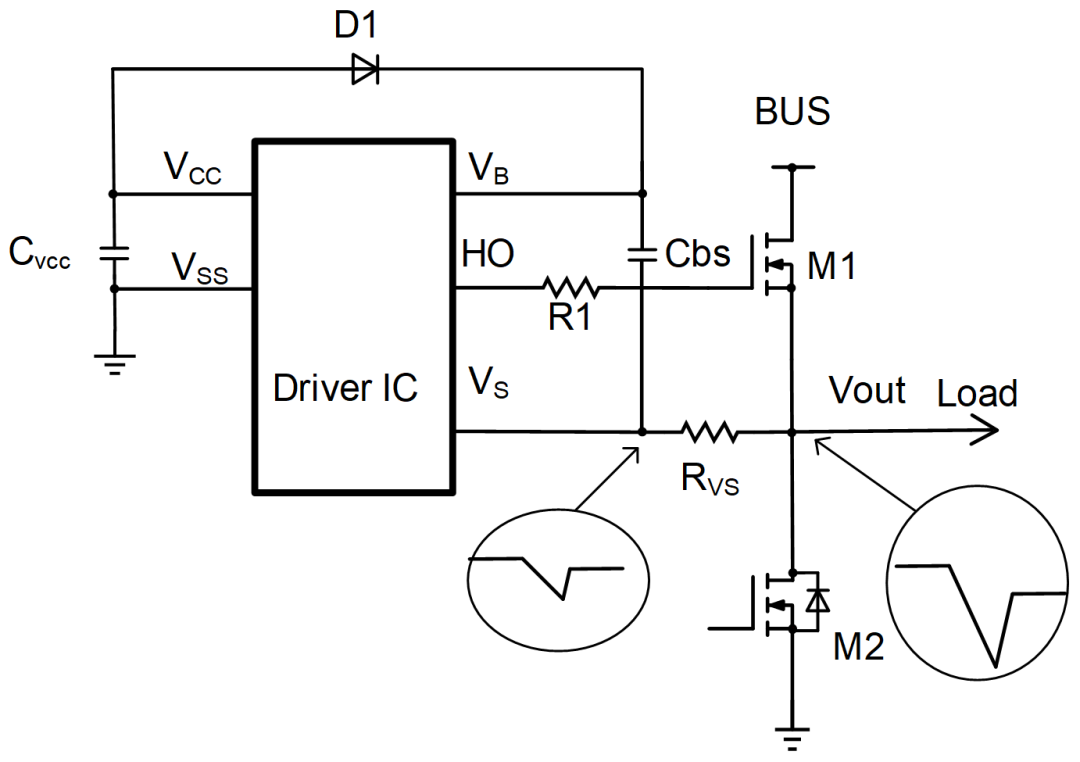

電力電子電路中,橋式電路應用非常廣泛。圖1顯示了一個半橋驅動芯片驅動半橋電路的典型電路示意圖。

圖 1. 理想典型驅動芯片與半橋電路示意圖

基本工作原理如下:當HIN為高時,輸出HO為高,上管M1打開,電流從BUS通過M1流到負載端。當LIN為高時,輸出LO為高,下管M2打開,電流通過M2續流。

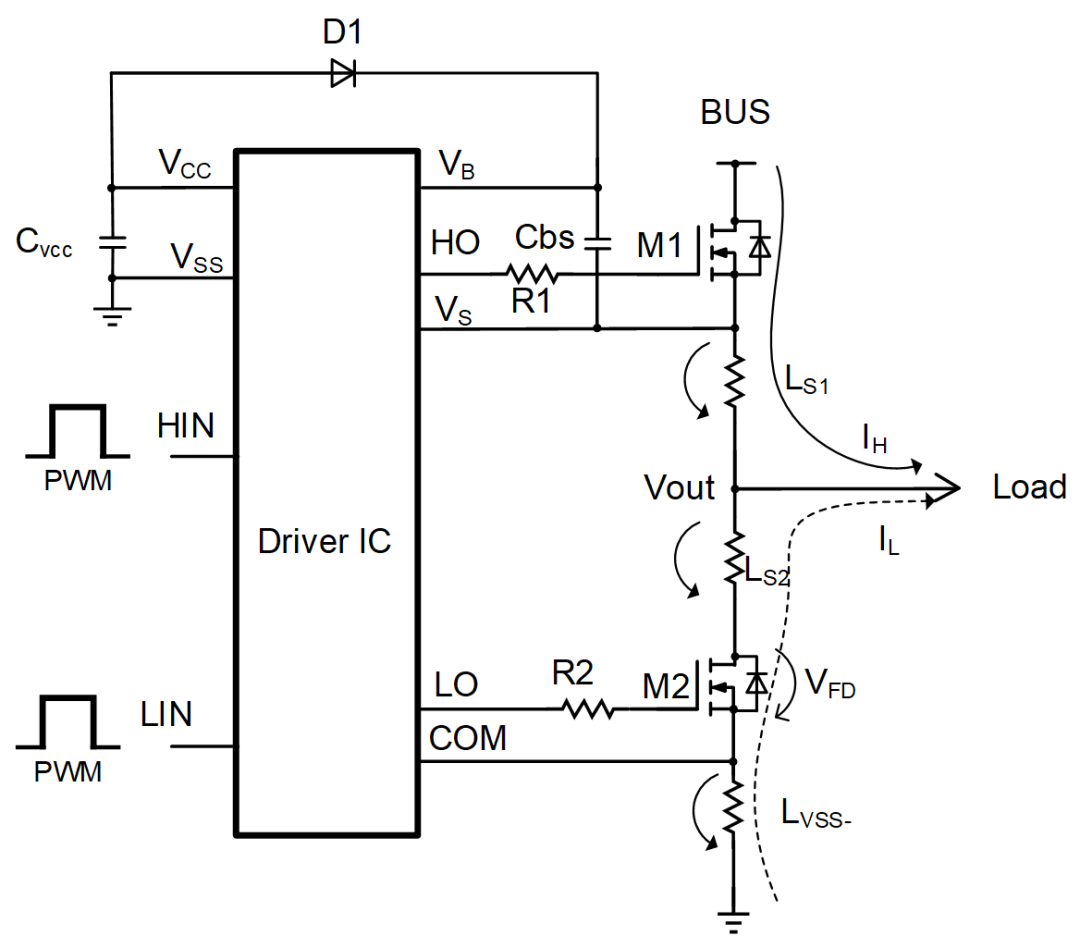

圖 2. 帶寄生電感導致VS電壓低于VSS

由于線路上有寄生電感,在上管關斷,下管開通的瞬態切換過程中,在寄生電感中將產生壓降,導致VS端將產生負壓,如圖 2所示。VS負壓端的大小,可由下述公式表示:

VS-VSS=-VFD-(LVSS-+LS2)×DIL/Dt-LS1×dIH/dt

由上述公式可知,VS的負壓大小主要取決于如下參數:電流變化的斜率,寄生電感的大小。電流變化的斜率越大,尤其是在輸出短路的情況下,VS負壓也越大。寄生電感越大,VS負壓也越大。

-半橋中點負壓及應對策略 -

VS負壓的影響

一般在驅動芯片規格書中規定了最大的VS與VSS(COM)之間的負壓和推薦的工作條件。

由于芯片內部含有寄生的二極管及latch up機制,當VS負壓過大時,會導致芯片損壞或邏輯異常。

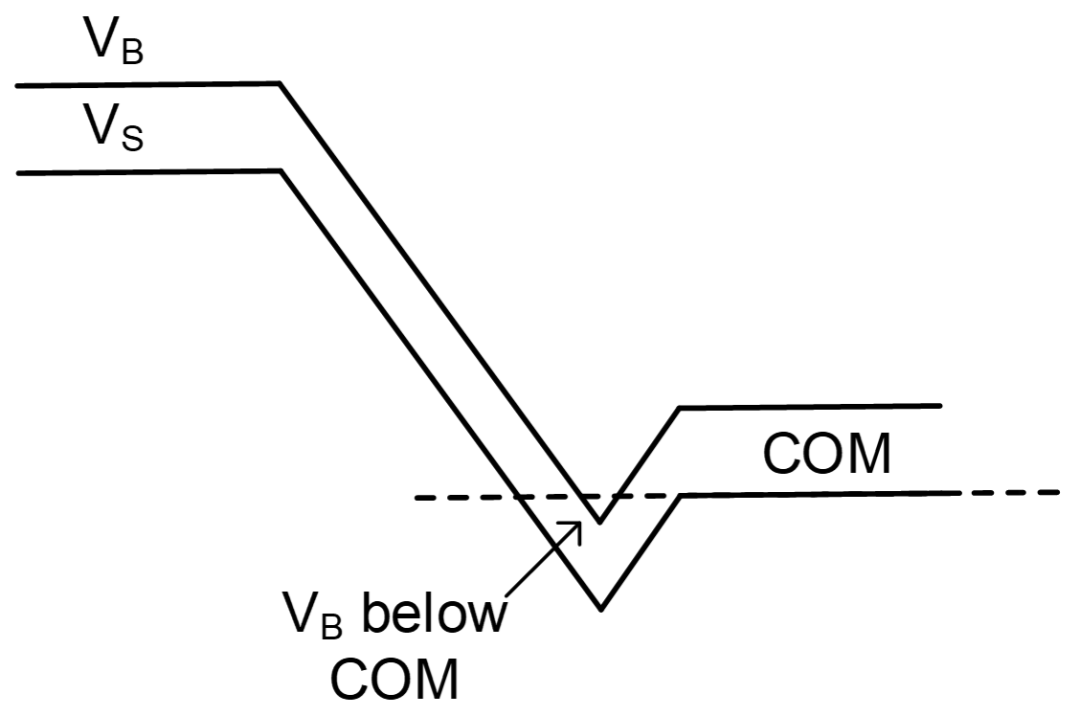

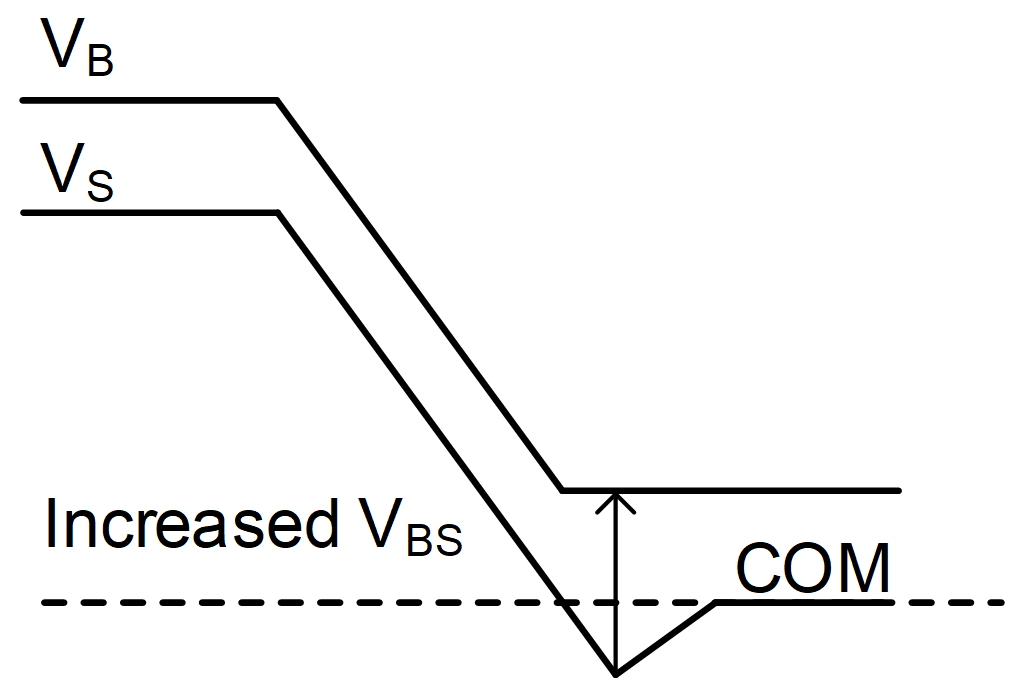

圖 3. 高邊的浮動電源與瞬態負壓值VB,VS波形

如圖3所示,當采用隔離的高邊電源,當VS電壓低于隔離電源Vbs電壓時,導致VB電壓低于COM端時,芯片內部二極管D3存在導通風險。

圖 4. Bootstrap電路與瞬態負壓值VB,VS波形

如圖4所示,當高邊電源采用bootstrap方式時,由于VS瞬間出現負壓,將導致VB到VS的電壓升高,當VBS電壓大于芯片使用的最高值時,芯片也將損壞。VBS為浮動電源,考慮極端情況,上管導通時發生短路,一旦上管關斷,短路大電流將通過下管體二極管。若此時的di/dt將使得VS非常小,VB與VS間電壓超過芯片的使用范圍。

VS負壓幅值過大,有大電流從VS腳流出,會干擾芯片內部襯底,從而干擾內部電路對輸入信號電平的正確判斷,導致輸出信號不受輸入信號控制。

-半橋中點負壓及應對策略 -

VS負壓對應策略

為了降低VS負壓,優化PCB布局降低寄生電感是最有效的。PCB布局可以采用如下一些手段:如上下功率管的擺放盡量靠近;驅動芯片靠近被驅動的功率管以減少驅動芯片地到功率器件地。

另外一個途徑是降低di/dt值。比較簡單的辦法是增大關斷電阻R1,但以此同時,需要考慮可能會帶來效率低下的問題。

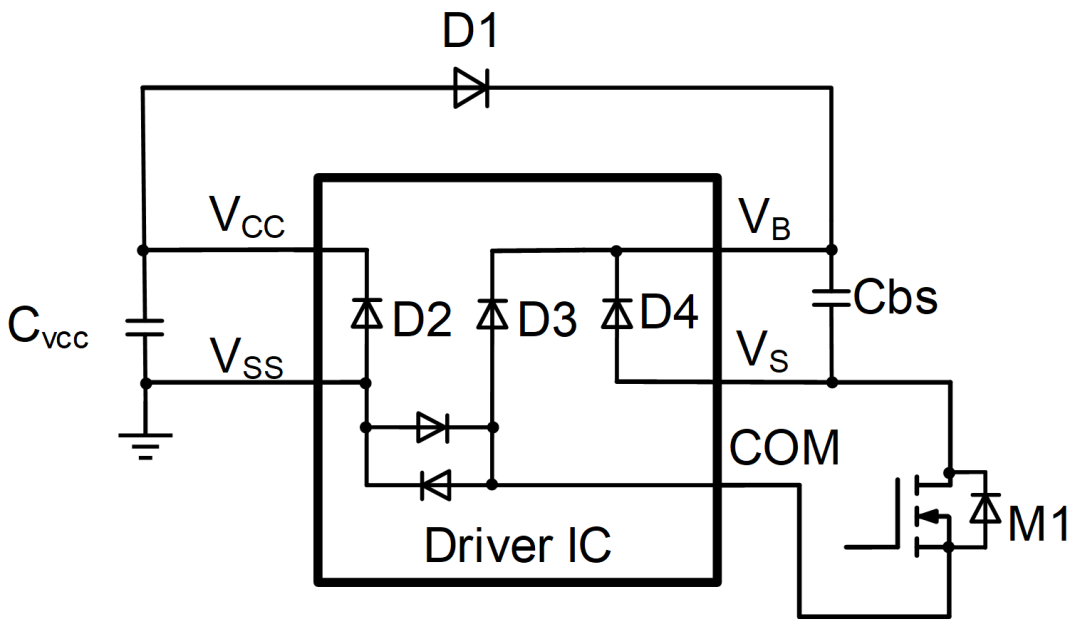

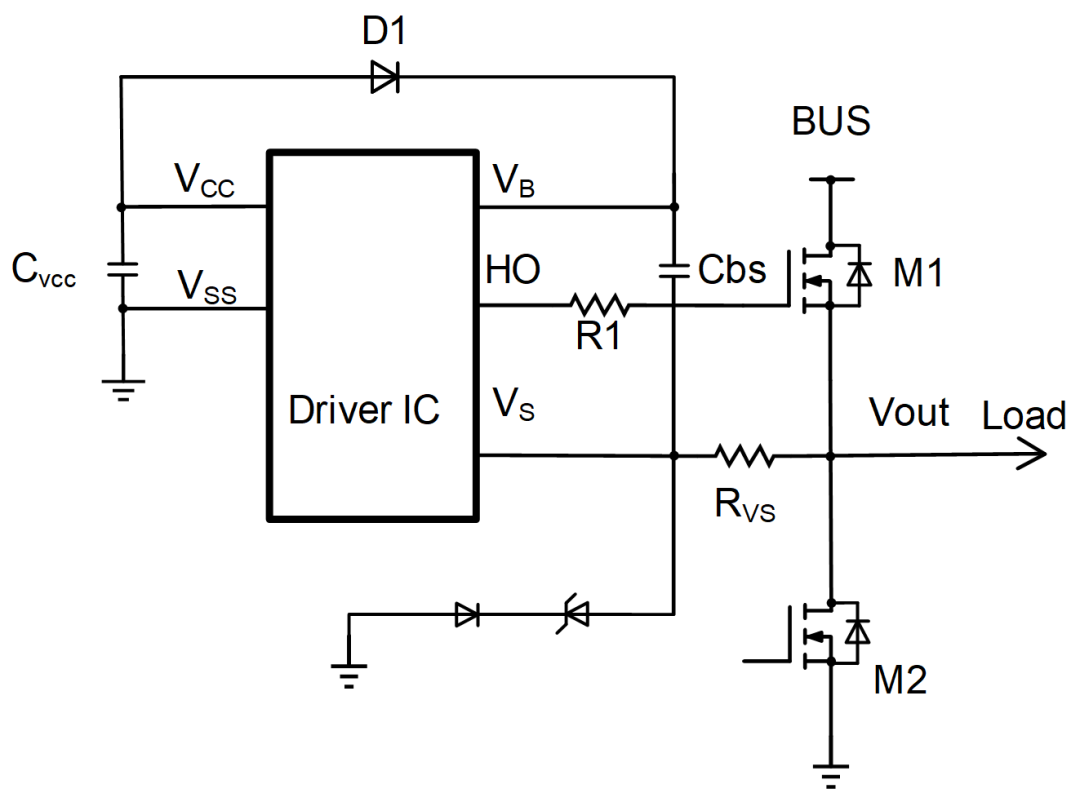

圖 5. Rvs連接電路

圖 6. VS端增加反向二極管和穩壓管

為了使得VB與VS間的電壓差小于VBS_ABSMAX,推薦在VS與VSS間加入一個穩壓管與高壓二極管串聯。VB-VS≤VBS_ABSMAX,則穩壓管耐壓值選擇需考慮:VZ≤VBS_ABSMAX-VCC。

-半橋中點負壓及應對策略 -

SLM2304S實驗測試

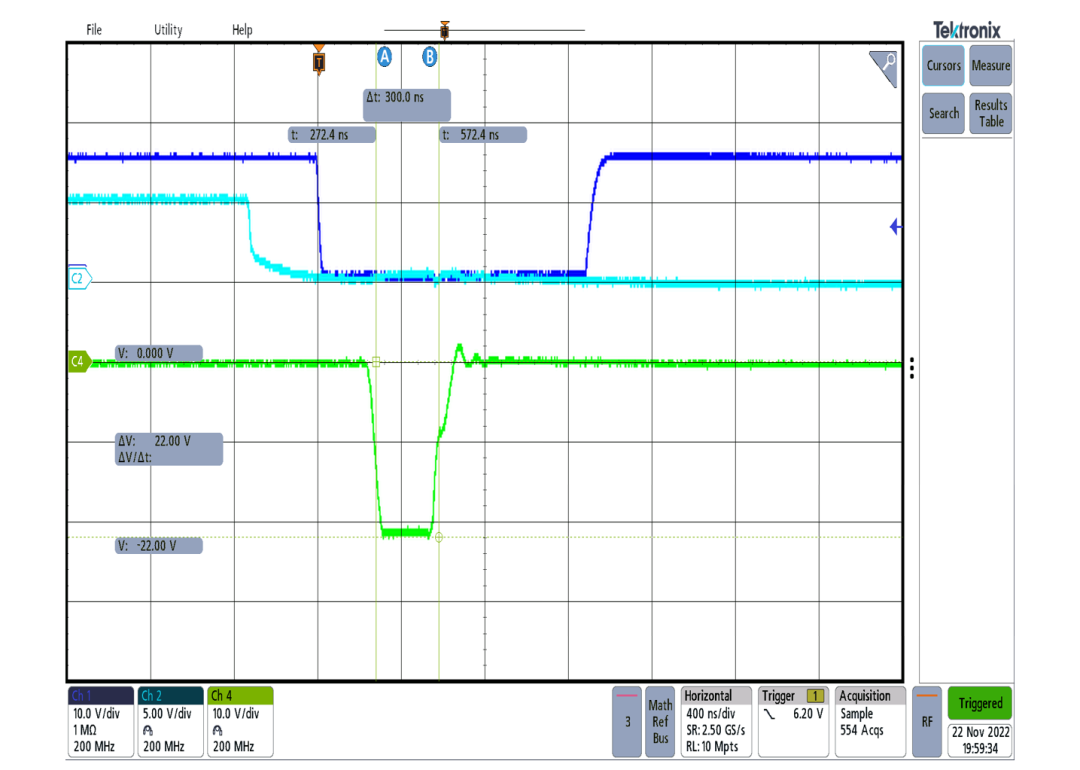

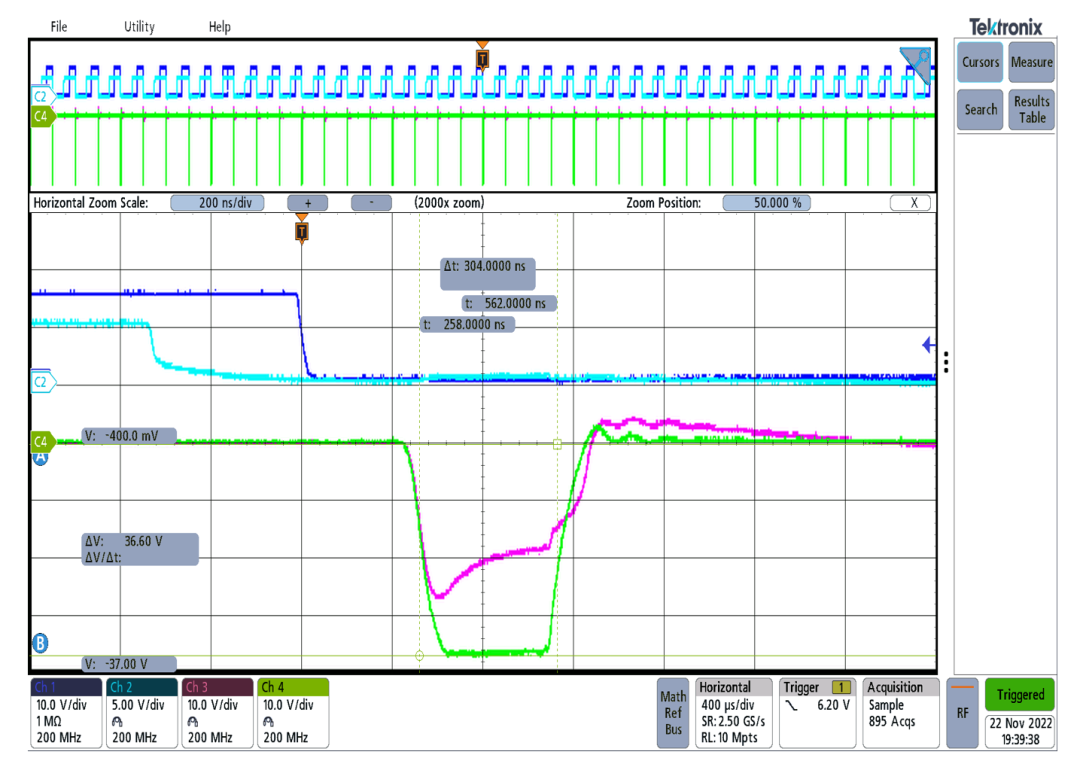

SLM2304S負壓測試波形

圖 7. SLM2304S VS 端沒有串聯電阻

-22V 300ns 負壓波形

CH1: HO 丨CH2: HIN 丨CH4: VS

圖 8. SLM2304S 串聯電阻Rvs=10ohm

-37V 300ns 負壓波形

CH1: HO 丨CH2: HIN

CH3: 芯片端VS 丨CH4: 半橋中點VS

從圖7,圖8對比可看出,VS端未串聯電阻,在300ns,負壓22V就出現了波形異常,而VS端串聯了10Ω電阻,負壓達到了37V才出現異常。另外如圖8所示,在半橋中點 有37V的負壓,而芯片端的VS電壓最大值只存在了20V附近,大大降低了芯片端的負壓值;從而有效的抑制了外部負壓的數值,相當于提高了芯片的耐負壓能力。

-半橋中點負壓及應對策略 -

測試總結

VS的負壓大小與持續時間關系到驅動芯片的安全、正常工作。瞬態負壓的大小主要取決于寄生電感,電流變化的速率。通過對外圍電路的有效設計,可以增強驅動芯片在系統中對負壓的耐受能力,使其能在惡劣工況中安全工作。

審核編輯:湯梓紅

-

半橋

+關注

關注

3文章

44瀏覽量

21362 -

驅動芯片

+關注

關注

13文章

1257瀏覽量

54448 -

半橋電路

+關注

關注

3文章

29瀏覽量

25749 -

vs

+關注

關注

0文章

14瀏覽量

12468

原文標題:應用筆記 丨 半橋中點負壓及應對策略

文章出處:【微信號:數明半導體,微信公眾號:數明半導體】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

應用筆記|半橋中點負壓及應對策略

應用筆記|半橋中點負壓及應對策略

評論