設計高速板是嵌入式應用的重要組成部分。如今,印刷電路板(PCB)的設計方式應自動滿足高級解決方案的要求。這就是高速高頻PCB設計成為硬件工程師重要課題的最大原因.

正確的硬件設計方法正成為產品設計服務能力的必要條件,以實現產品公司定義的項目時間表和成本。在設計具有PCI Express、SATA和LPDDR4等接口的高速電路板時,如果沒有深入的高速設計知識和經驗,實現第一個正確的可靠設計更具挑戰性。

當我們談論高速電路板設計時,從架構設計開始,在硬件設計生命周期中有許多領域需要研究,例如組件選擇、接口時序和直流特性分析、原理圖設計、所需的堆疊設計、布局設計、SI 分析、PI 分析等等。為了突出高速設計實踐,下面我們詳細討論了最初的兩個重要步驟:

樓層規劃策略

平面規劃是一個可視化圖表,可視化了電路板上所有互連子部分的位置。沒有適當布局規劃的布局布線可能會導致PCB尺寸增加、寄生效應、布線擁塞、EMI問題、層疊中層數要求更多等。通常,幾乎擁有布局規劃,用于估算PCB尺寸,隔離PCB上的模擬數字RF子部分,并根據產品外殼設計最終確定機電組件的放置。

高速電路板設計需要第二級平面規劃,以避免PCB布局期間的返工以及后期設計的時間和成本增加。放置互連模塊的良好做法之一是將PCB空間劃分為多個塊,然后根據驅動器和接收器或收發器之間盡可能短的互連來決定互連模塊最適合哪個塊。這將有助于確定PCB堆疊中的布線方向和所需層。

讓我們了解在電路板上優化放置的重要參數:

為高速電路板選擇小型封裝尺寸元件,以減少高速傳輸線路上的阻抗失配和寄生效應、電感和電容。請注意,較小的組件包可能存在良率問題。根據裝配供應商的能力咨詢他們來做出決定

從高引腳數元件和機電連接器開始放置

將組件分組為邏輯子部分,并按照組件或邏輯子部分放置的示意圖邏輯流程進行操作

印刷電路板層堆疊

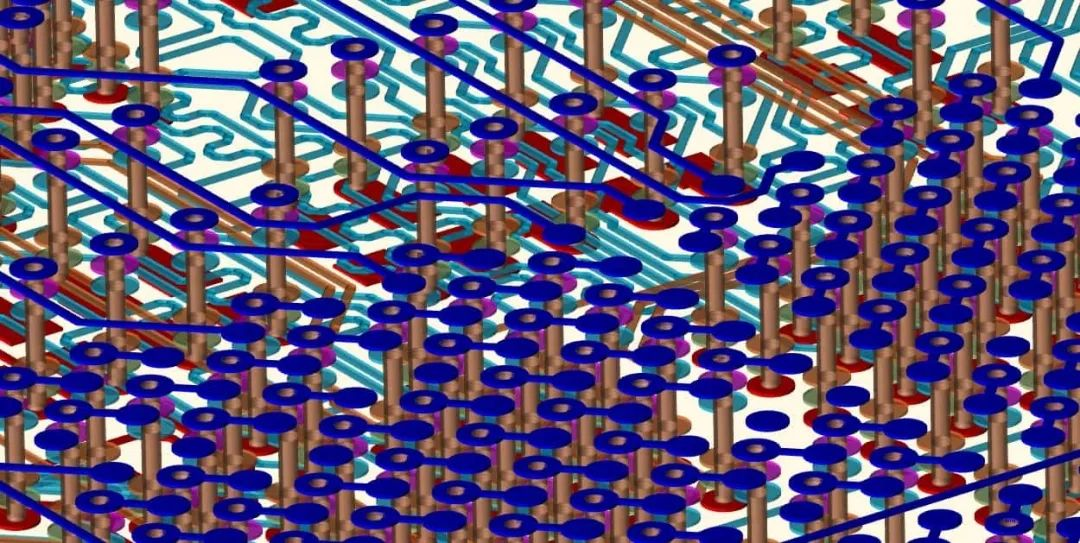

它是導電層和絕緣層一個接一個的排列,以便在布局設計之前制作PCB結構.PCB堆疊在高速電路板設計中很重要。定義良好的層疊有助于最大限度地減少EMI輻射并提高PCB的電磁兼容性。此外,它還有助于增強信號完整性、設計的電源完整性、不受外部噪聲影響,并降低制造成本。

定義電路板層堆疊的三個重要步驟:

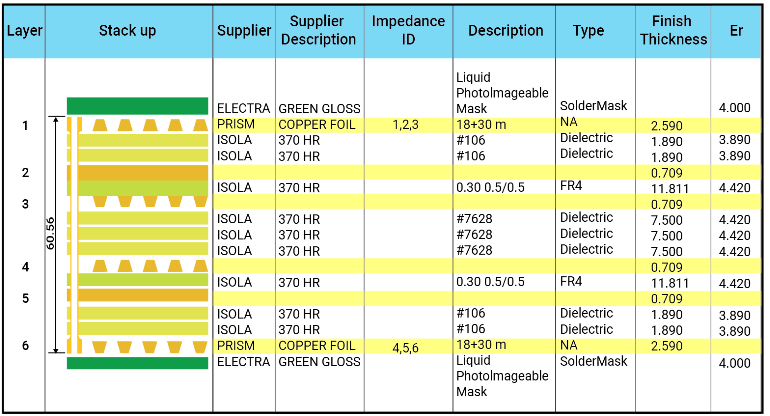

確定所需的層數:信號層取決于信號完整性要求,如低串擾、低間距元件、高引腳數元件(如BGA)、固定PCB尺寸等。電源和接地層數取決于高速設計中的配電、低 EMI 和信號返回路徑要求,從而降低電源軌中的直流壓降并提高電源完整性。

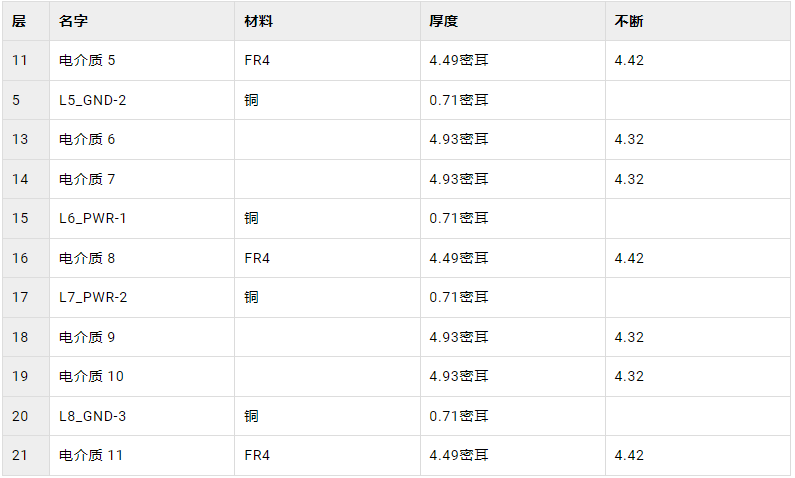

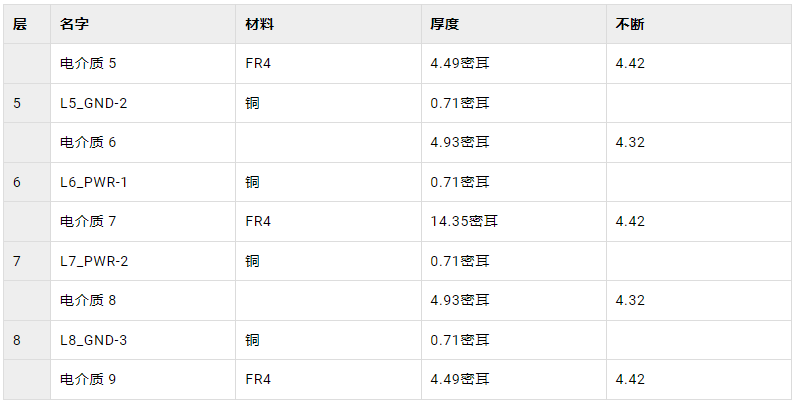

層疊中的層排列:一旦確定了信號、電源和接地層的數量,下一步就是按順序排列它們。在層疊安排中,我們需要遵循的一些規則如下:

電源層和接地層應彼此靠近,以獲得良好的規劃間電容

避免兩個相鄰的信號層。如果不可能,請確保信號層與參考接地層之間的預浸料厚度較低,兩個信號層之間的芯層厚度較高,如下圖所示

從中心到頂部和底部建立對稱或平衡的堆疊

在堆疊中添加可能的接地層,以減少高速信號的共模輻射

確定材料類型:PCB由四種不同類型的材料組成, 即絲網印刷材料, 阻焊材料, 銅, 和基板.影響高速設計參數(如阻抗和信號完整性)的基板材料在大多數常見應用中是FR4。由于快速時鐘速率和數據傳輸,高速電路板組件比普通電路板散發更多的熱量,數據傳輸也會傳導到PCB。設計人員可以選擇中等或高Tg,玻璃化轉變溫度,FR4材料,以實現長期運行可靠性。Tg是PCB基板開始變得機械不穩定的溫度。FR4 適用于時鐘速率為 <5GHz 的應用。超過5GHz的高速板需要使用其他材料,如Nelco和Megtron。對于56GHz以上的頻率,微波頻率需要Rozer材料用于堆疊

在定義了層堆疊之后, 現在設計人員應該開始讓他們的PCB制造商或合同制造商參與進來,根據材料的可用性, 基板厚度, 和所需的信號阻抗, 獲得實際可能的堆疊.為了達到所需的阻抗, PCB制造商在PCB制造過程中調整堆疊的介電厚度.可以與制造商核實,并確保在制造過程中驗證的阻抗在單端和差分信號的容差范圍內。

-

pcb

+關注

關注

4317文章

23010瀏覽量

396357 -

嵌入式

+關注

關注

5069文章

19021瀏覽量

303396 -

接口

+關注

關注

33文章

8504瀏覽量

150844

發布評論請先 登錄

相關推薦

印刷電路板設計對SIMPLE SWITCHER?電源模塊熱性能的影響

晶體和振蕩器印刷電路板設計注意事項

印度對原產于中國內地和香港的印刷電路板征收反傾銷稅

pcb電路板設計軟件哪個好 PCB電路板設計一般用sw嗎

集成電路板和pcb的區別

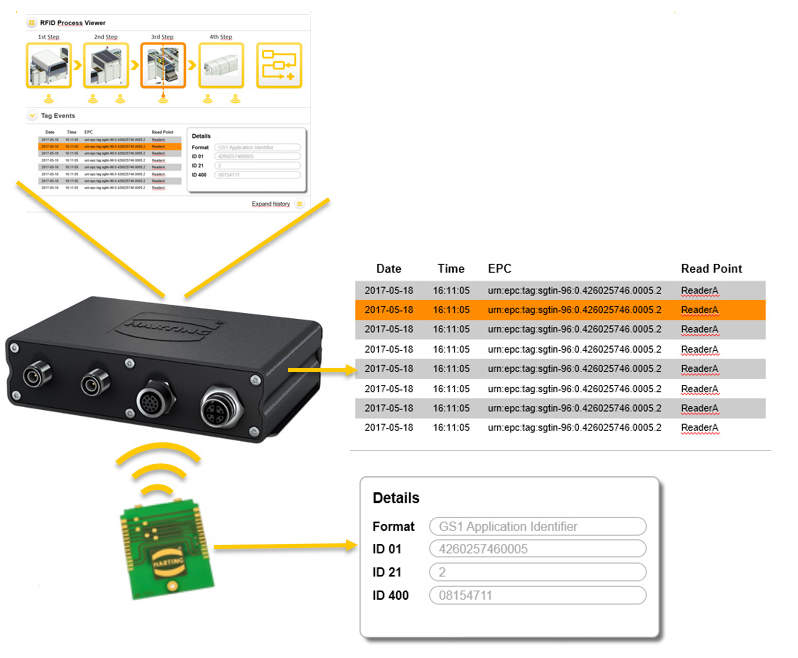

SMT生產線利用RFID檢測印刷電路板(PCB)

印刷電路板的起源和演變

設計高速印刷電路板的最佳實踐

設計高速印刷電路板的最佳實踐

評論