電子發燒友網報道(文/周凱揚)到了3nm這個工藝節點之后,單靠現有的0.33NA EUV光刻機就很難維系下去了。為了實現2nm乃至未來的埃米級工藝,將晶體管密度推向1000MTr/mm2,全面投入使用高NA EUV光刻機已經勢在必行了。據了解,一臺高NA EUV的光刻機成本就可能達到3.2億美元,這樣一個天價的光刻系統究竟能帶來哪些優勢,又存在哪些挑戰呢?

規模和密度的平衡,我們為什么需要高NA光刻機?

從今年發布的不少新品來看,即便工藝沒有太大的變化,芯片的性能仍在穩步提升,有的是從架構上找到了創新,有的選擇了改善帶寬之類的性能。但我們也都能看出,其中有一部分產品選擇了走大規模的路線,比如蘋果的M1 Ultra。這種方式雖然增加了功耗,但對于那些對功耗并不敏感的產品來說,似乎也是可行的一種思路,那么我們真的有必要用到更貴的高NA EUV光刻機進一步提升密度嗎?

這個問題的答案其實不言而喻了,英特爾、臺積電等晶圓廠提前預訂的高NA EUV光刻機訂單已經證明了它的重要性。歸根結底還是我們的晶體管密度需求仍在不斷攀升,但我們需要明白這個需求并不是線性增長的。

新世紀的20年代,很可能成為深度技術發展的黃金十年,比如邊緣AI芯片、基于CMOS的NIR/SWIR成像器、光電集成的片上激光雷達等等。你可以說推動工藝發展最大的功臣是智能手機芯片,但其他應用對高密度的需求同樣不可小覷,因為這對它們來說也就意味著更高的存儲容量和帶寬、更高的算力。

如今的深度學習在大規模模型的爆發下,所需算力每幾個月就會翻一番,但現在能效比已經成了優先級更高的指標,要想同時滿足性能和算力的話,主要方法有四種:一是換一種系統級計算架構,比如DSA架構;二是充分利用3D設計,也就是我們常說的3D封裝和堆疊技術;三是從晶體管架構上創新,譬如納米管、納米片、CFET和原子溝道等;第四個則是目前看來最快捷的一條路線,通過光刻技術的發展直接提升密度。

高NA光刻機帶來的優勢

固然高NA EUV光刻機能夠讓我們挺進下一工藝節點,但它帶來的好處并不只是增加晶體管密度。先從技術價值上來說,0.55的大數值孔徑與0.33相比,可以實現尺寸減小2/5的特征圖形,將密度提升2.9倍。其次,高NA EUV光刻機帶來了更高的成像對比度,從而極大改善線寬均勻性,在更少的光刻膠劑量下實現更少的條紋變化。

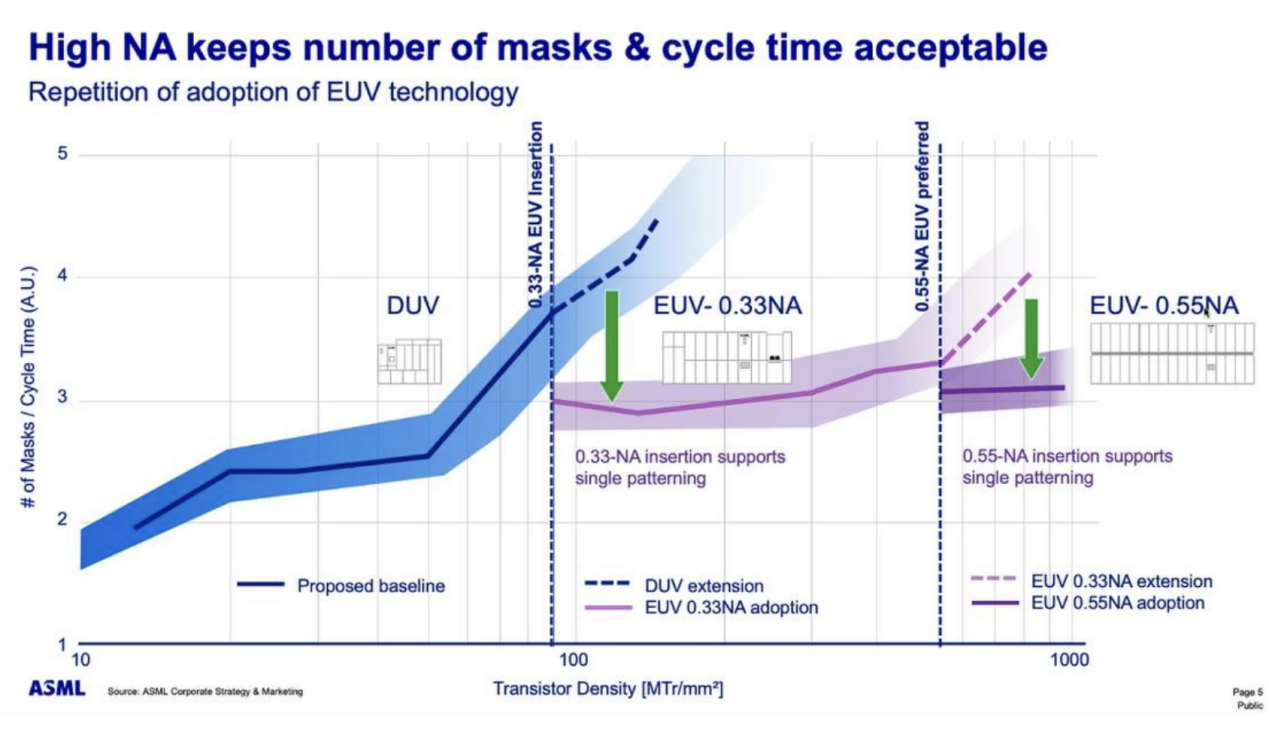

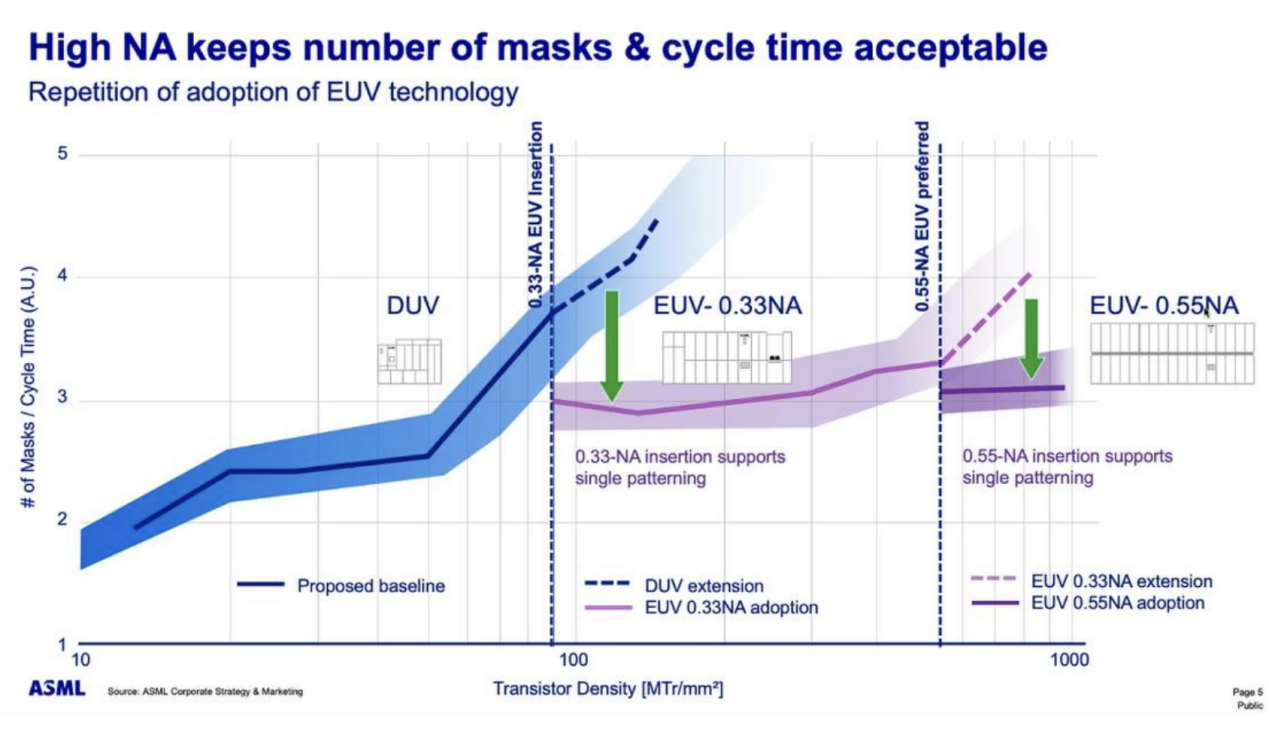

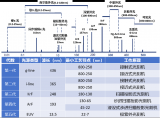

光刻機晶體管密度的變化趨勢 / ASML

對于使用光刻機的晶圓廠來說,以上的優勢減少了多重光刻的需要,也減少了光刻膠的劑量使用,從而降低了整體成本。其次,由于工序的簡化,曝光后光刻膠圖形邊緣與設計圖形之間的邊緣放置誤差也一并減少了。這也一并導致了掩膜處理周期的減少,極大提高整個晶圓廠的運轉效率。

有突破就有挑戰

既然高NA EUV光刻機有這么多好處,ASML為何還不加快進度將其造出來,而是要等到2024年才能出貨呢?答案是目前看來,這類光刻機的制造和應用都面臨著不小的挑戰,以至于在2025年大規模投入都存在一定阻礙。

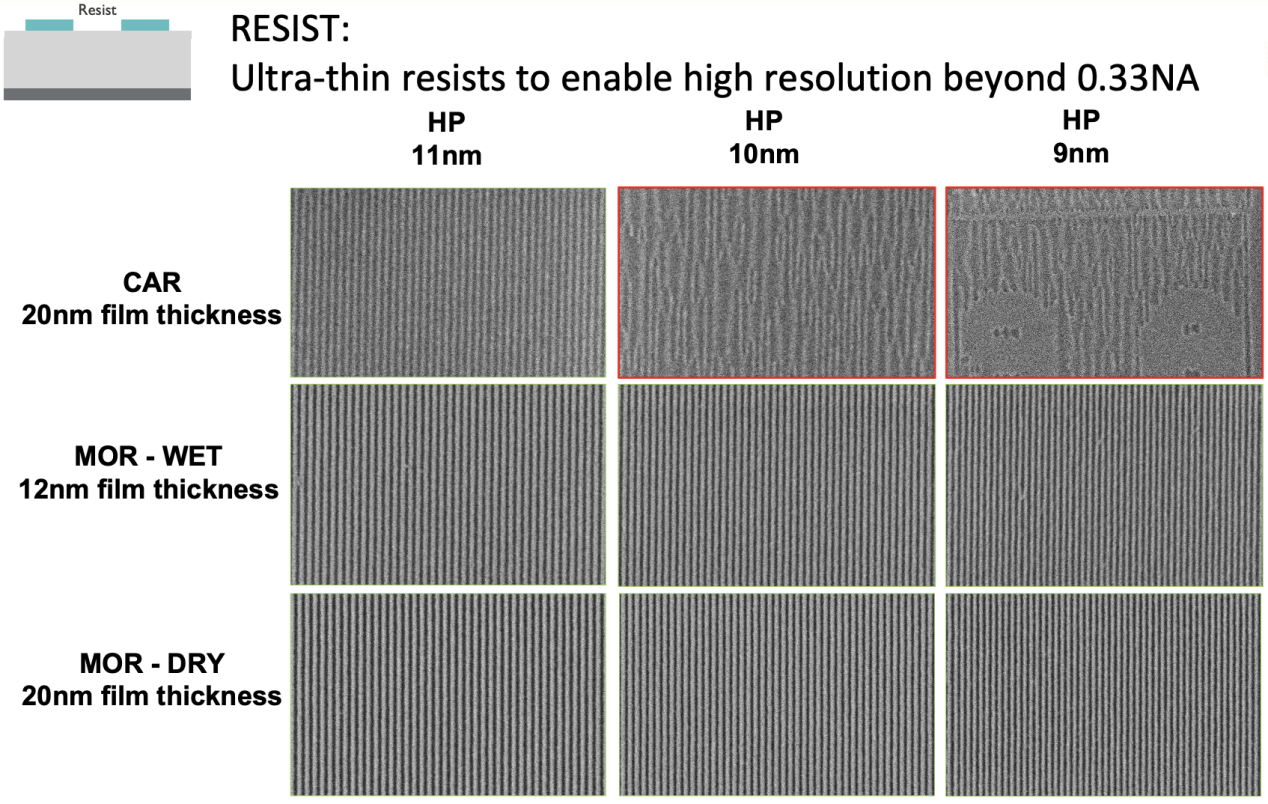

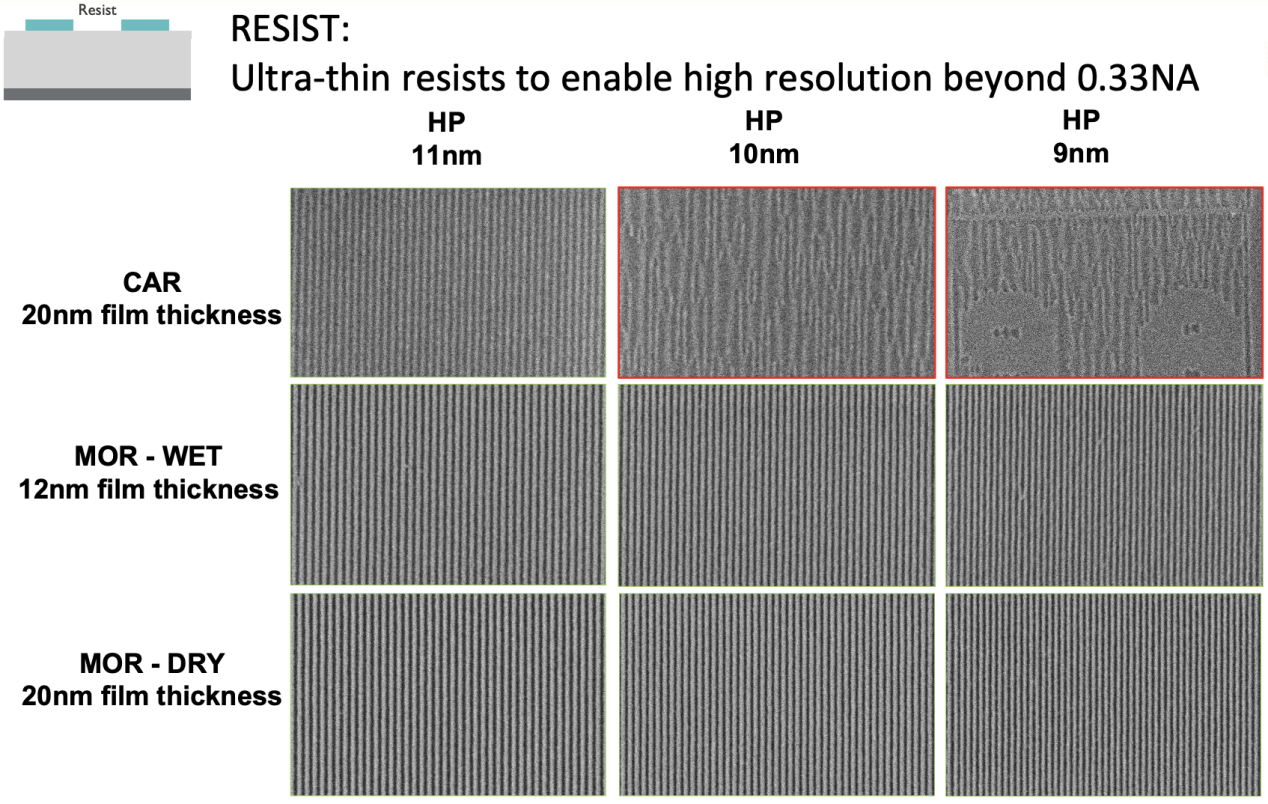

0.33NA之后所需的光刻膠厚度 / IMEC

我們先從光刻膠說起,高NA EUV光刻機需要用到更薄的光刻膠,比如小于20nm,這樣才能維持2:1這一理想的線高寬比。否則因為更大的厚度,就會超過這一比例,在曝光階段容易因為重心變化引發光刻膠塌陷。除了需要超薄、超高分辨率的光刻膠,還要考慮引入的隨機效應,這種隨機效應會導致不必要的失效和特征圖形粗糙度,從而影響到芯片的性能,甚至可能會使整個系統失效。

再者就是高NA EUV光刻機需要用到的新光掩膜,光掩膜對于芯片的制造來說至關重要,因為它的明暗區域內保存著設備成品所需的設計布局信息。隨著特征圖形尺寸的減小,與理想光掩膜之間的偏差對最終晶圓圖案的影響也在增加。

為禍作亂者之一就是光掩膜的3D效應,比如EUV中,光線以6°的入射角擊中光掩膜,以此產生的反射可能會產生屏蔽,從而因為光掩膜的緣故在晶圓上產生成像誤差。所以必須開發新的變形光掩膜技術及規范,才能減輕3D效應帶來的影響。

小結

在更高的芯片性能需求下,轉向高NA的EUV光刻機已是必然,這類光刻系統也能徹底釋放現代晶體管結構創新的潛力,引領我們走向埃米時代。但我們也不能就此忘記剛引入EUV光刻機時的教訓,3年后ASML的高NA EUV實現高密度已經是定數,但良率和產量問題才是這套系統交付后最大的問題。

規模和密度的平衡,我們為什么需要高NA光刻機?

從今年發布的不少新品來看,即便工藝沒有太大的變化,芯片的性能仍在穩步提升,有的是從架構上找到了創新,有的選擇了改善帶寬之類的性能。但我們也都能看出,其中有一部分產品選擇了走大規模的路線,比如蘋果的M1 Ultra。這種方式雖然增加了功耗,但對于那些對功耗并不敏感的產品來說,似乎也是可行的一種思路,那么我們真的有必要用到更貴的高NA EUV光刻機進一步提升密度嗎?

這個問題的答案其實不言而喻了,英特爾、臺積電等晶圓廠提前預訂的高NA EUV光刻機訂單已經證明了它的重要性。歸根結底還是我們的晶體管密度需求仍在不斷攀升,但我們需要明白這個需求并不是線性增長的。

新世紀的20年代,很可能成為深度技術發展的黃金十年,比如邊緣AI芯片、基于CMOS的NIR/SWIR成像器、光電集成的片上激光雷達等等。你可以說推動工藝發展最大的功臣是智能手機芯片,但其他應用對高密度的需求同樣不可小覷,因為這對它們來說也就意味著更高的存儲容量和帶寬、更高的算力。

如今的深度學習在大規模模型的爆發下,所需算力每幾個月就會翻一番,但現在能效比已經成了優先級更高的指標,要想同時滿足性能和算力的話,主要方法有四種:一是換一種系統級計算架構,比如DSA架構;二是充分利用3D設計,也就是我們常說的3D封裝和堆疊技術;三是從晶體管架構上創新,譬如納米管、納米片、CFET和原子溝道等;第四個則是目前看來最快捷的一條路線,通過光刻技術的發展直接提升密度。

高NA光刻機帶來的優勢

固然高NA EUV光刻機能夠讓我們挺進下一工藝節點,但它帶來的好處并不只是增加晶體管密度。先從技術價值上來說,0.55的大數值孔徑與0.33相比,可以實現尺寸減小2/5的特征圖形,將密度提升2.9倍。其次,高NA EUV光刻機帶來了更高的成像對比度,從而極大改善線寬均勻性,在更少的光刻膠劑量下實現更少的條紋變化。

光刻機晶體管密度的變化趨勢 / ASML

對于使用光刻機的晶圓廠來說,以上的優勢減少了多重光刻的需要,也減少了光刻膠的劑量使用,從而降低了整體成本。其次,由于工序的簡化,曝光后光刻膠圖形邊緣與設計圖形之間的邊緣放置誤差也一并減少了。這也一并導致了掩膜處理周期的減少,極大提高整個晶圓廠的運轉效率。

有突破就有挑戰

既然高NA EUV光刻機有這么多好處,ASML為何還不加快進度將其造出來,而是要等到2024年才能出貨呢?答案是目前看來,這類光刻機的制造和應用都面臨著不小的挑戰,以至于在2025年大規模投入都存在一定阻礙。

0.33NA之后所需的光刻膠厚度 / IMEC

我們先從光刻膠說起,高NA EUV光刻機需要用到更薄的光刻膠,比如小于20nm,這樣才能維持2:1這一理想的線高寬比。否則因為更大的厚度,就會超過這一比例,在曝光階段容易因為重心變化引發光刻膠塌陷。除了需要超薄、超高分辨率的光刻膠,還要考慮引入的隨機效應,這種隨機效應會導致不必要的失效和特征圖形粗糙度,從而影響到芯片的性能,甚至可能會使整個系統失效。

再者就是高NA EUV光刻機需要用到的新光掩膜,光掩膜對于芯片的制造來說至關重要,因為它的明暗區域內保存著設備成品所需的設計布局信息。隨著特征圖形尺寸的減小,與理想光掩膜之間的偏差對最終晶圓圖案的影響也在增加。

為禍作亂者之一就是光掩膜的3D效應,比如EUV中,光線以6°的入射角擊中光掩膜,以此產生的反射可能會產生屏蔽,從而因為光掩膜的緣故在晶圓上產生成像誤差。所以必須開發新的變形光掩膜技術及規范,才能減輕3D效應帶來的影響。

小結

在更高的芯片性能需求下,轉向高NA的EUV光刻機已是必然,這類光刻系統也能徹底釋放現代晶體管結構創新的潛力,引領我們走向埃米時代。但我們也不能就此忘記剛引入EUV光刻機時的教訓,3年后ASML的高NA EUV實現高密度已經是定數,但良率和產量問題才是這套系統交付后最大的問題。

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

光刻機

+關注

關注

31文章

1136瀏覽量

46894 -

EUV

+關注

關注

8文章

600瀏覽量

85847

發布評論請先 登錄

相關推薦

ASML擬于2030年推出Hyper-NA EUV光刻機,將芯片密度限制再縮小

ASML再度宣布新光刻機計劃。據報道,ASML預計2030年推出的Hyper-NA極紫外光機(EUV),將縮小最高電晶體密度芯片的設計限制。

Rapidus對首代工藝中0.33NA EUV解決方案表示滿意,未采用高NA EUV光刻機

在全球四大先進制程代工巨頭(包括臺積電、三星電子、英特爾以及Rapidus)中,只有英特爾明確表示將使用High NA EUV光刻機進行大規模生產。

買臺積電都嫌貴的光刻機,大力推玻璃基板,英特爾代工的野心和危機

電子發燒友網報道(文/吳子鵬)此前,臺積電高級副總裁張曉強在技術研討會上表示,“ASML最新的高數值孔徑極紫外光刻機(high-NA EUV)價格實在太高了,臺積電目前的極紫外設備(

ASML考慮推出通用EUV光刻平臺

范登布林克指出,更高的數值孔徑能提高光刻分辨率。他進一步解釋說,Hyper NA 光刻機將簡化先進制程生產流程,避免因使用 High NA 光刻機

臺積電A16制程采用EUV光刻機,2026年下半年量產

據臺灣業內人士透露,臺積電并未為A16制程配備高數值孔徑(High-NA)EUV光刻機,而選擇利用現有的EUV

臺積電張曉強:ASML High-NA EUV成本效益是關鍵

據今年2月份報道,荷蘭半導體制造設備巨頭ASML公布了High-NA Twinscan EXE光刻機的售價,高達3.5億歐元(約合27.16億元人民幣)。而現有EUV光刻機的價格則為1

臺積電未確定是否采購阿斯麥高數值孔徑極紫外光刻機

盡管High NA EUV光刻機有望使芯片設計尺寸縮減達三分之二,但芯片制造商需要權衡利弊,考慮其高昂的成本及ASML老款設備的可靠性問題。

ASML發貨第二臺High NA EUV光刻機,已成功印刷10nm線寬圖案

ASML公司近日宣布發貨了第二臺High NA EUV光刻機,并且已成功印刷出10納米線寬圖案,這一重大突破標志著半導體制造領域的技術革新向前邁進了一大步。

英特爾突破技術壁壘:首臺商用High NA EUV光刻機成功組裝

英特爾的研發團隊正致力于對這臺先進的ASML TWINSCAN EXE:5000 High NA EUV光刻機進行細致的校準工作,以確保其能夠順利融入未來的生產線。

阿斯麥(ASML)公司首臺高數值孔徑EUV光刻機實現突破性成果

)光刻機,并已經成功印刷出首批圖案。這一重要成就,不僅標志著ASML公司技術創新的新高度,也為全球半導體制造行業的發展帶來了新的契機。目前,全球僅有兩臺高數值孔徑EUV

光刻機的發展歷程及工藝流程

光刻機經歷了5代產品發展,每次改進和創新都顯著提升了光刻機所能實現的最小工藝節點。按照使用光源依次從g-line、i-line發展到KrF、ArF和EUV;按照工作原理依次從接觸接近式

發表于 03-21 11:31

?4796次閱讀

ASML 首臺新款 EUV 光刻機 Twinscan NXE:3800E 完成安裝

3 月 13 日消息,光刻機制造商 ASML 宣布其首臺新款 EUV 光刻機 Twinscan NXE:3800E 已完成安裝,新機型將帶來更高的生產效率。 ▲ ASML 在 X 平臺

英特爾成為全球首家購買3.8億美元高數值孔徑光刻機的廠商

英特爾最近因決定從荷蘭 ASML 購買世界上第一臺高數值孔徑(High-NA)光刻機而成為新聞焦點。到目前為止,英特爾是全球唯一一家訂購此類光刻機的晶圓廠,據報道它們的售價約為3.8億

英特爾搶下6種ASML HIGH NA光刻機

如果我們假設光刻機成本為 3.5 億至 4 億美元,并且 2024 年 10 個光刻機的HIGH NA 銷售額將在 35億至40億美元之間。

日本的EUV***引進之路

電子發燒友網報道(文/周凱揚)隨著歐美韓等國家均已引進EUV光刻機,為其晶圓代工廠提供最先進的工藝支持,日本雖然半導體制造水平這些年來提升不大,卻也計劃引進EUV

密度提升近3倍,高NA EUV光刻機有何玄機

密度提升近3倍,高NA EUV光刻機有何玄機

評論