SiP 產(chǎn)品從設(shè)計(jì)到封裝

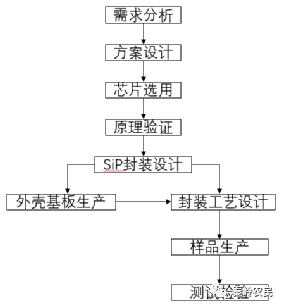

微系統(tǒng)產(chǎn)品的實(shí)現(xiàn)框圖如圖2.25所示,首先進(jìn)行需求的分析,根據(jù)需求情況采用SiP技術(shù)對(duì)由裸芯片組成的微系統(tǒng)進(jìn)行設(shè)計(jì),根據(jù)SiP設(shè)計(jì)文件輸出生產(chǎn)文件,投產(chǎn)陶瓷外殼,最后進(jìn)行封裝和組裝工藝。

圖2.25 SiP微系統(tǒng)封裝設(shè)計(jì)驗(yàn)證過程

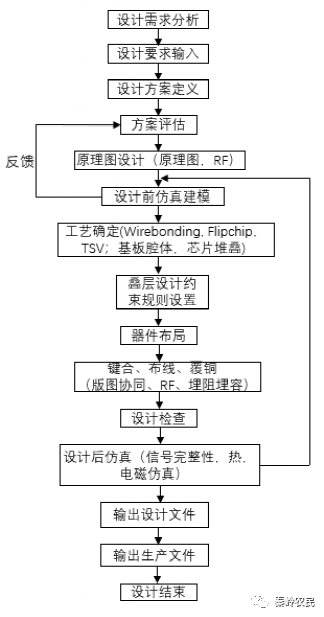

為了確保SiP項(xiàng)目能夠取得成功,遵循嚴(yán)格而規(guī)范的設(shè)計(jì)流程是必不可少的。一款高密度系統(tǒng)級(jí)封裝產(chǎn)品的設(shè)計(jì)往往需要在芯片布局、封裝結(jié)構(gòu)設(shè)計(jì)、基板設(shè)計(jì)、材料選擇、先進(jìn)封裝制程之間尋找良好的平衡與解決方案。任何細(xì)小的環(huán)節(jié)都將影響系統(tǒng)級(jí)封裝產(chǎn)品的成本、可制造性、性能與可靠性,考慮不周有可能導(dǎo)致產(chǎn)品開發(fā)延期和開發(fā)成本急劇上升,甚至導(dǎo)致產(chǎn)品報(bào)廢。系統(tǒng)級(jí)設(shè)計(jì)封裝流程如下圖2.26。

圖2.26系統(tǒng)級(jí)設(shè)計(jì)封裝流程

1) 設(shè)計(jì)需求分析和設(shè)計(jì)要求的輸入,需要就是要將產(chǎn)品的設(shè)計(jì)指標(biāo)明確化,量化。確定系統(tǒng)封裝產(chǎn)品的應(yīng)用類型、性能要求等基本信息。

2)設(shè)計(jì)方案定義,主要包括:SiP相關(guān)資料收集、裸芯片物理尺寸、管腳定義、能否采購等。封裝類型是采用BGA還是其他封裝形式、封裝尺寸的確定、管腳間距、數(shù)目的確定。采用自定義管腳排列方式還是采用標(biāo)準(zhǔn)封裝。封裝工藝和材料選擇,根據(jù)其應(yīng)用領(lǐng)域選擇塑料封裝、陶瓷封裝或金屬封裝。以及可能存在的潛在風(fēng)險(xiǎn)。

3)設(shè)計(jì)前方案評(píng)估,主要是當(dāng)所有的參數(shù)定義明確后進(jìn)行方案的初步討論和評(píng)估,將潛在的風(fēng)險(xiǎn)減小和量化以及想好解決方案。

4)原理圖設(shè)計(jì)和仿真建模同步進(jìn)行,通過假定分析 ,確定設(shè)計(jì)層疊結(jié)構(gòu)、關(guān)鍵信號(hào)的網(wǎng)絡(luò)拓?fù)浣Y(jié)構(gòu)、阻抗匹配,以及電源平面的分割、電容種類及型號(hào)選擇等,并在設(shè)計(jì)過程中建立好仿真模型,對(duì)模型進(jìn)行仿真驗(yàn)證。仿真驗(yàn)證包括對(duì)數(shù)模混合電路根據(jù)需要進(jìn)行電路功能仿真,對(duì)機(jī)械與熱進(jìn)行的熱應(yīng)力仿真,對(duì)RF射頻信號(hào)的電磁天線仿真,對(duì)光學(xué)信號(hào)的光路仿真等。

5)主要是為了確定 SiP 采用哪種工藝 ,如Wire Bonding、FlipChip、TAB、TSV等。基板上是否要挖腔體,采用單面腔體還是雙面腔體,以及腔體結(jié)構(gòu)等。同時(shí)要考慮是否做芯片堆疊 Chip stack,基板的層數(shù)以及層疊結(jié)構(gòu)等通常在這一步要確定下來。

6)基板層疊設(shè)置,約束規(guī)則設(shè)置,根據(jù)工藝確定及設(shè)計(jì)復(fù)雜程度進(jìn)行 SiP 基板層疊結(jié)構(gòu)設(shè)置,包括層數(shù)以及層疊結(jié)構(gòu)的選擇,基板內(nèi)部走線的設(shè)計(jì),以及加工工藝的選擇等。約束規(guī)則主要包括間距約束、差分線約束、信號(hào)線分類、高速信號(hào)約束。

7)器件布局,確定裸芯片在 SiP 封裝中的位置。如果芯片需要放置到腔體里,則需要確定腔體的深度以及是單階還是多階腔體, 腔體形狀的繪制和屬性設(shè)置等;如果需要設(shè)計(jì)芯片堆疊,則堆疊芯片后再進(jìn)行布局。

8)鍵合、貼裝、布線、覆銅,根據(jù)芯片及元器件的排列選擇適合的工藝,以及走線方式保證信號(hào)的連接。

9)設(shè)計(jì)檢查,通常情況下設(shè)計(jì)完成后對(duì)整體設(shè)計(jì)對(duì)照checklist進(jìn)行仔細(xì)檢查,保證每一項(xiàng)設(shè)計(jì)需求都可以達(dá)到。并滿足設(shè)計(jì)規(guī)則的約束。

10)設(shè)計(jì)后的仿真,設(shè)計(jì)完成后將版圖設(shè)計(jì)數(shù)據(jù)導(dǎo)出到仿真工具,進(jìn)行信號(hào)完整性、電源完整性、電磁場(chǎng)及熱等方面的仿真。解決由于信號(hào)質(zhì)量、供電不足、噪聲等產(chǎn)生的問題,以及由于芯片功耗過大而發(fā)生的過熱問題,確保產(chǎn)品工作的穩(wěn)定和可靠性。仿真如果順利通過,則進(jìn)入到下一步,如果不能通過則需要回到前仿真,進(jìn)行優(yōu)化后重新設(shè)計(jì)和仿真。

11) 輸出設(shè)計(jì)文件,將設(shè)計(jì)文件cad圖紙,仿真結(jié)果等輸出仿真報(bào)告。完成設(shè)計(jì)。

12)將設(shè)計(jì)文件結(jié)合生產(chǎn)設(shè)備與工藝進(jìn)行輸出生產(chǎn)可操作性文件。

13)設(shè)計(jì)結(jié)束。

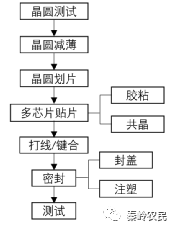

設(shè)計(jì)完成后就是封裝和組裝了,封裝工藝包括清洗,貼片,焊接,綁線,封蓋等

圖2.27系統(tǒng)級(jí)封裝流程

1)晶圓測(cè)試

就是對(duì)晶圓上每個(gè)芯片進(jìn)行測(cè)試,測(cè)試每個(gè)芯片上凸點(diǎn)的電特性,不合格的芯片會(huì)標(biāo)上記號(hào)并淘汰,以確保出產(chǎn)的每個(gè)芯片的正常功能和性能,也被稱為中間測(cè)試(中測(cè)),目前應(yīng)用最為廣泛的晶圓測(cè)試是使用探針測(cè)試臺(tái)等設(shè)備完成測(cè)試操作。

圓片探測(cè)是半導(dǎo)體制造過程中最后一道工藝。在這里對(duì)器件進(jìn)行完整的測(cè)量。在晶圓制造完成之后的圓片被分切成封裝管芯之前,對(duì)大晶片的每個(gè)芯片進(jìn)行測(cè)試,以確定它的功能與性能。晶圓測(cè)試也就是芯片分選測(cè)試(die sort)或晶圓電測(cè)(wafer probe)。測(cè)試是為了3個(gè)目的:晶圓被送到封裝廠之前,鑒別出合格芯片;對(duì)器件 / 電路的電性能參數(shù)進(jìn)行特性評(píng)估;芯片的合格品與不良品的核算會(huì)給晶圓生產(chǎn)人員提供全面業(yè)績(jī)的反饋。

2)芯片減薄技術(shù)

為了將2層甚至多層的芯片組裝在一個(gè)高度小于或是更小的堆疊芯片封裝體中,制造商致力于實(shí)現(xiàn)更薄的基板、更低的引線鍵合弧度、更低的塑封帽和更薄的芯片。芯片減薄技術(shù)是疊層裸芯片封裝的關(guān)鍵技術(shù)。因?yàn)樗档土藛蝹€(gè)芯片封裝高度,從而不會(huì)因?yàn)樾酒B加而增加系統(tǒng)的整體高度。

芯片減薄還可以提 高 散熱效率、機(jī)械性能、電性能,減小封裝體積,減輕劃片加工量。減薄技術(shù)包括背面研磨、化學(xué)刻蝕和等離子體刻蝕。機(jī)械研磨是最普通的方法,就是從晶圓背部去除多余的硅材料。當(dāng)前標(biāo)準(zhǔn)的晶圓減薄工藝(背部研磨和拋光)能將將厚度為300um的晶圓減至50um。甚至低于50um。

背部研磨通常會(huì)在晶圓表面留下微小缺陷。化學(xué)刻蝕和等離子體工藝可用于完成較低厚度的芯片減薄,且工藝過程對(duì)晶圓產(chǎn)生的應(yīng)力較小。典型的減薄工藝流程是先背部減薄,接著采用濕刻蝕技術(shù),可清除最后10~30um厚度的硅。

3)芯片貼片

芯片疊層是要求芯片在Z方向的疊加過程中實(shí)現(xiàn)高精度貼裝,要保證芯片在貼裝過程中盡量不產(chǎn)生漂移。芯片與芯片之間需采用絕緣膠粘接,而最底層的芯片直接和引線框架相接,所以可以用導(dǎo)電膠或者焊錫。芯片粘結(jié)工藝就有兩種,膠水粘結(jié)和共晶焊接。膠水和共晶需要共同考慮的問題有粘接應(yīng)力,導(dǎo)熱,以及粘結(jié)溫度曲線。

4)芯片密封

密封工藝是為了保護(hù)芯片保護(hù)器件不受外界環(huán)境的侵害,并提供足夠的機(jī)械支持。就包括了塑封和管殼封裝,管殼又包括陶瓷管殼和金屬管殼。根據(jù)芯片工作環(huán)境和芯片性能選擇合適的密封工藝。

審核編輯:劉清

-

晶圓

+關(guān)注

關(guān)注

52文章

4851瀏覽量

127816 -

TAB

+關(guān)注

關(guān)注

0文章

15瀏覽量

11545 -

SiP技術(shù)

+關(guān)注

關(guān)注

0文章

10瀏覽量

7937

原文標(biāo)題:SiP 產(chǎn)品從設(shè)計(jì)到封裝

文章出處:【微信號(hào):gh_38186cae1d9a,微信公眾號(hào):秦嶺農(nóng)民】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

Cadence發(fā)布推動(dòng)SiP IC設(shè)計(jì)主流化的EDA產(chǎn)品

3GPP R4版本為什么使用BICC協(xié)議而不是SIP-T?

SiP的11個(gè)誤區(qū)盤點(diǎn)

SIP協(xié)議性能測(cè)試的方法

SIP協(xié)議,什么是SIP協(xié)議

SIP立體封裝器件自動(dòng)回流焊裝配規(guī)范

SIP立體封裝器件手動(dòng)裝配規(guī)范

陶瓷封裝SiP腔體結(jié)構(gòu)介紹

SIP協(xié)議的定義及基本流程

淺談?dòng)布娐烽_發(fā)流程規(guī)范

生產(chǎn)電容器時(shí)流程不規(guī)范會(huì)有什么后果?

SiP產(chǎn)品嚴(yán)格而規(guī)范的設(shè)計(jì)流程

SiP產(chǎn)品嚴(yán)格而規(guī)范的設(shè)計(jì)流程

評(píng)論