PCB 布局和參考回流路徑的設(shè)計(jì)在電路的 EMC 性能中都是至關(guān)重要的因素,且對(duì)于電源轉(zhuǎn)換電路來(lái)說(shuō)尤其重要。因此設(shè)計(jì)初期將回流路徑可視化是重要的一個(gè)環(huán)節(jié),通過(guò)將回流路徑可視化,可以輔助設(shè)計(jì)和控制整個(gè)回路的區(qū)域。

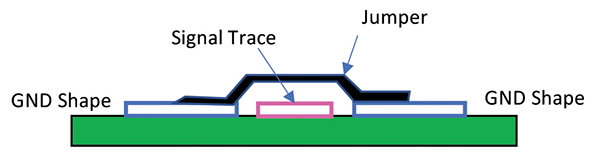

可視化回流路徑可以直觀看到整個(gè)信號(hào)或者電源的工作區(qū)域,從而找到減少回路感抗和高頻阻抗的方法。在單層PCB設(shè)計(jì)時(shí),我們沒(méi)有完整的地返回平面,有時(shí)這就需要引用額外的去耦電容或者“飛線”,以便減少回路面積。圖1為一個(gè)飛線的例子。

圖1:?jiǎn)螌语w線連接GND

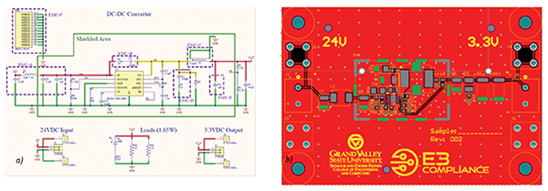

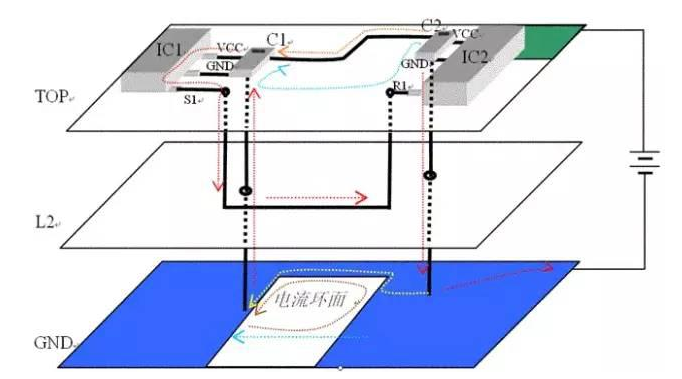

在兩層板中,相對(duì)于單層板具有更多的優(yōu)勢(shì),因?yàn)閷优c層之間走線可以由過(guò)孔連接,并優(yōu)化回路面積。圖 2 顯示了在頂層和底層通過(guò)過(guò)孔連接GND,并改善回流路徑的示例。

圖2兩層板示意圖

有時(shí)在做PCB設(shè)計(jì)的時(shí)候會(huì)建議割地處理(例如模擬和數(shù)字地),但根據(jù)我們的經(jīng)驗(yàn),這樣做往往會(huì)導(dǎo)致額外的EMC問(wèn)題。

一、可視化完整的回流路徑

在設(shè)計(jì)過(guò)程中,我們建議將所有電源和信號(hào)路徑的正向和返回電流分三步繪制。步驟 1:在原理圖上繪制的完整的電源路徑。第2步:在PCB圖上同樣繪制電源路徑。步驟 3:根據(jù)上面兩步的結(jié)果,優(yōu)化 PCB 布局和最小化環(huán)路面積。

在討論DC-DC電路設(shè)計(jì)時(shí),回流路徑的設(shè)計(jì)一直是關(guān)注的重點(diǎn)。如圖 3 所示,一款DC-DC降壓電路的原理圖和PCB布局。圖 3a:原理圖。圖 3b:PCB。

圖 3:a)原理圖 b)PCB

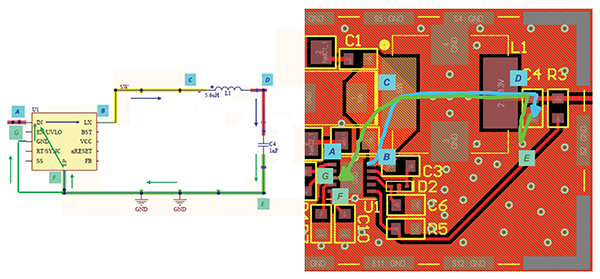

對(duì)圖3電路可視化回流路徑,參考圖4。電流的正向路徑為ABCD ,電流返回路徑為EFG 。

圖4:PCB的輸出濾波部分

在直流或低頻(低于100kHz ),電流會(huì)沿著阻值最小的路徑返回源端。在較高頻率下,回流信號(hào)會(huì)走感抗最小路徑。該感抗由電流的正向和返回路徑所形成的環(huán)路面積決定。當(dāng)回流路徑直接位于電流正向路徑下方時(shí),此時(shí)整個(gè)環(huán)路面積最小,感抗也最小。這意味著如果有完整的地平面,高頻電流會(huì)直接在正向路徑下方的地平面回流到源端,如圖 4 所示。

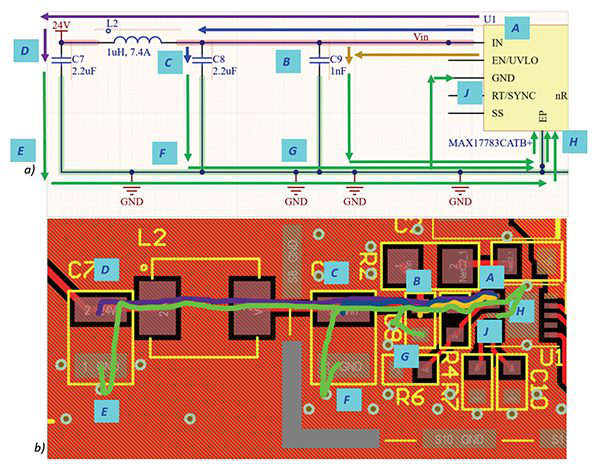

接下來(lái),讓我們看看圖 5 所示。

圖5:DC-DC濾波電路PCB

如圖所示,我們假設(shè)電流路徑從 U1(DC-DC芯片)的 Vin 開(kāi)始。在這種情況下,高頻電流有多個(gè)可能的返回路徑。高頻電流會(huì)根據(jù)頻率不同選擇經(jīng)過(guò)C7,C8或C9返回芯片源端,如圖5所示。例如,100MHz 的噪聲可能會(huì)選擇通過(guò)較小容值的C9回流,而較低頻率的噪聲(例如 500kHz)可能會(huì)選擇通過(guò)較大容值的 C7 或 C8回流。

二、經(jīng)驗(yàn)法則

為了減少了電流環(huán)路面積,并有助于減少開(kāi)關(guān)電源的輻射和傳導(dǎo)發(fā)射,有以下是幾個(gè) EMC 經(jīng)驗(yàn)法則:

1.在可能的情況下,在信號(hào)層底下保持完整的參考平面

3. 高速信號(hào)線盡量短,且挨著地線布線,以確保低阻抗路徑(最小環(huán)路面積)。

4. 在內(nèi)部開(kāi)關(guān)和續(xù)流二極管之間放置RC吸收電路,且吸收電路走線盡量短。

5. 在開(kāi)關(guān)元件(IC、電感等)下方鋪設(shè)完整參考平面。

審核編輯:郭婷

-

電源

+關(guān)注

關(guān)注

184文章

17207瀏覽量

247789 -

pcb

+關(guān)注

關(guān)注

4295文章

22776瀏覽量

393264 -

emc

+關(guān)注

關(guān)注

167文章

3800瀏覽量

182299

原文標(biāo)題:PCB 布局對(duì)電路EMC性能的影響

文章出處:【微信號(hào):mcu168,微信公眾號(hào):硬件攻城獅】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

高速電路PCB的EMC設(shè)計(jì)考慮

pcb設(shè)計(jì)中布局的要點(diǎn)是什么

PCB設(shè)計(jì)的EMC有哪些注意事項(xiàng)

不理解EMC,畫(huà)不好PCB!【硬件干貨】

pcb元件布局調(diào)整時(shí)應(yīng)注意哪些問(wèn)題

工程師需要知道的PCB回流問(wèn)題

pcb的電源回流講解方法

EMC之PCB設(shè)計(jì)技巧

pcb布局的基本原則

什么是信號(hào)回流路徑?

差分信號(hào)PCB布局布線時(shí)的幾個(gè)常見(jiàn)誤區(qū)

PCB布局規(guī)則與技巧分享

PCB電路設(shè)計(jì)參考布局

不了解EMC,怎么畫(huà)PCB?

PCB布局和參考回流路徑的設(shè)計(jì)對(duì)電路EMC性能的影響

PCB布局和參考回流路徑的設(shè)計(jì)對(duì)電路EMC性能的影響

評(píng)論