FPGA(Field-Programmable Gate Array),即現場可編程門陣列,它是在PAL、GAL、CPLD等可編程器件的基礎上進一步發展的產物。它是作為專用集成電路(ASIC)領域中的一種半定制電路而出現的,既解決了定制電路的不足,又克服了原有可編程器件門電路數有限的缺點。FPGA的開發相對于傳統PC、單片機的開發有很大不同。FPGA以并行運算為主,以硬件描述語言來實現;相比于PC或單片機(無論是馮諾依曼結構還是哈佛結構)的順序操作有很大區別,也造成了FPGA開發入門較難。

時至今日,FPGA市場的主要業者僅剩數家,包括Altera、Xilinx(賽靈思,過去稱為:智霖科技)、Actel、Atmel、Lattice、QuickLogic等,不過2007年11月QuickLogic也確定淡出FPGA市場,并轉進發展CSSP(CustomerSpecificStandardProduct)。下面給大家帶來了幾組原理圖設計:

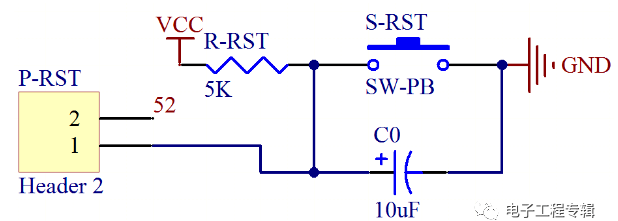

復位和晶振電路原理圖設計

一個芯片,尤其是可編程芯片,通常在上電的瞬間需要一個短暫的時間進行內部參數的初始化,這個時候芯片無法立即進入工作狀態。通常稱上電初始化這些工作為復位,完成這個功能的電路稱之為復位電路。本FPGA 芯片使用的是低電平復位,支持上電復位和手動復位,RESET 按下之后產生低電平。

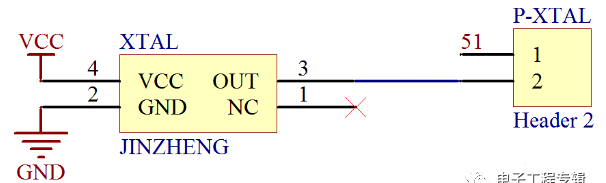

晶振電路原理圖設計

晶振是為電路提供頻率基準的元器件,通常分成有源晶振和無源晶振兩個大類,無源晶振需要芯片內部有振蕩器,并且晶振的信號電壓根據起振電路而定,允許不同的電壓,但無源晶振通常信號質量和精度較差,需要精確匹配外圍電路(電感、電容、電阻等),如需更換晶振時要同時更換外圍的電路。有源晶振不需要芯片的內部振蕩器,可以提供高精度的頻率基準,信號質量也較無源晶振要好。本FPGA 芯片采用50MHZ 的有源貼片晶振作為芯片工作的時鐘輸入。

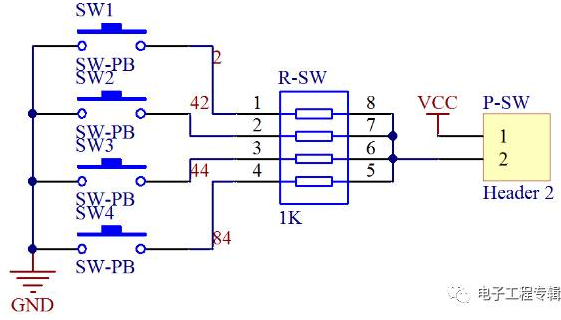

按鍵開關電路原理圖設計

最小系統板上使用的四腿按鍵實際上是分兩組,每組中的兩個是相通的,而兩組直接是通過上面的按鈕來控制通斷狀態的。簡單理解成開關就可以了,按下去兩端就形成短路,松開手就形成開路。短路相當于輸入0,開路為1。另外需要說明的是,由于按鍵屬于機械開關,按動過程不可避免存在抖動的現象,所以用戶按下按鍵的時間可以稍微長一點。

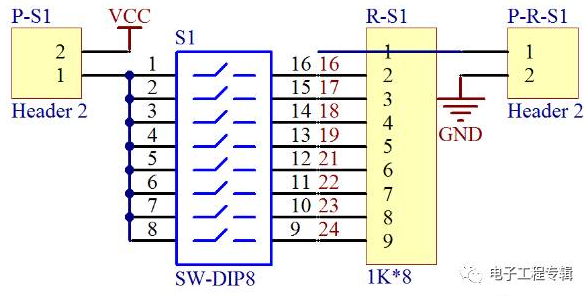

八位撥碼開關電路原理圖設計

撥碼開關就是相當與一個開關量,撥到ON 就表示接通,OFF 就是斷開,在數字電路中對 0、1,通常用于二進制輸入。本課題最小系統板使用八位撥碼開關作為一個字節的輸入,撥到ON 時相當于輸入“1”,默認輸入“0”。

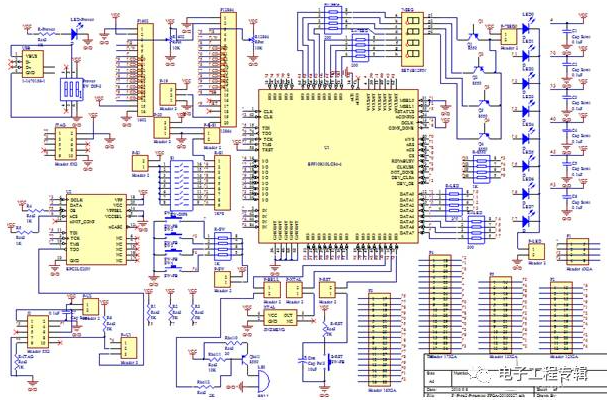

最小系統電路設計的總體電路原理圖

使用AlTIum 軟件設計的電路原理圖,FPGA 最小系統板包括時鐘電路、復位電路、電源電路、JATG 電路、PROM 配置電路、顯示模塊電路、開關電路以及各種接口電路。

FPGA產品的應用領域已經從原來的通信擴展到消費電子、汽車電子、工業控制、測試測量等廣泛的領域。把相對成熟的技術應用到某些特定領域如通訊,視頻,信息處理等等開發出滿足行業需要并能被行業客戶接受的產品這方面主要是FPGA技術和專業技術的結合問題。

另外還有就是與專業客戶的界面問題產品設計還包括專業工具類產品及民用產品,前者重點在性能,后者對價格敏感產品設計以實現產品功能為主要目的,FPGA技術是一個實現手段在這個領域,FPGA因為具備接口,控制,功能IP,內嵌CPU等特點有條件實現一個構造簡單,固化程度高,功能全面的系統產品設計將是FPGA技術應用最廣大的市場,具有極大的爆發性的需求空間產品設計對技術人員的要求比較高,路途也比較漫長不過現在整個行業正處在組建“首發團隊”的狀態,只要加入,前途光明產品設計是一種職業發展方向定位,不是簡單的愛好就能做到的!產品設計領域會造就大量的企業和企業家,是一個發展熱點和機遇。

審核編輯:郭婷

-

FPGA

+關注

關注

1626文章

21667瀏覽量

601861 -

單片機

+關注

關注

6032文章

44516瀏覽量

633036 -

cpld

+關注

關注

32文章

1247瀏覽量

169217 -

asic

+關注

關注

34文章

1194瀏覽量

120328 -

現場可編程門陣列

+關注

關注

1文章

20瀏覽量

4724

原文標題:幾組實用FPGA原理設計圖

文章出處:【微信號:FPGA研究院,微信公眾號:FPGA研究院】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

幾組實用FPGA原理設計圖

幾組實用FPGA原理設計圖

FPGAs的DSP性能該怎么分析?

如何分析FPGAs中的DSP性能?

STM32U599平衡圖顯性能與功耗的新一代產品

【電路分享】幾組實用FPGA原理設計圖

幾種FPGA原理設計圖的性能與應用分析

幾種FPGA原理設計圖的性能與應用分析

評論