Verilog例化說明

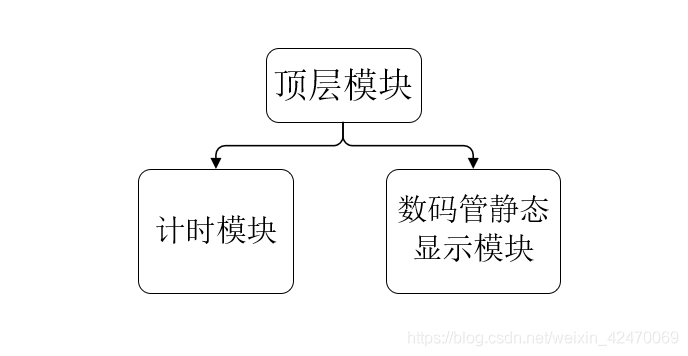

1.什么是模塊例化?為什么要例化?

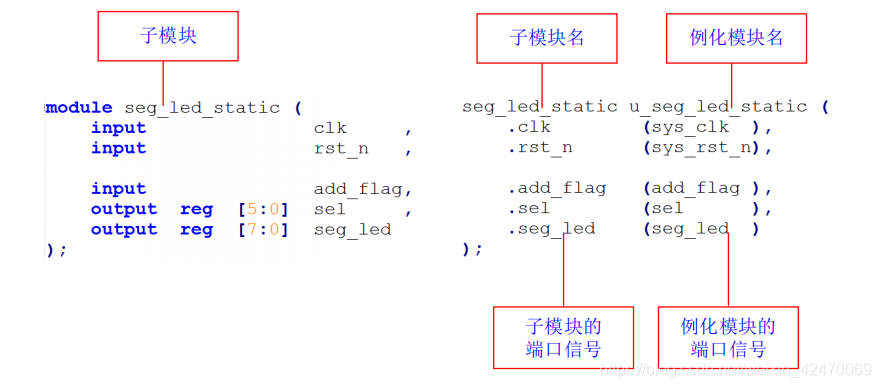

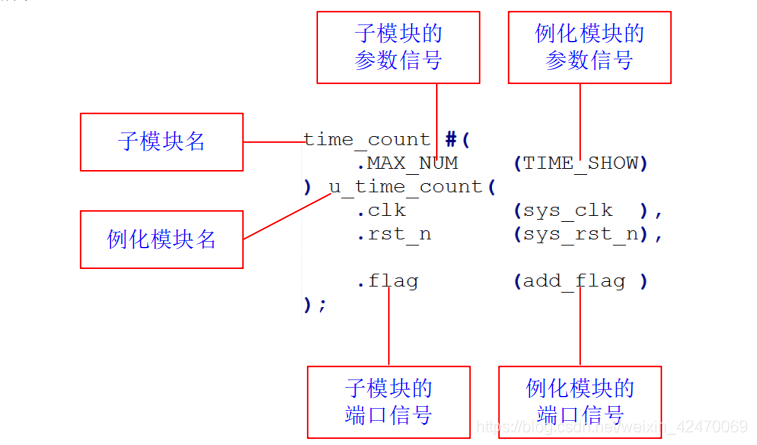

2.實例說明例化方法

歡迎加入至芯科技FPGA微信學習交流群,這里有一群優秀的FPGA工程師、學生、老師、這里FPGA技術交流學習氛圍濃厚、相互分享、相互幫助、叫上小伙伴一起加入吧!

點個在看你最好看

原文標題:FPGA學習-Verilog例化說明

文章出處:【微信公眾號:FPGA設計論壇】歡迎添加關注!文章轉載請注明出處。

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

FPGA

+關注

關注

1626文章

21671瀏覽量

601918

原文標題:FPGA學習-Verilog例化說明

文章出處:【微信號:gh_9d70b445f494,微信公眾號:FPGA設計論壇】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

Verilog vhdl fpga

相關專業,具有良好的專業基礎知識。 感興趣可滴滴 JYHXDX534

2.工作年限不限,有工作經驗或優秀應屆畢業生亦可。

3.對FPGA芯片架構和資源有深入的理解,精通Verilog HDL、VHDL

發表于 11-12 16:40

FPGA加速深度學習模型的案例

FPGA(現場可編程門陣列)加速深度學習模型是當前硬件加速領域的一個熱門研究方向。以下是一些FPGA加速深度學習模型的案例: 一、基于FPGA

FPGA編程語言的入門教程

FPGA(現場可編程邏輯門陣列)的編程涉及特定的硬件描述語言(HDL),其中Verilog和VHDL是最常用的兩種。以下是一個FPGA編程語言(以Verilog為

FPGA Verilog HDL代碼如何debug?

,共同進步。

歡迎加入FPGA技術微信交流群14群!

交流問題(一)

Q:Verilog代碼如何debug?最近學習fpga,寫了不少verilog

發表于 09-24 19:16

【招聘】verilog vhdl FPGA

1.熟悉FPGA架構及應用,熟悉圖像算法的FPGA實現。

2.熟悉verilog vhdl,熟悉Xilinx或Intel等開發工具。

3.有AI算法 fpga實現經驗優先。

4.本科及

發表于 09-02 15:50

求助各位關于Verilog當中模塊例化、端口與引腳 的問題

初學者。我在刷HDLbits的時候做到了這道題

答案:

答案給的是定義了wire型的信號,并借這個來進行端口連接。而我的疑問在于:

1.模塊例化時,如果采用按名字的方式進行例化,那么:點號后面寫

發表于 07-15 20:38

FPGA基礎知識學習

語言(HDL)如VHDL或Verilog來描述。這些描述定義了電路的功能和信號流,然后通過各種電子設計自動化(EDA)工具進行輔助設計、綜合化、布局和布線等處理,最終將設計轉化為可以在FPGA

發表于 04-29 23:26

如何快速入門FPGA

時鐘管理模塊、嵌入式塊RAM、布線資源等。

學習FPGA編程語言:

掌握Verilog HDL(硬件描述語言)。Verilog用于數字電路的系統設計,具有簡潔的語法和清晰的仿真語義,非

發表于 04-28 09:06

FPGA學習資料分享

的學習資源Verilog 教程,數字邏輯設計 (點擊文字進入鏈接).

具備一定硬件描述語言基礎是發開FPGA通用的。此外就是根據廠家型號、環境和提供的資源,能有效使用組織起來,實現目標功能,這更傾向于實踐應用。 大家有關于實踐應

發表于 03-31 13:23

# FPGA 編程如何工作?

的構建塊。邏輯門對輸入和輸出數據執行布爾運算。還有將信號從一點路由到另一點的路由資源。

FPGA 編程用例

FPGA 編程對現代世界的開發人員非常有吸引力。

以下是一些用例;

=#1

發表于 03-30 11:50

fpga是用c語言還是verilog

FPGA(現場可編程邏輯門陣列)開發主要使用的編程語言是硬件描述語言(HDL),其中Verilog是最常用的編程語言之一。而C語言通常用于傳統的軟件編程,與FPGA的硬件編程有所區別。

fpga是什么專業學的

FPGA(現場可編程門陣列)的學習涉及多個專業領域,但主要與電子信息類、自動化類、計算機類等相關專業最為緊密。這些專業通常涵蓋數字電路設計、硬件描述語言(如Verilog和VHDL)編

值得多看的FPGA 學習路線

,我總結了這份FPGA學習路線

FPGA入門學習第一部分:硬件編程語言

FPGA的編程語言,是我們必須掌握的內容。和軟件開發使用的C、C++

發表于 01-02 23:03

FPGA學習-Verilog例化說明

FPGA學習-Verilog例化說明

評論