Ann Kelleher介紹了晶體管誕生75年之后的新進展

在IEDM 2022(2022 IEEE國際電子器件會議)全體會議上發表演講之前,英特爾副總裁兼技術開發總經理Ann Kelleher接受了《IEEE Spectrum》的采訪,她表示,摩爾定律的下一波浪潮將依靠名為系統工藝協同優化(system technology co-optimization, STCO)的發展理念。

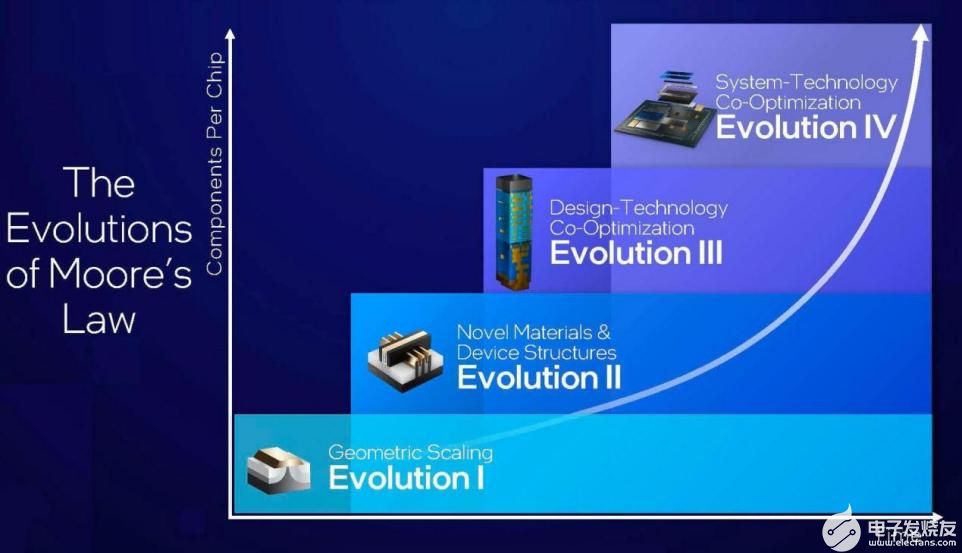

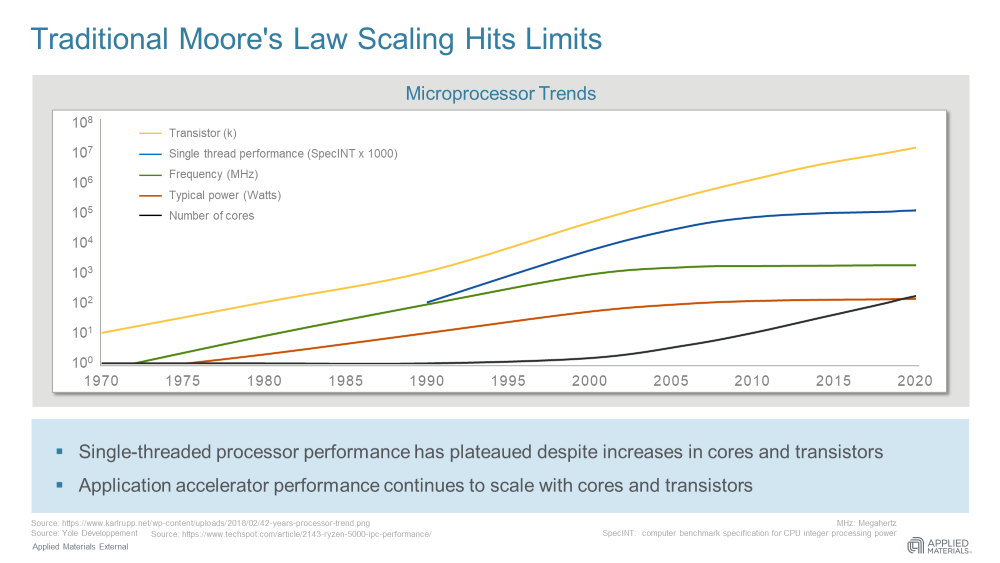

Kelleher認為,摩爾定律關乎功能集成度的提升,展望未來10到20年,可以看到一條充滿創新潛力的道路,將延續每兩年改進一次產品的節奏,其中將包括半導體制程和設計的常規發展,但系統工藝協同優化會發揮最大作用。

Kelleher稱系統工藝協同優化為一種“由外向內”的發展模式,從產品需支持的工作負載及其軟件開始,到系統架構,再到封裝中必須包括的芯片類型,最后是半導體制程工藝。“所謂系統工藝協同優化,就是把所有環節共同優化,由此盡可能地改進最終產品。”Kelleher說。

系統工藝協同優化之所以成為當下的一個重要選項,很大程度上是因為先進封裝技術,如3D集成,支持在單個封裝內實現芯粒(小且具有特定功能的芯片)的高帶寬連接。這意味著原來單芯片上的各個功能可以被分解到專門的芯粒上,而每個芯粒都可以采用最合適的的半導體制程技術進行制造。例如,Kelleher在其全體會議演講中指出,高性能計算要求每個處理器內核都有大量緩存,但芯片制造商微縮SRAM(靜態隨機存取存儲器)的能力并沒有跟上邏輯單元微縮的步伐。因此,使用不同制程技術把SRAM緩存和計算內核分別制成單獨的芯粒,并利用3D集成技術將它們組接起來,是一種有意義的做法。

Kelleher談到,系統工藝協同優化在實際應用中的一個重要案例是位于極光(Aurora)超級計算機核心的Ponte Vecchio處理器。它由47個芯粒(以及8個用于熱傳導的空白芯片)組成,利用先進的平面連接(2.5D封裝技術)和3D堆疊技術拼接在一起。Kelleher說:“它匯集了不同晶圓廠生產的芯片,并將它們有效地組合起來,以便系統能夠執行所設計的工作負載。”

英特爾認為系統工藝協同優化是摩爾定律的下一個發展階段。

英特爾在IEDM 2022上展示了3D混合鍵合研究成果,相比2021年公布的成果,其密度又提升了10倍。連接密度的增加意味著可以將更多芯片功能分解到獨立的芯粒上,進而又提升了通過系統工藝協同優化實現成果改進的潛力。采用這項新技術,混合鍵合間距(即互連之間的距離)僅為3微米,借此可以將更多的緩存從處理器內核中分離。Kelleher認為,如果能將鍵合間距減少到2微米至100納米之間,將有可能實現邏輯功能的分離。目前,邏輯功能必須位于同一塊芯片上。

通過分解功能來優化系統,這種趨勢正在深刻影響著對未來的半導體制造工藝。未來的半導體制程技術必須要應對3D封裝環境的熱應力,但互連技術的變化可能最大。Kelleher表示,英特爾有望在2024年推出一項名為PowerVia(通常指背面供電)的技術。PowerVia將供電網絡移動到芯片下方,從而減小了邏輯單元的尺寸并降低了功耗。Kelleher介紹,它同時“提供了不同的機會,讓我們能夠探索如何在單個封裝內進行互連” 。

系統工藝協同優化(STCO)通過同步優化從軟件到制程技術的一切,更全面地改進計算機系統。

Kelleher強調,系統工藝協同優化仍處于起步階段。EDA(電子設計自動化)工具已經解決了系統工藝協同優化的前身——也就是設計工藝協同優化(design technology co-optimization, DTCO)的挑戰,側重于邏輯單元級(logic-cell level)和功能塊級(functional-block level)的優化。Kelleher介紹:“一些EDA工具供應商已經在進行系統工藝協同優化的相關工作了,未來的重點將落在幫助其實現的方法和工具上。”

隨著系統工藝協同優化的發展,工程師們可能需要隨著它一起進步。Kelleher說:“一般而言,工程師需要不斷掌握器件知識,但也要開始了解其技術和器件的用例。隨著系統工藝協同優化逐步深入發展,將需要更多的跨學科技能。”

英特爾的制程路線圖

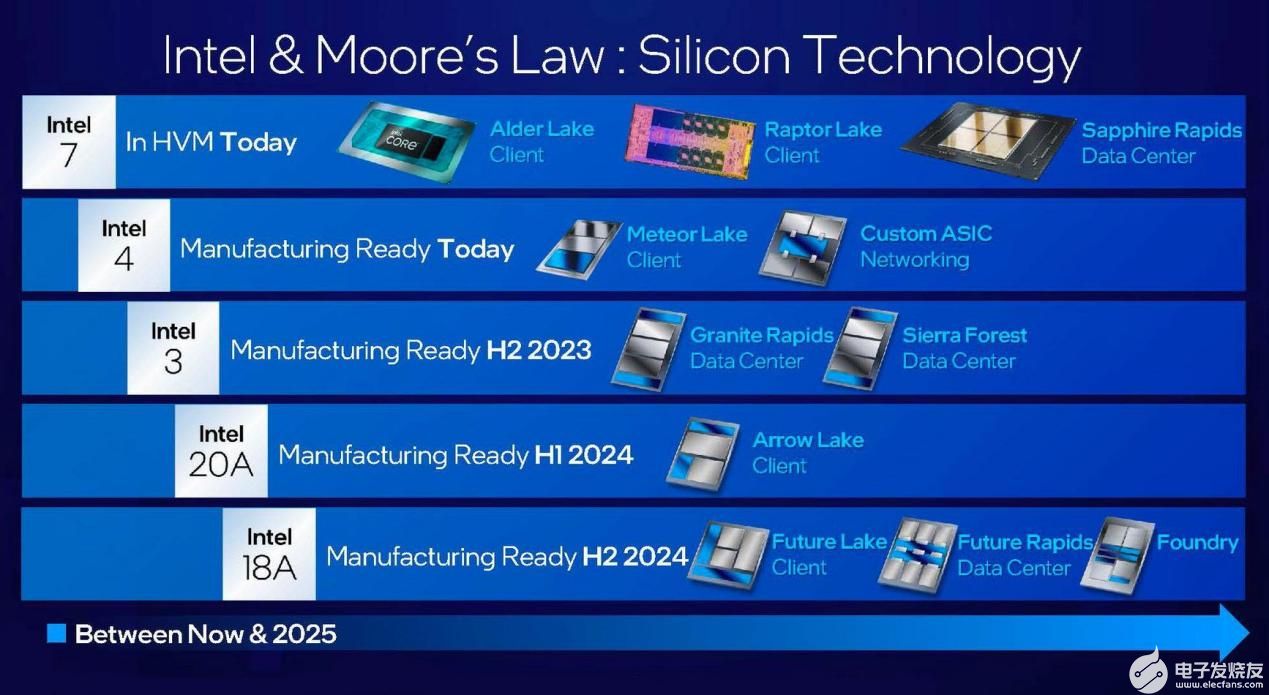

Kelleher還介紹了英特爾的最新制程路線圖,將其與摩爾定律的推進以及自晶體管發明以來的器件的演進聯系起來。Kelleher表示,自英特爾在不到兩年前公布新的制程路線圖開始,一切都在步入正軌。同時,她也補充了一些細節,比如哪些處理器將率先采用新技術。

英特爾正在按部就班地推進其制程技術路線圖。

預計于2024年上半年投產的Intel 20A取得了技術上的重大飛躍。它引入了一種新的晶體管架構——RibbonFET(通常被稱為全環繞柵極或納米片晶體管)以及PowerVia背面供電技術。當被問到這項技術可能涉及的風險時,Kelleher解釋了英特爾的戰略。

Kelleher稱:“這些并不需要同時完成,但我們看到了采用PowerVia來實現RibbonFET技術的顯著優勢。” 她解釋道,兩者的發展是并行的,這樣可以減少延誤的風險。英特爾正在使用FinFET(目前正在使用的晶體管架構)和PowerVia進行測試。 “進展非常順利,我們能夠加快研發步伐了。” Kelleher表示。

未來的晶體管

Kelleher發表演講之際,正值IEEE電子器件協會慶祝晶體管發明75周年。在《IEEE Spectrum》雜志上,我們向專家們提問,在2047年,誕生100周年之際,晶體管會變成什么樣子。Kelleher認為,晶體管技術是一項長壽技術,平面晶體管設計一直從上世紀60年代持續到2010年左右,而它的繼任者FinFET仍然很強大。她表示:“現在,我們將采用RibbonFET,它可能會延續20年或更久......我預計我們將在某個時間點開始堆疊RibbonFET晶體管。然而,到那時晶體管的帶(ribbon)可能會由2D半導體制成,而不是硅。”

審核編輯黃昊宇

-

芯片

+關注

關注

454文章

50460瀏覽量

421980 -

英特爾

+關注

關注

60文章

9900瀏覽量

171551 -

晶體管

+關注

關注

77文章

9641瀏覽量

137876

發布評論請先 登錄

相關推薦

擊碎摩爾定律!英偉達和AMD將一年一款新品,均提及HBM和先進封裝

英特爾IT的發展現狀和創新動向

英特爾是如何實現玻璃基板的?

“自我實現的預言”摩爾定律,如何繼續引領創新

英特爾CEO:AI時代英特爾動力不減

英特爾CEO基辛格:摩爾定律放緩,仍能制造萬億晶體

英特爾CEO基辛格:摩爾定律仍具生命力,且仍在推動創新

后摩爾定律時代,Chiplet落地進展和重點企業布局

英特爾Ann Kelleher:系統工藝協同優化將引領摩爾定律未來創新

英特爾Ann Kelleher:系統工藝協同優化將引領摩爾定律未來創新

評論