對于系統設計工程師來說,時序問題在設計中是至關重要的,尤其是隨著時鐘頻率的提高,留給數據傳輸的有效讀寫窗口越來越小,要想在很短的時間限制里,讓數據信號從驅動端完整地傳送到接收端,就必須進行精確的時序計算和分析。同時,時序和信號完整性也是密不可分的,良好的信號質量是確保穩定的時序的關鍵,由于反射,串擾造成的信號質量問題都很可能帶來時序的偏移和紊亂。因此,對于一個信號完整性工程師來說,如果不懂得系統時序的理論,那肯定是不稱職的。本章我們就普通時序(共同時鐘)和源同步系統時序等方面對系統時序的基礎知識作一些簡單的介紹。

普通時序系統(共同時鐘系統)

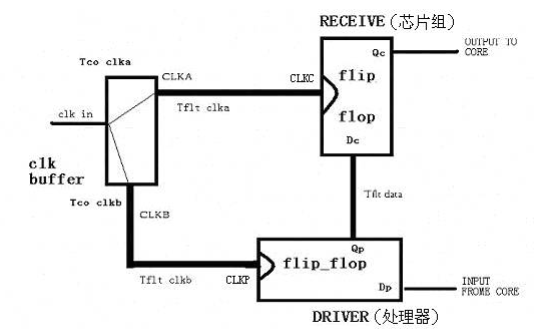

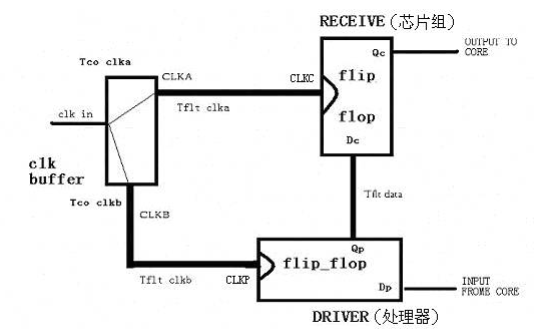

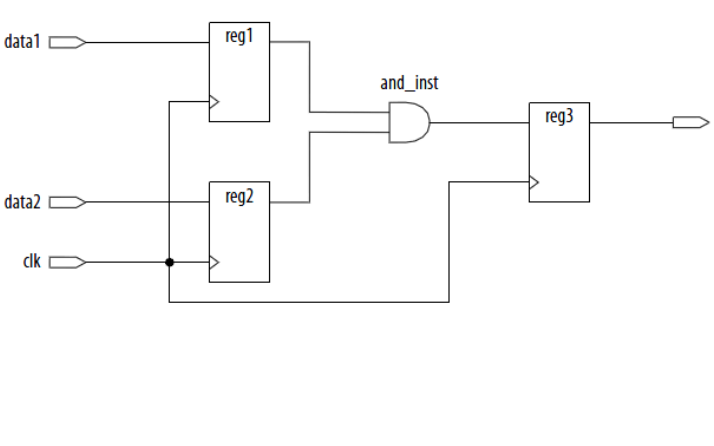

所謂普通時序系統就是指驅動端和接收端的同步時鐘信號都是由一個系統時鐘發生器提供。下圖就是一個典型的普通時鐘系統的示意圖,表示的是計算機系統的前端總線的時序結構,即處理器(CPU)和芯片組(Chipset)之間的連接。

在這個例子中,驅動端(處理器)向接收端(芯片組)傳送數據,我們可以將整個數據傳送的過程考慮為三個步驟:

1.核心處理器提供數據;

2.在第一個系統時鐘的上升沿到達時,處理器將數據Dp鎖存至Qp輸出;

3.Qp沿傳輸線傳送到接收端觸發器的Dc,并在第二個時鐘上升沿到達時,將數據傳送到芯片組內部。一般來說,標準普通時鐘系統的時鐘信號到各個模塊是同步的,即圖中的Tflt clka和Tflt clkb延時相同。通過分析不難看出,整個數據從發送到接收的過程需要經歷連續的兩個時鐘沿,也就是說,如果要使系統能正常工作,就必須在一個時鐘周期內讓信號從發送端傳輸到接收端。如果信號的傳輸延遲大于一個時鐘周期,那么當接收端的第二個時鐘沿觸發時,就會造成數據的錯誤讀取,因為正確的數據還在傳輸的過程中,這就是建立時間不足帶來的時序問題。

目前普通時序系統的頻率無法得到進一步提升的原因就在于此,頻率越高,時鐘周期越短,允許在傳輸線上的延時也就越小,200-300MHz已經幾乎成為普通時序系統的頻率極限。那么,是不是傳輸延時保持越小就越好呢?當然也不是的,因為它還必須要滿足一定的保持時間。在接下來幾節里,我們就建立和保持時間來分析一下時序設計需要考慮的一些問題以及正確的系統時序所必須滿足的條件。

時序參數的確定

對于時序問題的分析,我們首先要清楚地理解相關的一些時序參數的具體含義,比如Tco,緩沖延時,傳播延遲,最大/小飛行時間,建立時間,保持時間,建立時間裕量,保持時間裕量,時鐘抖動,時鐘偏移等等,如果對這些參數的概念理解不深刻,就很容易造成時序設計上的失誤。

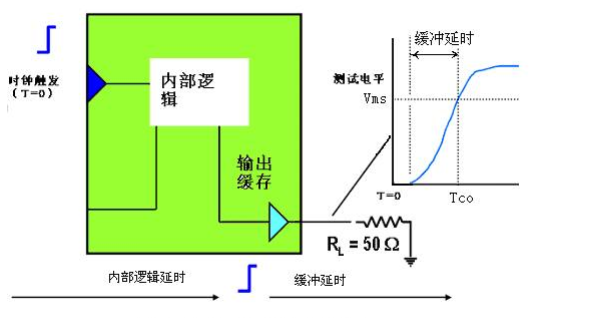

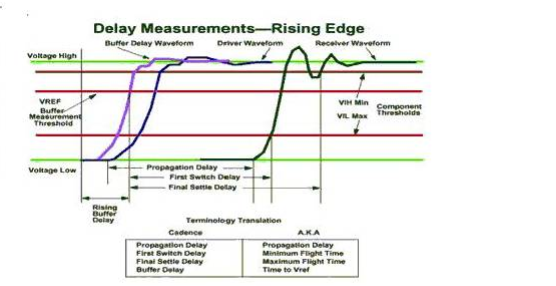

首先要闡明的是Tco和緩沖延時(buffer delay)的區別。從定義上來說,Tco是指時鐘觸發開始到有效數據輸出的器件內部所有延時的總和;而緩沖延時是指信號經過緩沖器達到有效的電壓輸出所需要的時間。可以看出,Tco除了包含緩沖延時,還包括邏輯延時。通常,確定Tco的方法是在緩沖輸出的末端直接相連一個測量負載,最常見的是50歐姆的電阻或者30pF的電容,然后測量負載上的信號電壓達到一定電平的時間,這個電平稱為測量電壓(Vms),一般是信號高電平的一半。如Tco和緩沖延時的確定如下圖所示:

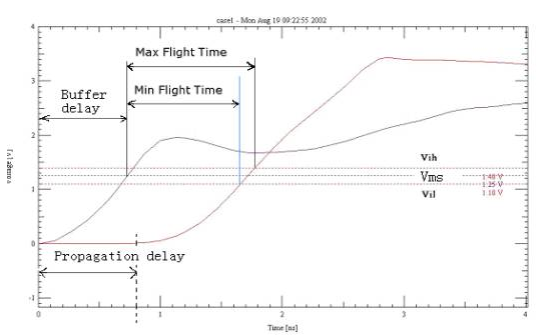

信號從緩沖器出來之后,就要經過傳輸線到接收終端,信號在傳輸線上的傳輸的延時我們稱為傳播延遲(propagationdelay),它只和信號的傳播速度和線長有關。然而我們在大多數時序設計里面,最關鍵的卻不是傳播延遲這個參數,而是飛行時間(Flight Time)參數,包括最大飛行時間(Max Flight Time)和最小飛行時間(Min Flight Time)。飛行時間包含了傳播延遲和信號上升沿變化這兩部分因素,從下圖中可以很容易看出兩者的區別。

在較輕的負載(如單負載)情況下,驅動端的上升沿幾乎和接收端的信號的上升沿平行,所以這時候平均飛行時間和傳播延遲相差不大;但如果在重負載(如多負載)的情況下,接收信號的上升沿明顯變緩,這時候平均飛行時間就會遠遠大于信號的傳播延遲。這里說的平均飛行時間是指Buffer波形的Vms到接收端波形Vms之間的延時,這個參數只能用于時序的估算,準確的時序分析一定要通過仿真測量最大/最小飛行時間來計算。

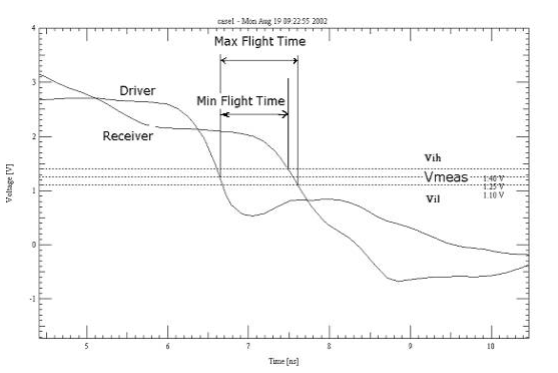

上面只是對信號上升沿的分析,對于下降沿來說,同樣存在著最大/最小飛行時間的參數,如下圖。在時序計算時我們實際取的最大飛行時間是在上升沿和下降沿中取最長的那個飛行時間,而最小飛行時間則是取上升和下降沿中最短的那個飛行時間。

也有些時候,人們對信號的最大/最小飛行時間還有其它稱謂,比如在Cadence軟件中,就將最大飛行時間稱為最終穩定延時(Final Settle Delay),而將最小飛行時間稱為最早開關延時

(First SwitchDelay),如下圖。

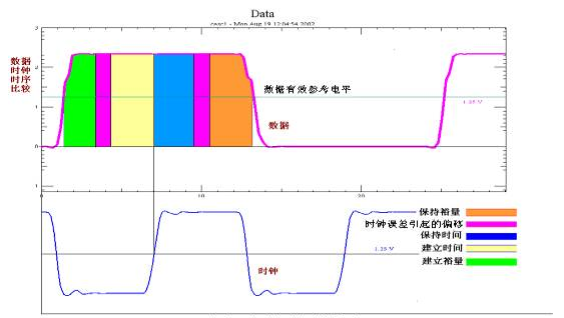

信號經過傳輸線到達接收端之后,就牽涉到建立時間和保持時間這兩個時序參數,它們是接收器本身的特性,表征了時鐘邊沿觸發時數據需要在鎖存器的輸入端持續的時間。通俗地說,時鐘信號來的時候,要求數據必須已經存在一段時間,這就是器件需要的建立時間(Setup Time);而時鐘邊沿觸發之后,數據還必須要繼續保持一段時間,以便能穩定的讀取,這就是器件需要的保持時間(Hold Time)。如果數據信號在時鐘沿觸發前后持續的時間均超過建立和保持時間,那么超過量就分別被稱為建立時間裕量和保持時間裕量。見下圖,其中還考慮了時鐘誤差的因素。

每個器件的建立和保持時間參數,一般都可以在相應的DataSheet查到,對于設計者來說最大的目的是提高時序的裕量,這樣即使信號完整性上出現一點問題,或者外界環境發生一定的變化,系統仍然能正常工作,這就是一個設計優良的系統應該體現出的超強的穩定性。

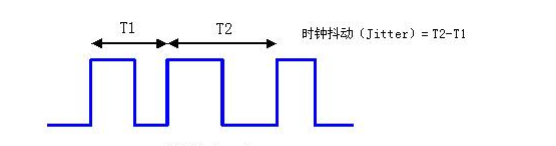

系統時序設計中對時鐘信號的要求是非常嚴格的,因為我們所有的時序計算都是以恒定的時鐘信號為基準。但實際中時鐘信號往往不可能總是那么完美,會出現抖動(Jitter)和偏移(Skew)問題。所謂抖動,就是指兩個時鐘周期之間存在的差值,這個誤差是在時鐘發生器內部產生的,和晶振或者PLL內部電路有關,布線對其沒有影響,如下圖。除此之外,還有一種由于周期內信號的占空比發生變化而引起的抖動,稱之為半周期抖動。總的來說,jitter可以認為在時鐘信號本身在傳輸過程中的一些偶然和不定的變化之總和。

時鐘偏移(skew)是指兩個相同的系統時鐘之間的偏移。它表現的形式是多種多樣的,既包含了時鐘驅動器的多個輸出之間的偏移,也包含了由于PCB走線誤差造成的接收端和驅動端時鐘信號之間的偏移,比如在下圖中所示,CLKA和CLKB之間的差異,CLKC和CLKP之間的差異均為時鐘偏移,這些偏移量在時序計算中需要全部考慮。

除了上面提到的這些概念,還有一點要注意的是,時刻不能忽略信號完整性對時序的影響,比如串擾會影響微帶線傳播延遲;反射會造成數據信號在邏輯門限附近波動,從而影響最大/最小飛行時間;時鐘走線的干擾會造成一定的時鐘偏移。有些誤差或不確定因素是仿真中無法預見的,設計者只有通過周密的思考和實際經驗的積累來逐步提高系統設計的水平。

審核編輯:湯梓紅

-

處理器

+關注

關注

68文章

19160瀏覽量

229115 -

FPGA

+關注

關注

1626文章

21665瀏覽量

601809 -

時鐘

+關注

關注

10文章

1720瀏覽量

131362 -

觸發器

+關注

關注

14文章

1995瀏覽量

61049 -

時序

+關注

關注

5文章

385瀏覽量

37275

原文標題:FPGA知識匯集-FPGA時序基礎理論

文章出處:【微信號:gh_873435264fd4,微信公眾號:FPGA技術聯盟】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

FPGA知識匯集-FPGA系統時序理論

FPGA時序約束的基礎知識

FPGA實戰演練邏輯篇48:基本的時序分析理論1

FPGA時序約束--基礎理論篇

FPGA設計:時序是關鍵

FPGA中的時序約束設計

FPGA時序約束的理論基礎知識說明

FPGA知識匯集-FPGA時序基礎理論

FPGA知識匯集-FPGA時序基礎理論

評論