半導(dǎo)體行業(yè)正在發(fā)生重大的戰(zhàn)略轉(zhuǎn)變,多晶粒 SoC逐漸成為行業(yè)主流,這對 SoC 的架構(gòu)和設(shè)計方式具有深遠(yuǎn)影響。這一戰(zhàn)略轉(zhuǎn)變的驅(qū)動因素主要有以下幾種:- 某些 SoC 的功能要獲得最佳實(shí)現(xiàn),可能需要不同的工藝節(jié)點(diǎn)

對增強(qiáng)產(chǎn)品的可擴(kuò)展性和可組合性需求正在增加

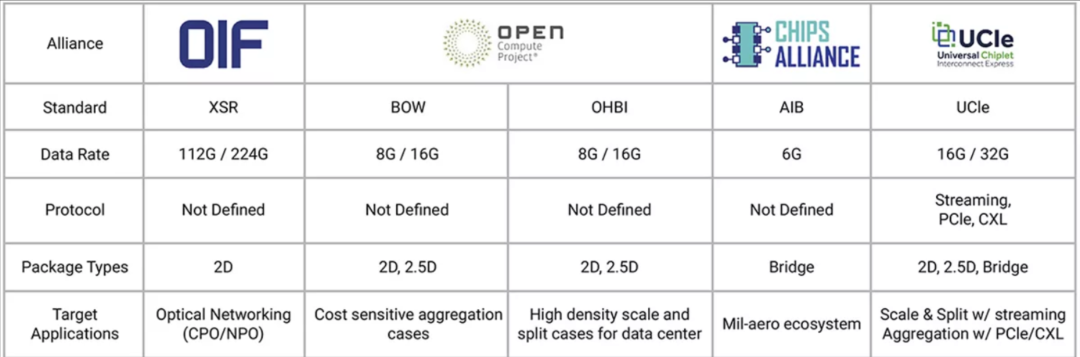

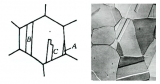

然而,由于多晶粒技術(shù)的新穎性及設(shè)計生態(tài)系統(tǒng)的匱乏,SoC 架構(gòu)師不得不暫停,甚至推遲其多晶粒 SoC 項(xiàng)目。不過,現(xiàn)在情況正在好轉(zhuǎn),全行業(yè)的參與者已開始攜手合作,為行業(yè)提供全面、集成的多晶粒設(shè)計和驗(yàn)證產(chǎn)品,以及全套先進(jìn)封裝選項(xiàng)。早期采用者已開始開發(fā)自己的專用晶粒間接口,但業(yè)界很快意識到,這種方法不利于組裝不同供應(yīng)商開發(fā)的晶粒。該行業(yè)需要標(biāo)準(zhǔn)化的晶粒間互連。多個行業(yè)聯(lián)盟已共同定義此類標(biāo)準(zhǔn),如圖 1 所示。

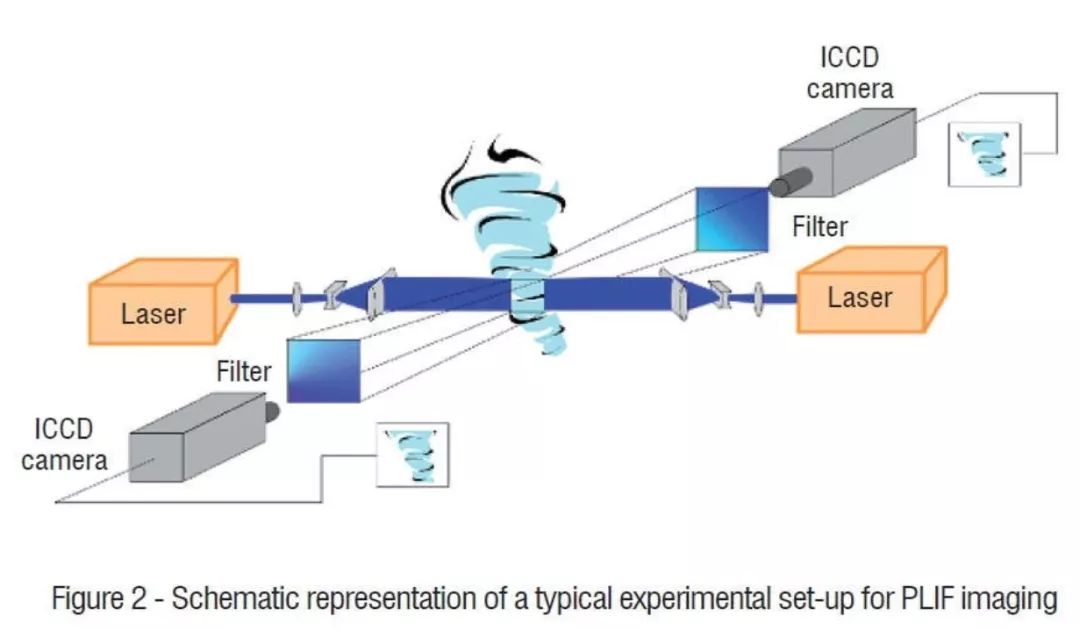

圖 1:多個組織已定義并制定了晶粒間互連標(biāo)準(zhǔn)本文將詳細(xì)探討 UCIe 規(guī)范及其主要優(yōu)勢。UCIe 是最近公布的規(guī)范,它繼承了最初發(fā)起者積累的多項(xiàng)關(guān)鍵技術(shù)方面的大量工作和經(jīng)驗(yàn),如圖 2 所示。UCIe 是一個全面的規(guī)范,可以立即用作新設(shè)計的基礎(chǔ),同時為未來的規(guī)范演變奠定堅(jiān)實(shí)的基礎(chǔ)。

圖 2:各公司攜手建立完整的標(biāo)準(zhǔn)化晶粒間互連與其他規(guī)格相反,UCIe 定義了完整的晶粒間互連堆棧,確保兼容設(shè)備的互操作性,這是實(shí)現(xiàn)多晶粒系統(tǒng)市場的必要要求。從一開始,UCIe 就包含支持多個當(dāng)前和未來用例的功能。UCIe 支持當(dāng)前所需的數(shù)據(jù)速率(從 8Gbps/引腳到 16Gbps/引腳)。UCIe 還有望支持高達(dá) 32Gbps/引腳的靈活數(shù)據(jù)速率,這將是未來高帶寬網(wǎng)絡(luò)和數(shù)據(jù)中心應(yīng)用的要求。UCIe 以兩種方式支持所有類型的封裝技術(shù):- 用于先進(jìn)封裝(硅中介層、硅橋或 RDL 扇出)的 UCIe

- 用于標(biāo)準(zhǔn)包裝(有機(jī)基材或?qū)訅喊澹┑?UCIe

兩種方式共享相同的架構(gòu)和協(xié)議。唯一的區(qū)別在于 bump map 和 PHY 組織。這種差異意味著無論為特定 SoC 選擇何種封裝類型,都可以重復(fù)使用系統(tǒng)架構(gòu)、系統(tǒng)驗(yàn)證和軟件開發(fā)。UCIe 支持?jǐn)?shù)據(jù)中心中的新型資源聚合(或匯合)架構(gòu),無論是在刀片內(nèi)配備靈活的 PCIe/CXL IO 晶粒,還是在機(jī)架到機(jī)架內(nèi)配備支持 UCIe 的光學(xué) IO 晶粒。最重要的是,UCIe 通過利用流式傳輸(用戶定義)協(xié)議,在同一封裝內(nèi)的多個服務(wù)器(或 AI)片上網(wǎng)絡(luò) (NoC) 之間創(chuàng)建低延遲連接,從而支持計算擴(kuò)展。如圖 3 所示,UCIe 規(guī)范分為三個堆棧層:物理層、晶粒間適配器層和協(xié)議層。

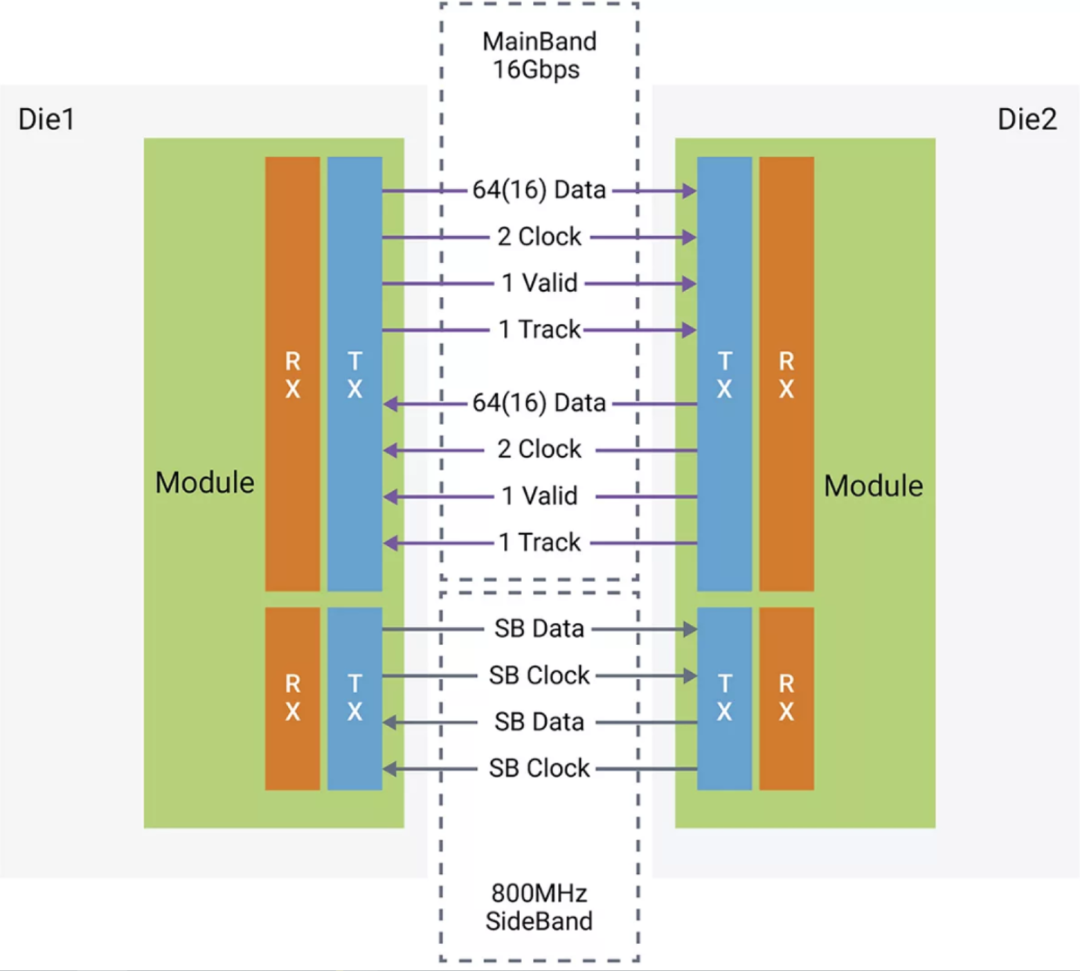

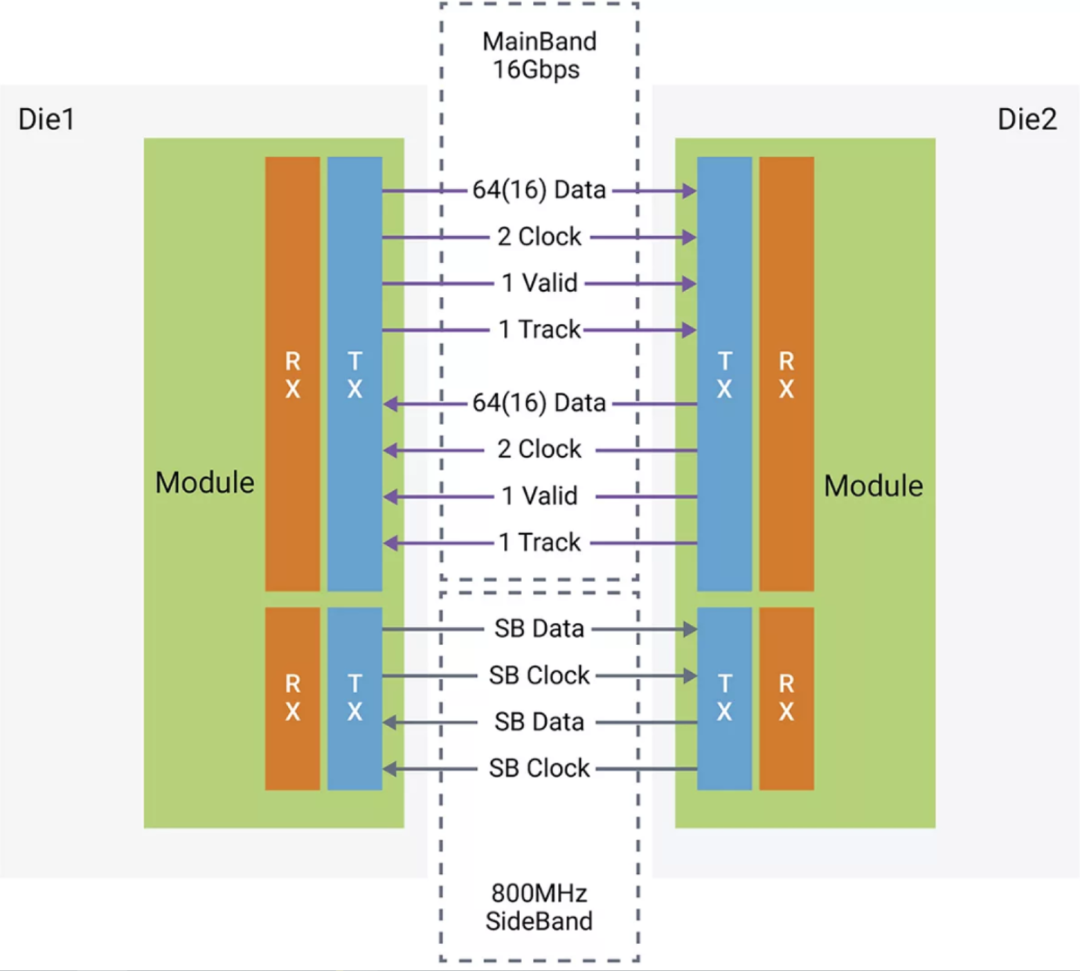

UCIe 接口使用時鐘轉(zhuǎn)發(fā)和單端、低電壓 DDR 信號來提高能耗效率。通過在 PHY 級別擾亂數(shù)據(jù),可以減少電源干擾。與其他技術(shù)(如 DBI)相反,數(shù)據(jù)擾亂不會影響帶寬效率。由于時鐘與數(shù)據(jù)并行轉(zhuǎn)發(fā),接收器數(shù)據(jù)恢復(fù)大大簡化,從而實(shí)現(xiàn)了更多的功耗節(jié)省和延遲縮短。圖 4 顯示了 UCIe PHY 架構(gòu)框圖。

UCIe 將模塊定義為最小的接口單元。每個模塊包括一個主帶“總線”,最多 64 個用于先進(jìn)封裝(或 16 個用于標(biāo)準(zhǔn)封裝)的發(fā)送和接收 IO、時鐘轉(zhuǎn)發(fā) IO、一個有效(成幀)和跟蹤 IO。邊帶“總線”的實(shí)現(xiàn)方式也如圖 5 所示。

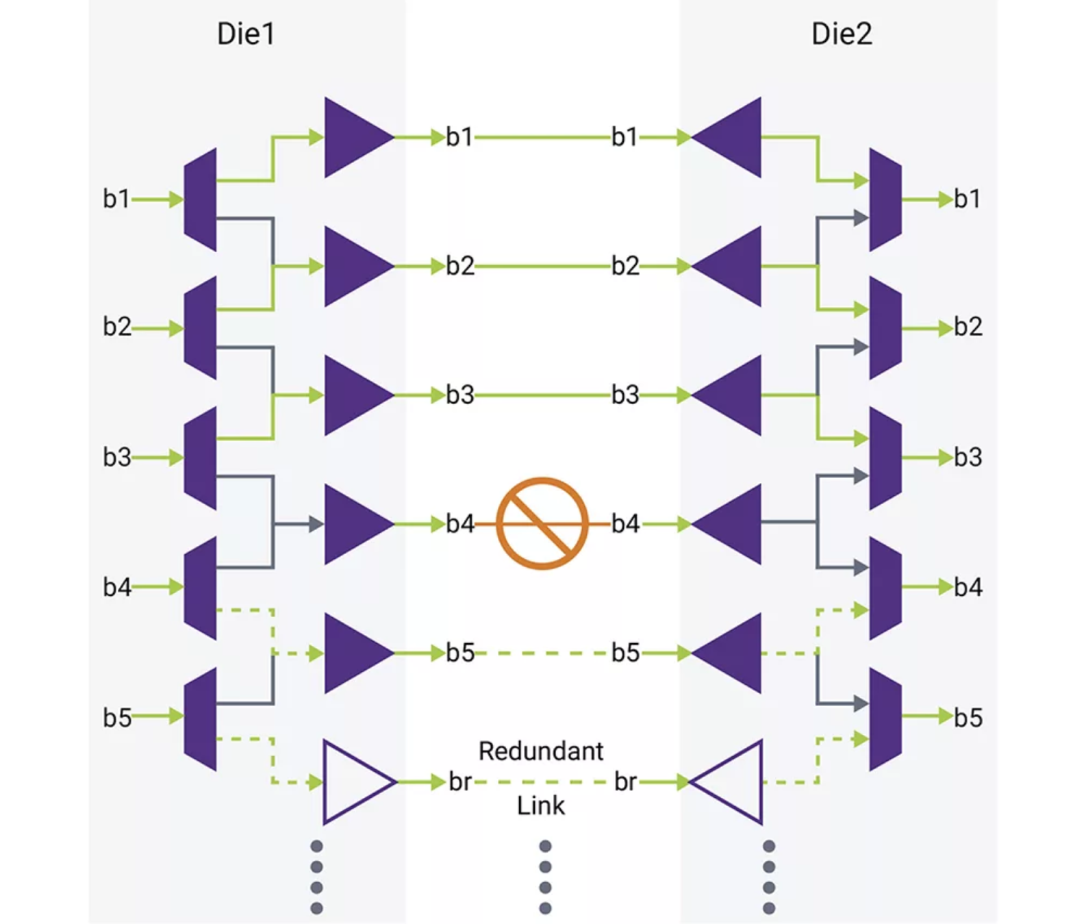

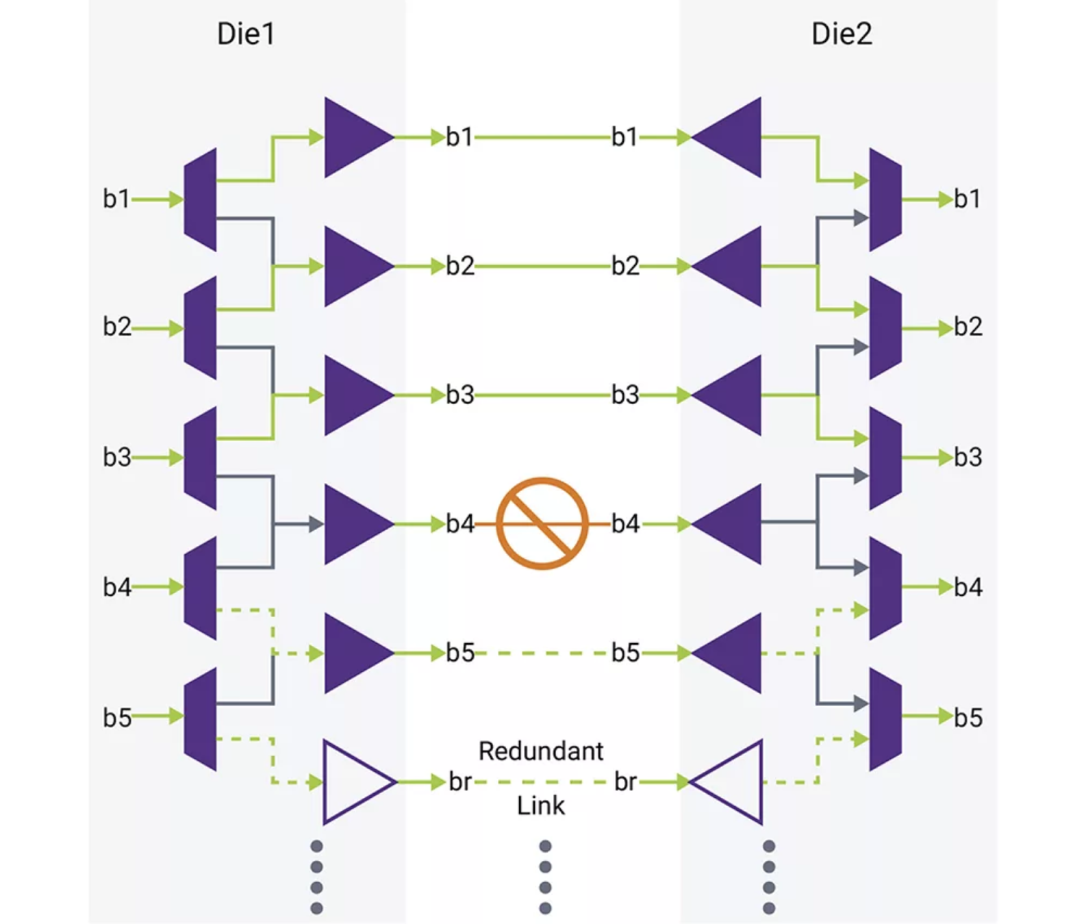

圖 5:UCIe 模塊實(shí)現(xiàn)主帶和邊帶總線為減少先進(jìn)封裝組件中由于 ubump 質(zhì)量導(dǎo)致的良率損失,UCIe 提供基于 6 個冗余引腳(用于 TX 和 RX 數(shù)據(jù)、時鐘、有效和跟蹤)和 2 個冗余引腳(用于邊帶 TX 和 RX)的測試和修復(fù)機(jī)制。由于 C4(或銅柱凸塊)凸點(diǎn)良率和完整封裝過程良率非常高,因此 UCIe 不為標(biāo)準(zhǔn)封裝實(shí)施引腳冗余。對于這些封裝,UCIe 支持“降級”操作模式,在另一半檢測到故障后,只有一半模塊處于活躍狀態(tài)。測試和修復(fù)流程在鏈路初始化時實(shí)施。PHY 測試每個晶粒連接以確定是否存在任何故障。如果發(fā)生故障,相應(yīng)的信號將重新路由到冗余引腳,如圖 6 所示。

圖 6:物理層測試每個晶粒連接以確定故障,并將信號重新路由到冗余引腳表 1 顯示了先進(jìn)封裝和標(biāo)準(zhǔn)封裝的 UCIe 規(guī)范之間的主要差異。

表 1:用于先進(jìn)封裝與標(biāo)準(zhǔn)封裝的不同 UCIe PHY 功能如前所述,這些差異僅在電氣層面上可見,并且不影響上層協(xié)議。這些差異源于標(biāo)準(zhǔn)封裝 (110u) 與先進(jìn)封裝 (45u) 所需的明顯更大的最小凸塊間距,以及源于需要在標(biāo)準(zhǔn)封裝中支持更長的信道距離以增加靈活性。晶粒間適配器層是將任何協(xié)議連接到 UCIe PHY 層的中間層。晶粒間適配器層管理鏈路本身。在鏈路初始化時,它會等待 PHY 完成鏈路初始化,包括校準(zhǔn)、測試和修復(fù),此時會啟動兩個晶粒的發(fā)現(xiàn)功能。它會商定將使用哪個協(xié)議(如果實(shí)施了多個協(xié)議)來移交給任務(wù)模式活動的協(xié)議層。晶粒間適配器層和協(xié)議層之間的接口稱為 FLIT 感知晶粒間接口 (FDI),是一種基于 FLIT 的接口。為了適應(yīng)不同的協(xié)議,它支持各種 FLIT 模式:- CXL3 256B 標(biāo)準(zhǔn) FLIT 模式

- CXL3 256B 延遲優(yōu)化 FLIT 模式

- CXL2 68B 增強(qiáng)型 FLIT 模式

流式傳輸 64B 原始模式

UCIe 還定義了 CXL 協(xié)議和 PCI Express 協(xié)議的原始模式。這些模式適用于 UCIe 流量在光纖鏈路上運(yùn)行時的重定時器應(yīng)用。在重定時器模式下,延遲和錯誤率不由 UCIe 鏈路本身定義,并且假設(shè)協(xié)議層將處理所有糾錯機(jī)制,包括 CRC、重試和可能的 FEC。晶粒間適配器層不會將 CRC 代碼添加到協(xié)議 FLIT 中,也不會檢查是否出錯或在接收器上應(yīng)用重試機(jī)制。UCIe 映射 PCI Express 和 CXL 等通用協(xié)議,這樣開發(fā)人員就能夠利用之前在軟件堆棧上的工作,并使用多晶粒架構(gòu)讓采用封裝內(nèi)集成變得更加簡單。UCIe 預(yù)計會在其未來的版本中實(shí)現(xiàn)其他協(xié)議映射的標(biāo)準(zhǔn)化。UCIe 還支持通過流模式映射其他協(xié)議。例如,在流模式下,CXS 或 AXI 橋接到 FDI 接口,支持兩個計算晶粒上的 NoC 架構(gòu)之間的低延遲連接。利用物理層和晶粒間適配器層鏈路管理功能,可以以相同的方式實(shí)施其他由用戶定義的協(xié)議。在實(shí)施 UCIe 互連時,架構(gòu)師可以選擇支持這些協(xié)議中的一個或多個。實(shí)施多個協(xié)議可增強(qiáng)晶粒在不同用例中的適用性,這在開放式多晶粒系統(tǒng)市場中具有真正的優(yōu)勢。晶粒間適配器層負(fù)責(zé)發(fā)現(xiàn)和選擇在給定互連中使用哪個協(xié)議。UCIe 規(guī)范為多晶粒 SoC 設(shè)計人員帶來了極具競爭力的性能優(yōu)勢,包括高能效 (pJ/b),高邊緣使用效率 (Tbps/mm) 和低延遲 (ns),支持最受歡迎的 IO 協(xié)議以及任何用戶定義的協(xié)議,與從有機(jī)基材到先進(jìn)硅中介層的各種封裝技術(shù)兼容,并涵蓋接口的所有關(guān)鍵方面(初始化、邊帶、協(xié)議、測試和修復(fù)、糾錯、等等)。UCIe 的優(yōu)勢使其成為一項(xiàng)非常引人注目的技術(shù),通過確保互操作性,輕松實(shí)現(xiàn)真正開放的多晶粒系統(tǒng)的生態(tài)系統(tǒng)。UCIe 發(fā)起者勾勒出了一個令人信服的路線圖,以支持行業(yè)的新用例和要求。發(fā)起者預(yù)計 UCIe 會支持更高的數(shù)據(jù)速率和新的協(xié)議、3D 封裝以及多晶粒系統(tǒng)設(shè)計的其他方面,例如外形尺寸、安全性、可測試性,等等。新思科技提供全面的多晶粒系統(tǒng)解決方案,使設(shè)計人員能夠輕松過渡到多晶粒 SoC 架構(gòu)。- 經(jīng)過硅驗(yàn)證的 IP 產(chǎn)品組合,包括接口 IP、處理器 IP、安全 IP 和測試 IP

- 適用于 UCIe 和 112G XSR 的完整晶粒間控制器和 PHY IP

- 統(tǒng)一的 3DIC 探索和設(shè)計基礎(chǔ)架構(gòu)

- 與代工廠和 OSAT 的生態(tài)系統(tǒng)協(xié)作

原文標(biāo)題:多晶粒SoC成趨勢,UCIe標(biāo)準(zhǔn)助其一臂之力

文章出處:【微信公眾號:電子發(fā)燒友網(wǎng)】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

聲明:本文內(nèi)容及配圖由入駐作者撰寫或者入駐合作網(wǎng)站授權(quán)轉(zhuǎn)載。文章觀點(diǎn)僅代表作者本人,不代表電子發(fā)燒友網(wǎng)立場。文章及其配圖僅供工程師學(xué)習(xí)之用,如有內(nèi)容侵權(quán)或者其他違規(guī)問題,請聯(lián)系本站處理。

舉報投訴

原文標(biāo)題:多晶粒SoC成趨勢,UCIe標(biāo)準(zhǔn)助其一臂之力

文章出處:【微信號:elecfans,微信公眾號:電子發(fā)燒友網(wǎng)】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

相關(guān)推薦

晶粒尺寸與晶界特征晶粒作為材料中的基本結(jié)構(gòu)單元,其尺寸和取向?qū)Σ牧系男阅苡兄钸h(yuǎn)的影響。晶粒內(nèi)部的取向相對一致,而相鄰晶粒之間則存在明顯的取

![的頭像]() 發(fā)表于

發(fā)表于 11-26 11:51

?58次閱讀

自動化測試

經(jīng)緯恒潤

發(fā)布于 :2024年11月07日 18:02:58

的核心產(chǎn)品,它可以提供計算、存儲、網(wǎng)絡(luò)等資源,承載了最基礎(chǔ)也最重要的任務(wù),性價比高、安全可靠、穩(wěn)定性強(qiáng)的云服務(wù)器,是中小企業(yè)上云、用云,加快數(shù)字化轉(zhuǎn)型的關(guān)鍵。 作為重磅推出的下一代“柔性算力”新物種,華為云

![的頭像]() 發(fā)表于

發(fā)表于 08-14 16:29

?535次閱讀

直流單臂電橋是一種用于測量電阻的儀器,它由四個標(biāo)準(zhǔn)電阻組成。 一、直流單臂電橋的工作原理 直流單臂

![的頭像]() 發(fā)表于

發(fā)表于 07-26 10:26

?617次閱讀

硬盤WD_BLACK? P40 游戲移動固態(tài)硬盤定可助父親一臂之力,輕松馳騁游戲世界。 WD_BLACK? P40 游戲移動固態(tài)硬盤 WD_BLACK P40 游戲移動固態(tài)硬盤適用于存儲

![的頭像]() 發(fā)表于

發(fā)表于 06-13 10:04

?275次閱讀

AGV行業(yè)資訊

鳳凰動力

發(fā)布于 :2024年05月22日 11:21:47

在LED照明和顯示屏行業(yè),LED透鏡和LED燈珠之間貼合的精密度和同心度直接影響著產(chǎn)品的效果。為了確保每一顆透鏡都達(dá)到貼合標(biāo)準(zhǔn)不出現(xiàn)遮光、漏光、偏光等缺陷,木幾推出了LED透鏡偏心檢測機(jī),用科技為品質(zhì)保駕護(hù)航。

![的頭像]() 發(fā)表于

發(fā)表于 03-14 13:36

?624次閱讀

作者|哪里桃小編|不吃豬頭肉一百三十多年前,奔馳夫人貝爾塔為了回?fù)羯鐣浾搶Ρ捡Y一號的質(zhì)疑,駕駛著奔馳汽車從曼海姆出發(fā),直駛104公里外的位于普福爾茨海姆的娘家,全程雖開的磕磕絆絆,但卻為汽車的宣傳

![的頭像]() 發(fā)表于

發(fā)表于 02-22 08:25

?864次閱讀

的六大熱門應(yīng)用領(lǐng)域中的燃燒領(lǐng)域。 1、為什么研究燃燒? 人類文明發(fā)展的每一步都與燃燒利用息息相關(guān),人類的文明史,就是燃燒的利用史。知道燃料的燃燒方式及原理,了解燃燒進(jìn)程,排放的污染物等,對于燃燒類的工程活動至關(guān)

![的頭像]() 發(fā)表于

發(fā)表于 02-01 06:32

?468次閱讀

成太陽能電池板。多晶硅可以將太陽光轉(zhuǎn)化為電能,并應(yīng)用于太陽能發(fā)電系統(tǒng),使之成為可再生能源的重要組成部分。 半導(dǎo)體芯片制造:多晶硅是制造集成電路芯片的主要材料之一。通過將

![的頭像]() 發(fā)表于

發(fā)表于 01-23 16:01

?8021次閱讀

再結(jié)晶后,再繼續(xù)保溫或升溫,會使晶粒進(jìn)一步長大。

![的頭像]() 發(fā)表于

發(fā)表于 01-13 11:42

?2747次閱讀

軟件

VIOOVI

發(fā)布于 :2024年01月10日 10:29:29

軟件

VIOOVI

發(fā)布于 :2023年12月25日 15:38:46

開源集市攻略 武林秘籍 開源大俠請留步! 您可是要去那赫赫有名的開源集市? 聽聞那集市門派眾多、臥虎藏龍 遂引得無數(shù)英雄紛至沓來 這里有一份武林秘籍和尋寶圖 助您一臂之力! 開源集市內(nèi)共有三十門派

![的頭像]() 發(fā)表于

發(fā)表于 12-11 22:20

?451次閱讀

Universal Chiplet Interconnect Express (UCIe) 是一個開放的行業(yè)互連標(biāo)準(zhǔn),可以實(shí)現(xiàn)小芯片之間的封裝級互連,具有高帶寬、低延遲、經(jīng)濟(jì)節(jié)能的優(yōu)點(diǎn)。

發(fā)表于 12-11 10:37

?2437次閱讀

多晶粒SoC成趨勢,UCIe標(biāo)準(zhǔn)助其一臂之力

多晶粒SoC成趨勢,UCIe標(biāo)準(zhǔn)助其一臂之力

評論