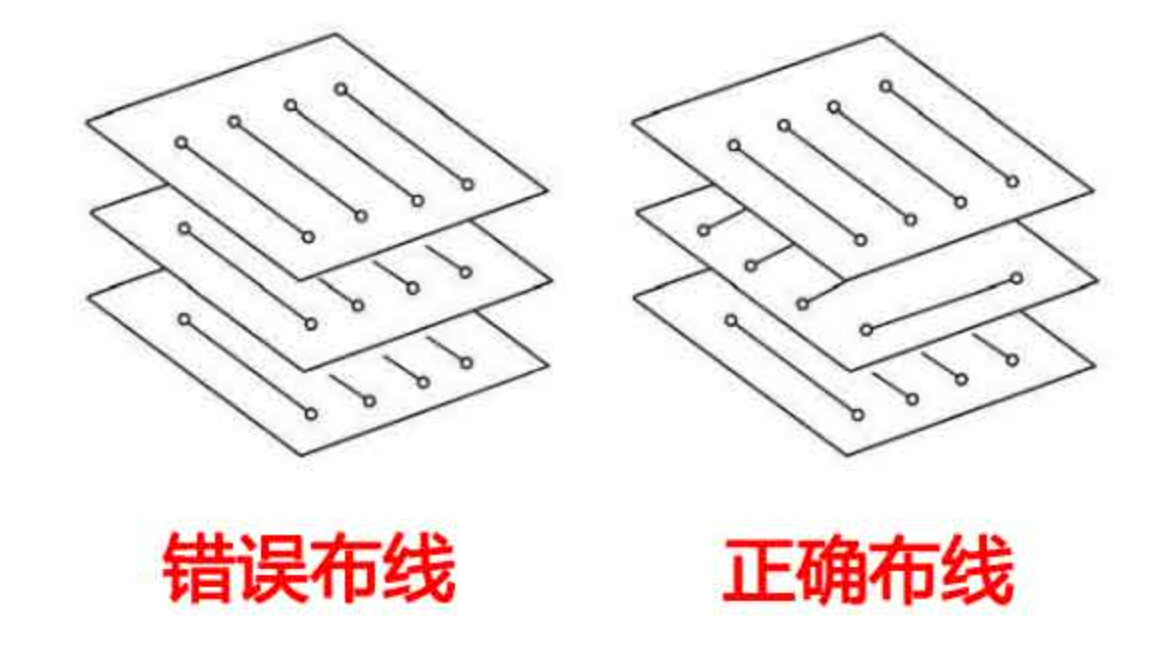

一.控制走線方向

輸入和輸出端的導(dǎo)線應(yīng)盡量避免相鄰平行。在 PCB布線時,相鄰層的走線方向成正交結(jié)構(gòu),避免將不同的信號線在相鄰層走成同一方向,以減少不必要的層間竄擾。當 PCB布線受到結(jié)構(gòu)限制(如某些背板)難以避免出現(xiàn)平行布線時,特別是在信號速率較高時,應(yīng)考慮用地平面隔離各布線層,用地線隔離各信號線。相鄰層的走線方向示意圖如下圖。

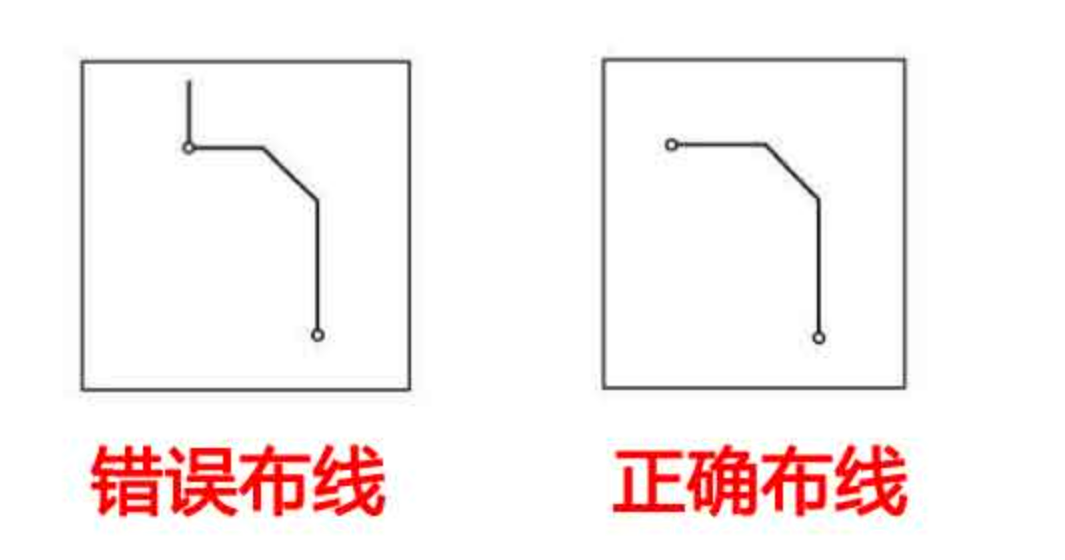

二.檢查走線的開環(huán)和閉環(huán)

在PCB布線時,為了避免布線產(chǎn)生的“天線效應(yīng)”,減少不必要的干擾輻射和接收,一般不允許出現(xiàn)一端浮空的布線形式,否則可能帶來不可預(yù)知的結(jié)果。

要防止信號線在不同層間形成自環(huán)。在多層板設(shè)計中容易發(fā)生此類問題,而自環(huán)將引起輻射干擾。

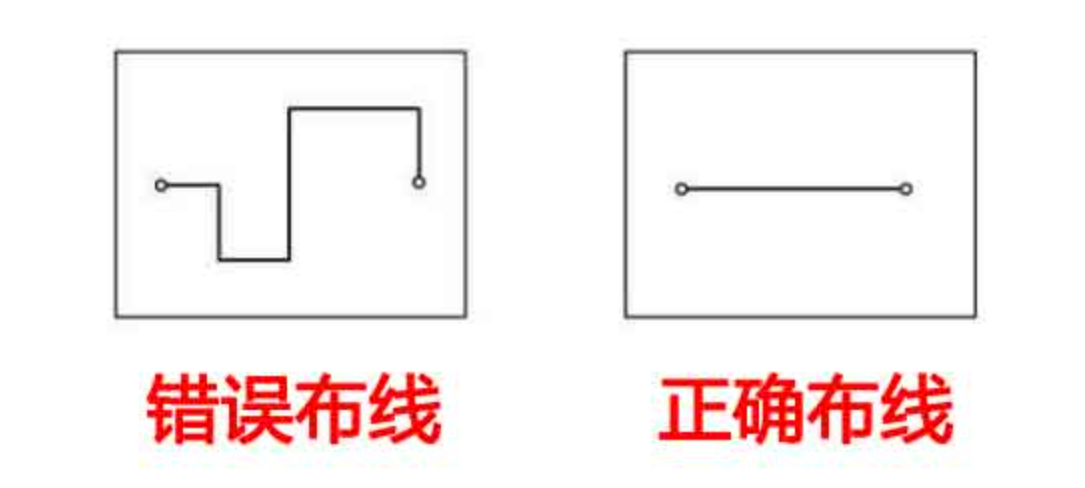

三.控制走線的長度

1.使走線長度盡可能的短

在 PCB布線時,應(yīng)該使走線長度盡可能的短,以減少由走線長度帶來的干擾問題

2.調(diào)整走線長度

數(shù)字電路系統(tǒng)對時序有嚴格的要求,為了滿足信號時序的要求,對PCB上的信號走線長度進行調(diào)整已經(jīng)成為PCB設(shè)計工作的一部分。

走線長度的調(diào)整包括以下兩個方面的要求。

a.要求走線長度保持一致,保證信號同步到達若干個接收器。有時在PCB上的一組信號線之間存在著相關(guān)性,如總線,就需要對其長度進行校正,因為需要信號在接收端同步。調(diào)整方法就是找出其中最長的那根走線,然后將其他走線調(diào)整到等長.6.控制兩個器件之間的走線延遲為某一個特定值,如控制器件A、B之間的導(dǎo)線延遲為1ns,而這樣的要求往往由電路設(shè)計者提出,但由PCB工程師去實現(xiàn)。需要注意的是,在PCB上的信號傳播速度是與PCB的材料、走線的結(jié)構(gòu)、走線的寬度、過孔等因素相關(guān)的。通過信

號傳播速度,可以計算出所要求的走線延遲對應(yīng)的走線長度。

走線長度的調(diào)整常采用的是蛇形線的方式

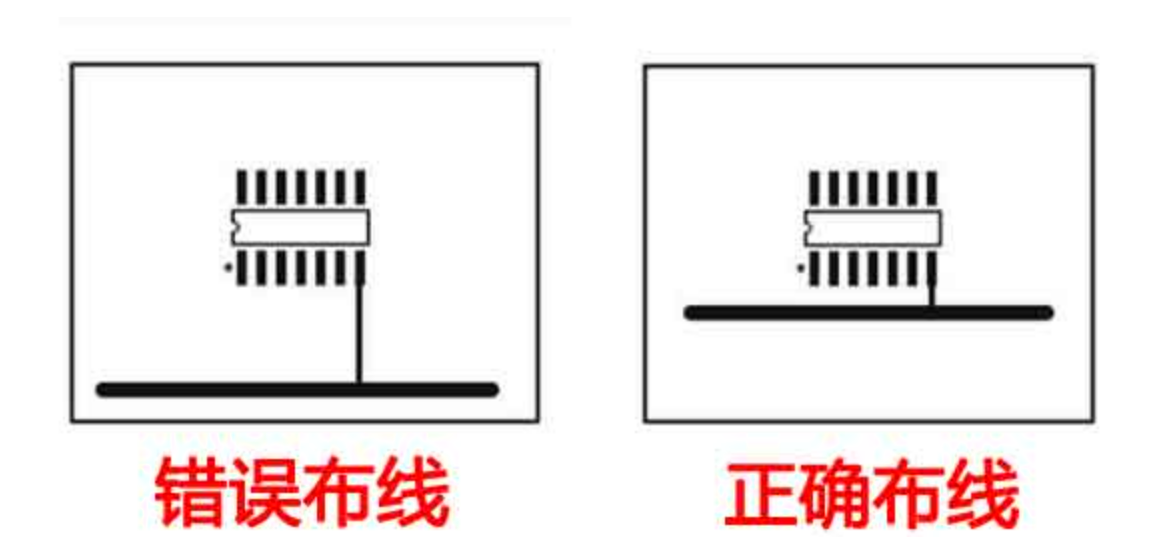

四、控制走線分支的長度

在PCB布線時,盡量控制走線分支的長度,使分支的長度盡量短,另外一般要求走線延時tdelay≤trise/20,其中trise是數(shù)字信號的上升時間。走線分支長度控制示意圖

-

pcb

+關(guān)注

關(guān)注

4317文章

23006瀏覽量

396283 -

數(shù)字電路

+關(guān)注

關(guān)注

193文章

1600瀏覽量

80498 -

華秋DFM

+關(guān)注

關(guān)注

20文章

3493瀏覽量

4376

發(fā)布評論請先 登錄

相關(guān)推薦

PCB布線規(guī)則和技巧圖解(上)

PCB布線規(guī)則和技巧圖解(上)

評論