作者:Lloben PaculananandJohn Neeko Garlitos

介紹

許多數據采集 (DAQ) 應用 需要 隔離 的 DAQ 信號 鏈 路徑, 以 實現 魯棒性、 安全性、 高 共 模 電壓, 或 消除 可能 在 測量 中 引入 誤差 的 接地 環 路。ADI公司的精密高速技術使系統設計人員能夠在相同的設計中實現高交流和直流精度,而無需犧牲直流精度來換取更高的采樣速率。但是,為了實現高交流性能,例如信噪比(SNR),系統設計人員需要考慮控制ADC中采樣保持(S&H)開關的采樣時鐘信號或轉換啟動信號抖動引入的誤差。隨著目標信號和采樣率的增加,控制S&H開關的信號抖動成為一個更主要的誤差。

當DAQ信號鏈被隔離時,用于控制S&H開關的信號通常來自背板,用于多通道同步采樣。系統設計人員必須選擇具有低抖動的數字隔離器,以便進入ADC的S&H開關的最終控制信號具有低抖動。LVDS是精密、高速ADC的首選接口格式,因為數據速率要求很高。它還對DAQ電源和接地層產生最小的干擾。本文將解釋如何解釋ADI公司LVDS數字隔離器的抖動規格,以及在連接ADAQ23875DAQ μModule解決方案等精密高速產品時哪些規格很重要。本文概述的指南適用于使用具有LVDS接口的其他精密、高速ADC。當與ADN4654千兆位LVDS隔離器配合使用時,還將在ADAQ23875的上下文中解釋計算對SNR的預期影響的方法。?

抖動如何影響采樣過程

通常,時鐘源在時域中具有抖動。在 設計 DAQ 系統 時, 了解 時鐘 源 的 抖 動 量 非常重要。

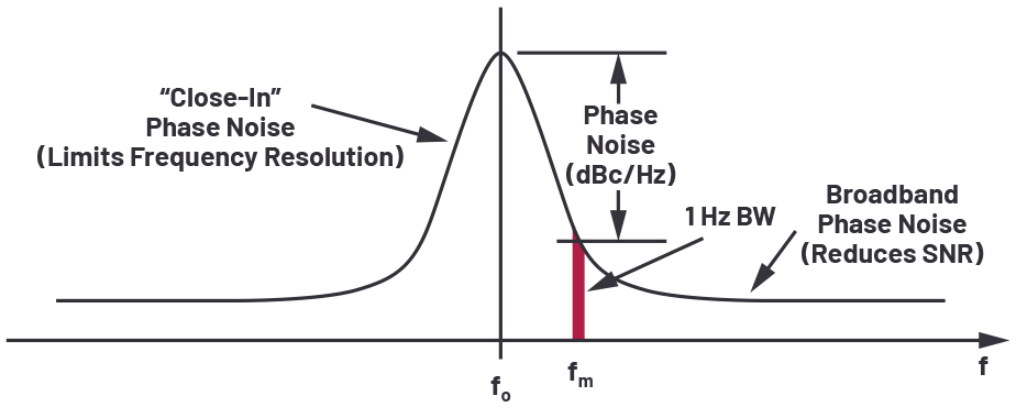

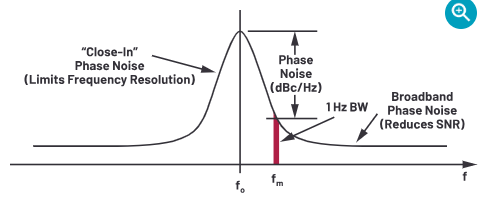

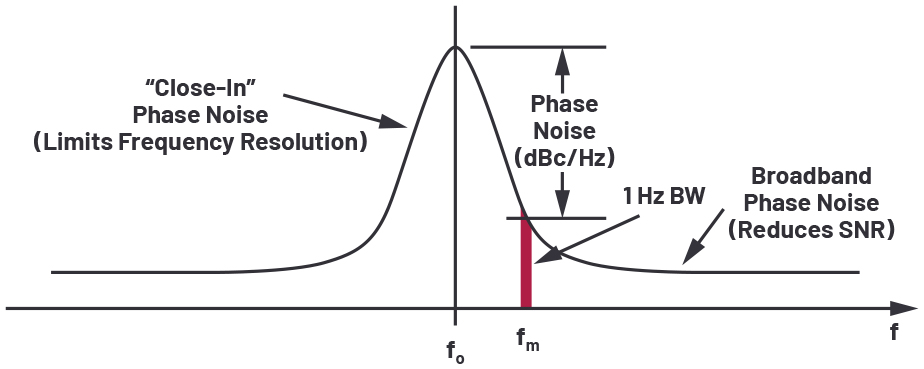

圖1顯示了非理想振蕩器的典型輸出頻譜,其噪聲功率在1 Hz帶寬內與頻率的函數關系。相位噪聲定義為指定頻率偏移下1 Hz帶寬內的噪聲之比,fm,振蕩器信號在基頻處的幅度,fo.

圖1.相位噪聲引起的振蕩器功率譜。

采樣過程是采樣時鐘和模擬輸入信號的乘法。時域中的這種乘法相當于頻域中的卷積。因此,在ADC轉換過程中,ADC采樣時鐘的頻譜與純正弦波輸入信號發生卷積,因此,采樣時鐘上的抖動或相位噪聲將出現在ADC輸出數據的FFT頻譜中,如圖2所示。

圖2.使用相位噪聲采樣時鐘對理想正弦波進行采樣的效果。

隔離式 精度、 高速 DAQ 應用

隔離式精密、高速DAQ應用的一個例子是多相功率分析儀。圖3顯示了具有通道間隔離的典型系統架構,以及用于與系統計算或控制器模塊通信的通用背板。在本例中,我們選擇了ADAQ23875精密、高速DAQ解決方案,因為它的解決方案尺寸小,便于在小尺寸中安裝多個隔離式DAQ通道,從而減輕了現場測試用例中移動儀器的重量。DAQ 通道通過 LVDS 千兆隔離器 (ADN4654) 與主機箱背板隔離。

隔離每個DAQ通道使每個通道能夠直接連接到具有明顯不同共模電壓的傳感器,而不會損壞輸入電路。每個隔離式DAQ通道的接地跟蹤具有一定電壓偏移的共模電壓。使DAQ信號鏈能夠跟蹤與傳感器相關的共模電壓,無需輸入信號調理電路來適應大輸入共模電壓,并消除下游電路的高共模電壓。隔離還為用戶提供了安全性,并消除了可能影響測量精度的接地回路。

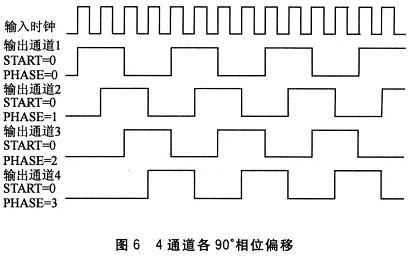

在功率分析儀應用中,跨所有DAQ通道同步采樣事件至關重要,因為與采樣電壓相關的時域信息不匹配將影響后續計算和分析。為了跨通道同步采樣事件,ADC采樣時鐘從背板通過LVDS隔離器發出。

在圖3所示的隔離式DAQ架構中,以下抖動誤差源導致控制ADC中S&H開關的采樣時鐘上的總抖動。

1. 參考時鐘抖動

采樣時鐘抖動的第一個來源是參考時鐘。該參考時鐘通過背板,連接到插入背板的每個隔離式精密高速DAQ模塊和其他測量模塊。它可作為 FPGA 的時序參考;因此,FPGA 內部所有事件、數字模塊、PLL 等的時序精度都取決于參考時鐘的精度。在一些沒有背板的應用中,板載時鐘振蕩器用作參考時鐘。

2. FPGA 抖動

采樣時鐘抖動的第二個來源是FPGA增加的抖動。重要的是要記住,FPGA內部有一個觸發到執行的路徑,FPGA內部PLL和其他數字模塊的抖動規格有助于系統的整體抖動性能。

3. LVDS隔離器抖動

采樣時鐘抖動的第三個來源是LVDS隔離器。LVDS隔離器具有附加的相位抖動,有助于提高系統的整體抖動性能。

4. ADC的孔徑抖動

采樣時鐘抖動的第四個來源是ADC的孔徑抖動。這是ADC固有的,在數據手冊中定義。

圖3.通道到通道、隔離式DAQ架構。

參考時鐘和FPGA抖動規格是根據相位噪聲給出的。為了計算采樣時鐘的抖動貢獻,需要將頻域中的相位噪聲規格轉換為時域中的抖動規格。

根據相位噪聲計算抖動

相位噪聲曲線有點類似于放大器的輸入電壓噪聲頻譜密度。與放大器電壓噪聲一樣,振蕩器中非常需要低1/f轉折頻率。振蕩器通常根據相位噪聲來指定,但要將相位噪聲與ADC性能相關聯,必須將相位噪聲轉換為抖動。為了使圖4中的圖表與現代ADC應用相關,出于討論目的,振蕩器頻率(采樣頻率)選擇為100 MHz,典型圖表如圖4所示。請注意,相位噪聲曲線由幾個單獨的線段近似,每個線段的端點由數據點定義。

圖4.根據相位噪聲計算抖動。

計算等效均方根抖動的第一步是獲得目標頻率范圍內(即曲線面積A)的積分相位噪聲功率。曲線分為幾個單獨的區域(A1、A2、A3 和 A4),每個區域由兩個數據點定義。積分的上限頻率范圍應該是采樣頻率的兩倍,假設振蕩器和ADC輸入之間沒有濾波。這近似于ADC采樣時鐘輸入的帶寬。為積分選擇較低的頻率也需要一些判斷。理論上,它應該盡可能低,以獲得真正的均方根抖動。然而,在實踐中,對于小于10 Hz左右的偏移頻率,通常不會給出振蕩器規格,但是,這肯定會在計算中給出足夠準確的結果。如果該規格可用,則在大多數情況下,100 Hz的較低集成頻率是合理的。否則,請使用 1 kHz 或 10 kHz 數據點。還應考慮近載波相位噪聲會影響系統的光譜分辨率,而寬帶噪聲會影響整個系統的SNR。可能最明智的方法是分別集成每個區域,并檢查每個區域的抖動貢獻的大小。如果使用晶體振蕩器,與寬帶貢獻相比,低頻貢獻可以忽略不計。其他類型的振蕩器可能在低頻區域具有顯著的抖動貢獻,因此必須決定它們對整體系統頻率分辨率的重要性。每個單獨區域的集成產生單獨的功率比。然后將各個功率比相加并轉換回dBc。一旦知道積分相位噪聲功率,以弧度為單位的均方根相位抖動由下式給出:

并除以 2πf0在幾秒鐘內將弧度抖動轉換為抖動:

有關更多詳細信息,請參閱“MT-008 教程:將振蕩器相位噪聲轉換為時間抖動”。

量化參考時鐘抖動

高性能DAQ系統中常用的參考時鐘是晶體振蕩器,因為與其他時鐘源相比,它提供了最佳的抖動性能。

晶體振蕩器的抖動規格通常在數據手冊中通過表1所示的示例定義。相位抖動是量化參考時鐘抖動貢獻時最重要的指標。相位抖動通常定義為邊緣位置相對于平均邊緣位置的偏差。

| 象征 | 參數 | 測試條件 | 最低 | 典型 | 最大 | 單位 | |

| J每 | 周期抖動,有效值 | LVDS | — | 三十 | — | 附言 | |

| 綠佩克利 | — | 三十 | — | ||||

| LVCMOS | f外= 125 兆赫 | — | 三十 | — | |||

| RJ | 隨機抖動,有效值 | LVDS | — | 三十 | — | 附言 | |

| 綠佩克利 | — | 三十 | — | ||||

| LVCMOS | f外= 125 兆赫 | — | 三十 | — | |||

| DJ | 確定性抖動 | LVDS | — | 三十 | — | 附言 | |

| 綠佩克利 | — | 三十 | — | ||||

| LVCMOS | f外= 125 兆赫 | — | 三十 | — | |||

| TJ | 總抖動 | LVDS | — | 三十 | — | 附言 | |

| 綠佩克利 | — | 三十 | — | ||||

| LVCMOS | f外= 125 兆赫 | — | 三十 | — | |||

| F抖動 | 相位抖動(12 kHz 至 20 MHz) | LVDS | — | 三十 | — | 司 司長 | |

| 綠佩克利 | — | 三十 | — | ||||

| LVCMOS | f外= 125 兆赫 | — | 三十 | — | |||

另一方面,有一些晶體振蕩器指定相位噪聲性能而不是抖動。如果振蕩器數據手冊定義了相位噪聲性能,則可以將其轉換為抖動,如“根據相位噪聲計算抖動”一節中所述。

量化 FPGA 的 抖動

參考時鐘在FPGA中的主要作用是提供觸發信號,以啟動FPGA內部編程的不同并行事件。換句話說,參考時鐘編排FPGA內的所有事件。為了提供更好的時序時間分辨率,參考時鐘通常被傳遞到FPGA內部的PLL以提高其頻率,因此,小時間間隔事件是可能的。同樣重要的是要知道,FPGA內部有一個觸發到執行的路徑,參考時鐘被傳遞到時鐘緩沖器、計數器、邏輯門等。在處理對抖動敏感的重復事件時,例如通過隔離向ADC提供LVDS轉換啟動信號,量化FPGA的抖動貢獻非常重要,以正確估計對整體系統抖動對高速數據采集性能的影響。

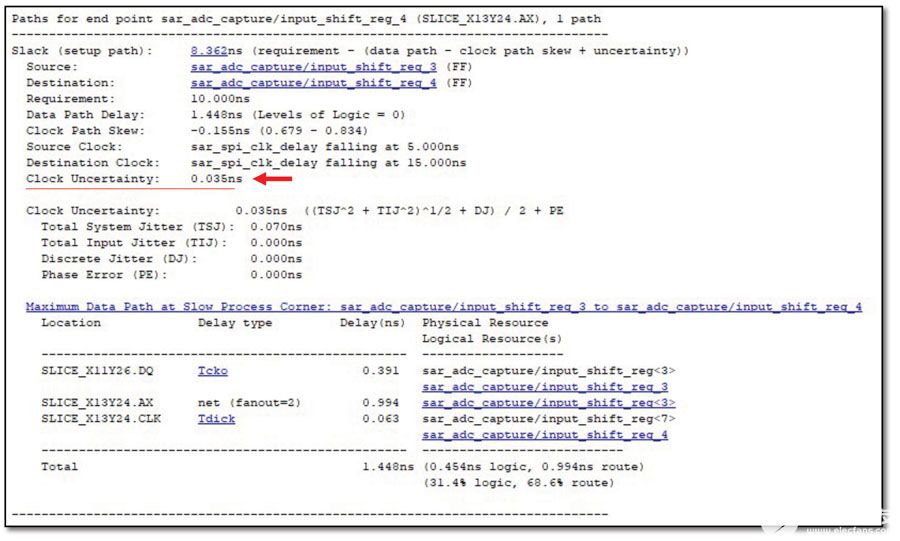

FPGA 的抖動性能通常在 FPGA 數據手冊中定義。在大多數FPGA軟件工具的靜態時序分析(STA)中也可以找到它,如圖5所示。時序分析工具可以從數據路徑的源和目標計算時鐘不確定性,并將它們組合在一起以形成總時鐘不確定性。為了自動計算STA中參考時鐘抖動的貢獻,必須在FPGA項目中將其添加為輸入抖動約束。

圖5.靜態時序分析 (STA) 示例視圖。

量化數字隔離產生的抖動

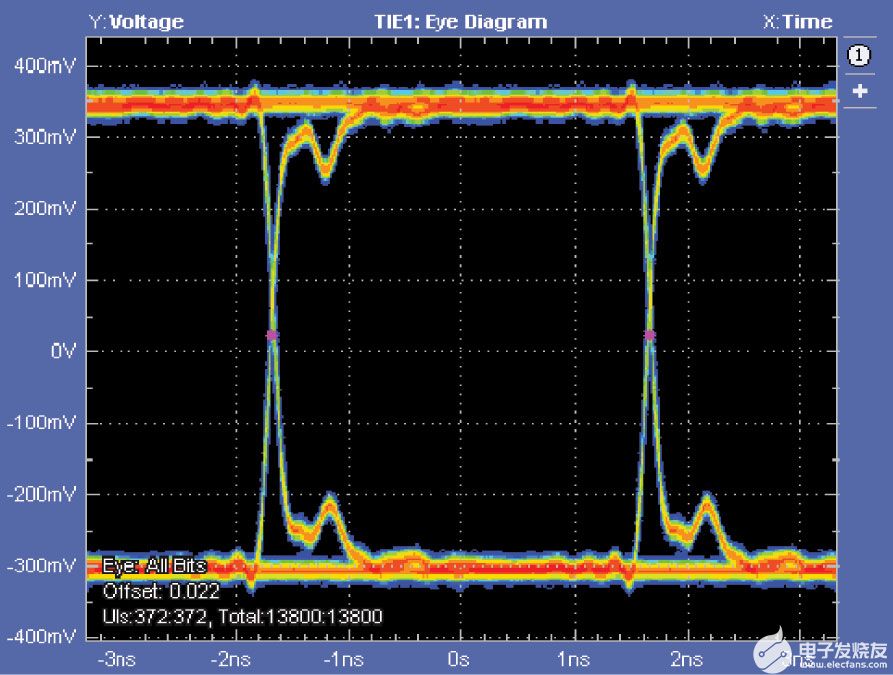

觀察抖動的最基本方法是使用差分探頭測量LVDS信號對,并在上升沿和下降沿觸發,示波器設置為無限持久性。這意味著從高到低和從低到高的轉換是疊加的,允許測量交越點。分頻器的寬度對應于迄今為止測量的峰峰值抖動或時間間隔誤差(TIE)。比較圖 6 和圖 7 中所示的眼圖和直方圖。一些抖動是由隨機源(例如,熱噪聲)引起的,這種隨機抖動(RJ)意味著示波器上的峰峰值抖動受運行時間的限制(直方圖上的尾部將隨著運行時間的增加而增長)。

圖6.ADN4651的眼圖。

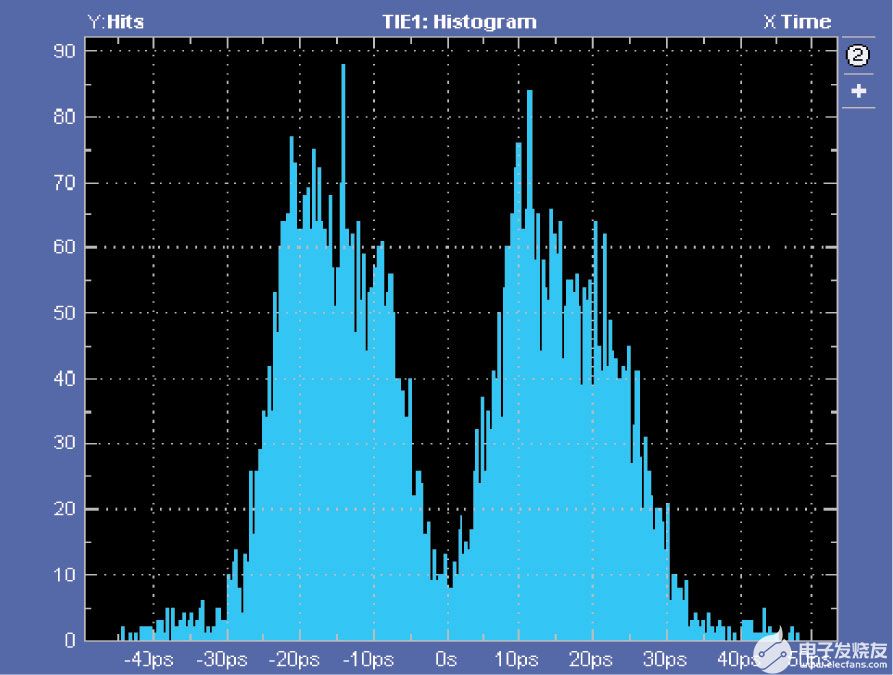

圖7.ADN4651的眼圖直方圖。

相比之下,確定性抖動 (DJ) 的來源是有界的,例如脈沖偏斜引起的抖動、數據相關抖動 (DDJ) 和碼間干擾 (ISI)。脈沖偏斜是由于高到低和從低到高的傳播延遲之間的差異引起的。這通過偏移交叉表示,在0 V時,兩個邊沿被分開(很容易從圖7直方圖中的分離中看出)。DDJ產生于工作頻率上傳播延遲的差異,而ISI是由于先前轉換頻率對電流轉換的影響(例如,在1s或0的序列與1010模式之后,邊沿時序通常會有所不同)。

圖8.總抖動貢獻。

圖8顯示了如何完全估計給定誤碼率(TJ@BER)的總抖動。RJ 和 DJ 可以根據測量中對 TIE 分布的模型擬合來計算。其中一個模型是雙狄拉克模型,它假設高斯隨機分布與雙狄拉克增量函數(對應于DJ的兩個狄拉克增量函數之間的分離)卷積。對于具有顯著確定性抖動的 TIE 分布,分布將在視覺上近似于此模型。一個復雜的問題是,一些DJ可以貢獻高斯分量,這意味著雙狄拉克模型可以低估DJ并高估RJ。但是,兩者相結合仍可準確估計給定 BER 的總抖動。

RJ 被指定為來自建模高斯分布的 1 西格瑪均方根值,這意味著要推斷到更長的運行長度(低 BER),只需選擇適當的多西格瑪以沿著分布的尾部移動足夠遠(例如,14 西格瑪表示 1 × 10-12位錯誤)。然后添加 DJ 以提供TJ@BER估計值。對于信號鏈中的多個元件,無需添加多個TJ值,因為TJ值會高估抖動,RJ值可以幾何求和,DJ值可以代數求和,從而可以對完整的信號鏈進行更合理的完整TJ@BER估計。

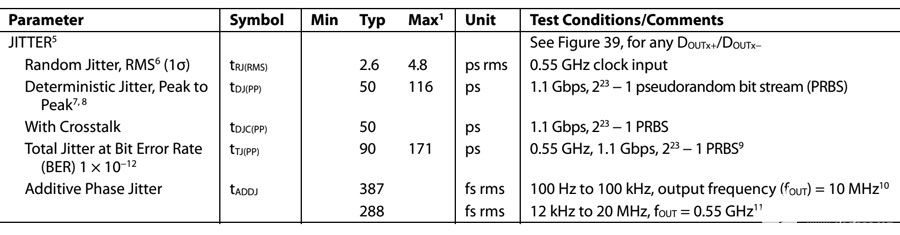

ADN4654的RJ、DJ和TJ@BER均單獨指定,根據對多個單元的統計分析,為每個單元提供最大值,以保證這些抖動值在整個電源、溫度和工藝范圍內。

圖9所示為ADN4654 LVDS隔離器的抖動規格示例。對于隔離式DAQ信號鏈,附加相位抖動是最重要的抖動規格。附加相位抖動與其他抖動源一起增加了ADC的孔徑抖動,導致采樣時間不精確。

圖9.ADN4654抖動規格

量化ADC的孔徑抖動

孔徑抖動是ADC固有的。這是由于孔徑延遲的樣本間變化,這與采樣事件中的誤差電壓相對應。這種開關打開瞬間的樣本間變化稱為孔徑不確定性或孔徑抖動,通常以均方根皮秒為單位。

在ADC中,如圖10和圖11所示,孔徑延遲時間以轉換器的輸入為基準;模擬傳播延遲通過輸入緩沖器TA的影響;以及通過開關驅動器的數字延遲,t日嘎.參考ADC輸入,孔徑時間,t一個',定義為前端緩沖器的模擬傳播延遲之間的時間差,t大,和開關驅動器數字延遲,t日嘎,加上一半的光圈時間,t一個/2.

圖 10.ADC的采樣保持輸入級。

圖 11.采樣保持波形和定義。

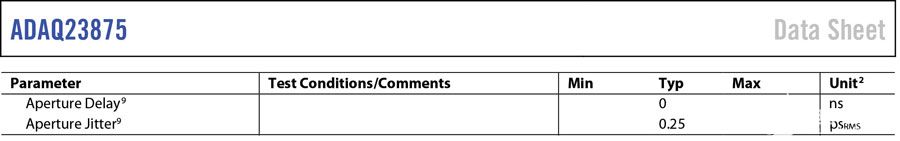

對于ADAQ23875,孔徑抖動僅為0.25 ps左右有效值如圖 12 所示。此規范由設計保證,無需測試。

圖 12.ADAQ23875孔徑抖動。

整體采樣時鐘抖動

在量化圖3所示四個主要模塊的單個抖動貢獻后,控制S&H開關的信號(或時鐘)的整體抖動性能可以通過取四個抖動源的平方根和(RSS)來計算。

另一方面,如果使用 STA,則簡化的時鐘抖動公式為:

采樣時鐘抖動對信噪比的影響

在量化了控制S&H開關的信號的整體抖動之后,我們現在可以量化該抖動對DAQ信號鏈的SNR性能的影響程度。

圖13顯示了采樣時鐘抖動引起的誤差。

圖 13.采樣時鐘抖動的影響。

采樣時鐘抖動對理想ADC信噪比的影響可以通過以下簡單分析來預測。

假設輸入信號由以下公式給出:

該信號的變化率由下式給出:

dv/dt 的均方根值可以通過除以振幅 2πfV 得到O,按 √2。現在讓 ΔV有效值= 均方根電壓誤差和 Δt = 均方根孔徑抖動 tj,并替換以下

值:

并求解 ΔV有效值:

滿量程輸入正弦波的均方根值為VO/√2.因此,均方根信號與均方根噪聲比(以dB表示)由頻率給出:

該公式假設使用無限分辨率ADC,其中孔徑抖動是決定SNR的唯一因素。該等式如圖14所示,顯示了孔徑和采樣時鐘抖動對SNR和ENOB的嚴重影響,特別是在較高的輸入/輸出下。

圖 14.理論數據轉換器SNR和ENOB由于抖動與滿量程正弦波輸入頻率的關系。

ADAQ23875和ADN4654采樣時鐘抖動理想信噪比計算

ADAQ23875的孔徑抖動為250 fs rms(典型值),而ADN4654的附加相位抖動為387 fs rms(f外= 1 兆赫)。在這種情況下,我們暫不考慮參考時鐘和FPGA的抖動貢獻。

現在,根據ADC和隔離器的抖動規格,我們可以通過以下方式計算總均方根抖動:

圖 14 和 15 顯示了 隔離 式 精密 高速 DAQ 系統 計算 出 的 最大 SNR 和 ENOB 性能。SNR和ENOB隨輸入頻率而降低,這與圖13中理論SNR圖中的曲線一致。

圖 15.ADAQ23875和ADN4654計算的最大信噪比。

圖 16.ADAQ23875和ADN4654的最大計算ENOB。

結論

控制ADC中S&H開關的信號(或時鐘)抖動會影響精密、高速DAQ信號鏈的SNR性能。在選擇時鐘信號鏈中的各種元件時,了解導致整體抖動的誤差源非常重要。

當應用需要將DAQ信號鏈與背板隔離時,選擇具有低附加抖動的數字隔離器對于保持最佳SNR性能至關重要。ADI具有低抖動LVDS隔離器,使系統級設計人員能夠在隔離式信號鏈架構中實現高SNR性能。

參考時鐘是采樣時鐘抖動的第一個來源,使用低抖動參考時鐘對于實現隔離式高速DAQ的最佳性能非常重要。確保FPGA和參考時鐘之間路徑的信號完整性也很重要,以避免路徑本身產生額外的誤差。

審核編輯:郭婷

-

adc

+關注

關注

98文章

6452瀏覽量

544147 -

DAQ

+關注

關注

6文章

91瀏覽量

32157 -

SNR

+關注

關注

3文章

195瀏覽量

24374

發布評論請先 登錄

相關推薦

計算隔離式精密高速DAQ的采樣時鐘抖動的簡單步驟

【數據采集分享】基于LABVIEW的USB接口高速數據采集的設計

時鐘分配芯片在高速并行數據采集中的應用

開源硬件-TIDA-01037-最大程度提升 SNR 和采樣速率的 20 位、1MSPS 隔離器優化型數據采集 PCB layout 設計

開源硬件-TIDA-01035-為最大程度提升 SNR 和采樣速率而優化抖動的 20 位隔離式數據采集 PCB layout 設計

計算隔離式精密高速DAQ的采樣時鐘抖動的簡單步驟分享

計算隔離式精密高速DAQ的采樣時鐘抖動的簡單步驟

計算隔離式精密高速數據采集的采樣時鐘抖動的簡單步驟

計算隔離式精密高速數據采集的采樣時鐘抖動的簡單步驟

評論