作者:John Martin Dela Cruz and Patrick Errgy Pasaquian

在本電源系統優化系列的第1部分中,我們研究了如何量化電源噪聲靈敏度,以及如何將這些量與信號鏈中的實際效應聯系起來。有人問:實現高性能模擬信號處理器件卓越性能的真正噪聲限值是多少?噪聲只是設計配電網絡(PDN)的一個可測量參數。如第1部分所述,僅僅關注最小化噪聲可能會以尺寸增加、成本增加或效率降低為代價。優化配電網絡可以改善這些參數,同時將噪聲降低到必要的水平。

本文基于對高性能信號鏈中電源紋波影響的概括性概述。在這里,我們將深入探討優化高速數據轉換器配電網絡的細節。

我們將標準 PDN 與優化的 PDN 進行比較,以了解在空間、時間和成本方面可以獲得哪些收益。后續文章將探討針對其他信號鏈器件(如RF收發器)的具體優化解決方案。

AD9175雙通道12.6 GSPS高速數模轉換器的電源系統優化

AD9175是一款高性能、雙通道、16位數模轉換器(DAC),支持高達12.6 GSPS的DAC采樣速率。該器件具有 8 通道、15.4 Gbps JESD204B 數據輸入端口;高性能片內DAC時鐘乘法器;以及針對單頻段和多頻段直接到射頻 (RF) 無線應用的數字信號處理能力。

圖1.AD9175高速DAC的標準PDN,現成的評估板提供。

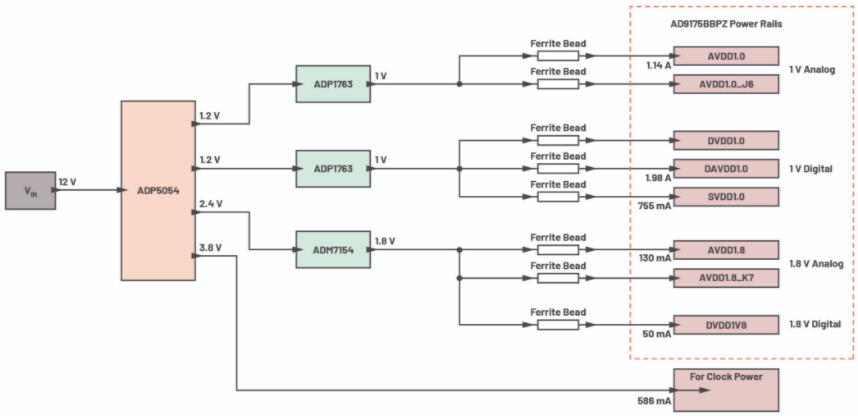

讓我們看一下如何優化此雙通道高速DAC的PDN。圖1顯示了安裝在現成評估板上的高速DACAD9175的標準配電網絡。PDN包括一個分立式四通道開關ADP5054和三個低壓差(LDO)后置穩壓器。目標是看看是否可以改進和簡化該PDN,同時確保其輸出噪聲不會導致DAC性能的任何顯著下降。

AD9175需要8個電源軌,可分為4組,即:

1 V 模擬(雙軌)

1 V 數字(三軌)

1.8 V 模擬(雙軌)

1.8 V 數字(單軌)

分析:噪聲要求

在進行任何優化之前,我們必須了解這些電源軌的電源靈敏度。我們將重點介紹模擬電源軌,因為它們往往比數字電源軌對噪聲更敏感。

模擬電源軌的電源調制比(PSMR)如圖2所示。請注意,1 V模擬電源軌在1/f頻率區域相對更敏感,而1.8 V模擬電源軌在開關轉換器工作頻率范圍(100 kHz至1 MHz左右)更敏感。

圖2.AD9175高速DAC PSMR,采用1 V模擬和1.8 V模擬電源軌。

優化的一種方法是使用帶有LC濾波器的低噪聲開關穩壓器。圖 3 顯示了在擴頻頻率調制 (SSFM) 模式關閉的情況下,LT8650S 靜音開關穩壓器穩壓器(帶或不帶 LC 濾波器)的傳導頻譜輸出。如第1部分所述,SSFM降低了開關頻率噪聲幅度,但由于三角調制頻率,在1/f區域引入了噪聲峰值。增加的噪聲將超過該電源軌的最大允許紋波閾值,因為1/f噪聲已經與該閾值有很小的裕量。因此,在這種情況下不建議使用 SSFM。最大允許電壓紋波閾值表示電源紋波電平,超過該電平時,DAC載波信號中的邊帶雜散高于DAC輸出頻譜的1 μV p-p本底噪聲。?

從這些結果可以看出,開關穩壓器的1/f噪聲不超過1 V模擬軌的最大允許紋波閾值。此外,一個LC濾波器足以將LT8650S的基波開關紋波和諧波降到最大允許紋波門限以下。

圖3.LT8650S傳導頻譜輸出與1 V模擬軌的最大允許紋波閾值的關系。

圖4顯示了LT8653S的傳導光譜輸出(帶和不帶LC濾波器)。圖中還顯示了1.8 V電源軌的最大允許電壓紋波,該紋波不會在AD9175輸出頻譜的1 μV p-p本底噪聲中產生雜散。可以看出,LT8653S的1/f噪聲不超過最大允許紋波閾值,LC濾波器足以將LT8653S的基波開關紋波和諧波降到最大允許紋波閾值以下。

圖4.LT8653S傳導頻譜輸出與1.8 V模擬軌的最大允許紋波閾值的關系。

結果:優化的 PDN

圖5顯示了AD9175的優化配電網絡。目標是在實現AD9175出色的動態性能的同時,通過圖1所示的PDN提高效率,降低空間要求和功耗。噪聲目標基于圖3和圖4所示的最大允許紋波閾值。

優化的配電網絡由 LT8650S 和 LT8653S 靜音開關穩壓器組成,后跟模擬電源軌上的 LC 濾波器。在此 PDN 中,1 V 模擬電源軌由 V 供電輸出1LT8650S,后接一個LC濾波器;1 V 數字電源軌直接由 V 供電輸出2相同的LT8650S,無需LC濾波器。對于AD9175,數字電源軌對電源噪聲不太敏感,因此可以直接為這些供電軌供電,而不會降低DAC動態性能。帶LC濾波器的LT8653S直接為1.8 V模擬和1.8 V數字電源軌供電。

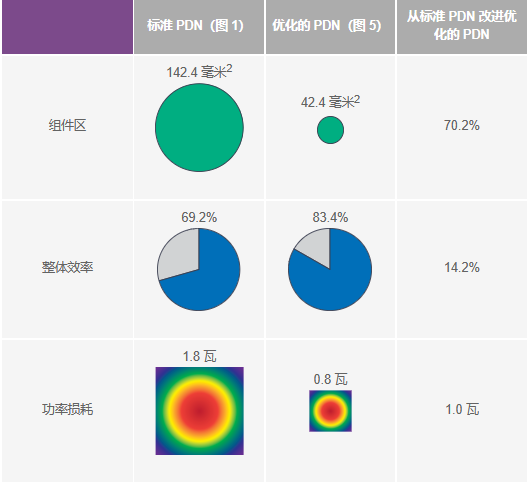

表 1 將優化后的 PDN 的性能與圖 1 所示的標準 PDN(帶有三個 LDO 穩壓器的四通道降壓開關)進行了比較。優化解決方案的組件面積比標準減少了70.2%。此外,效率從69.2%提高到83.4%,整體功耗節省1.0 W。

圖5.針對AD9175高速DAC的優化PDN。

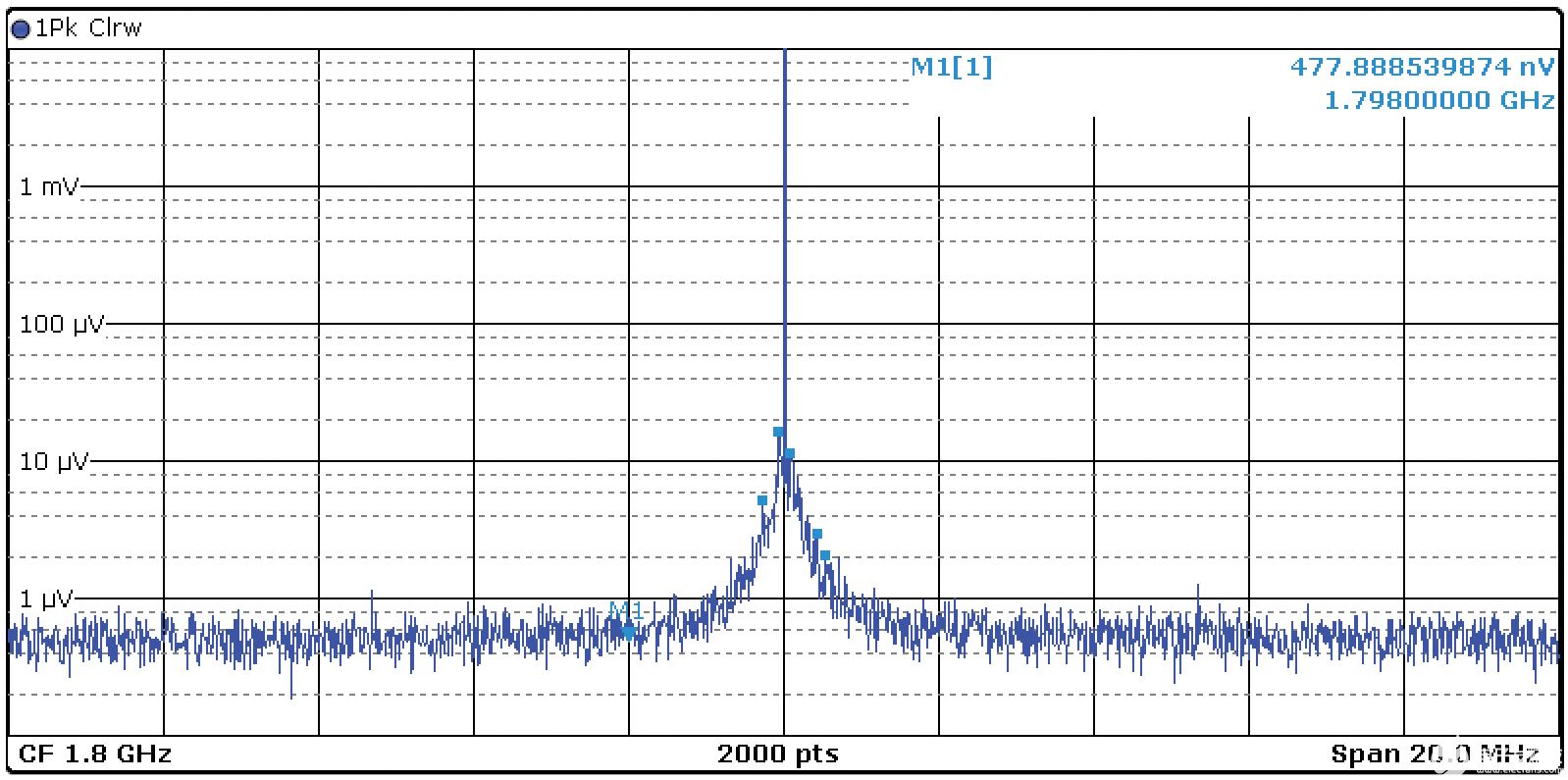

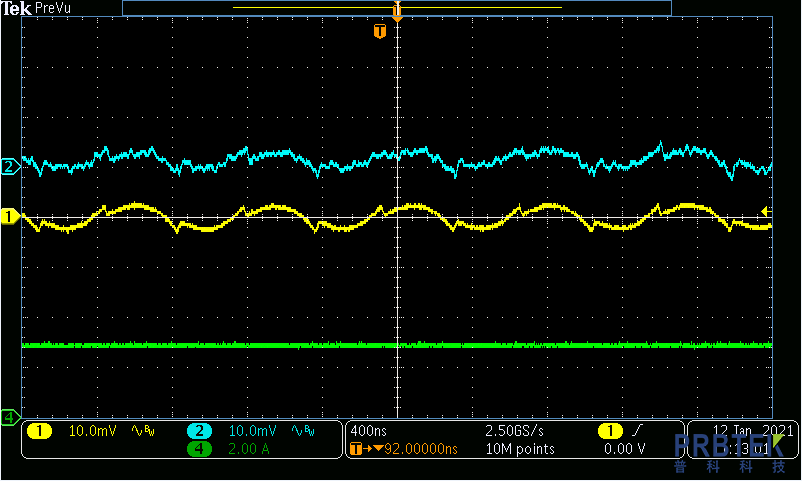

為了驗證優化后的PDN的噪聲性能是否足以滿足高性能規格,對AD9175進行了相位噪聲評估,并檢查了載波周圍邊帶雜散的DAC輸出頻譜。1標準PDN和優化PDN之間的相位噪聲結果相當,如表2所示。AD9175的輸出頻譜具有干凈的載波頻率,沒有可見的邊帶雜散,如圖6所示。

圖6.AD9175輸出頻譜(1.8 GHz,–7 dBFS載波),采用優化的PDN。

| 頻率偏移 | 相位噪聲 (dBc/Hz) | ||||

| 標準 PDN(圖 1) | 優化的 PDN(圖 5) | ||||

| DAC0 | 數字轉換器1 | DAC0 | 數字轉換器1 | ||

| 1.0千赫 | –91 | –91 | –91 | –91 | |

| 10.0千赫 | –99 | –99 | –99 | –99 | |

| 100.0千赫 | –110 | –110 | –110 | –110 | |

| 600.0千赫 | –125 | –125 | –125 | –125 | |

| 1.2兆赫 | –134 | –134 | –134 | –134 | |

| 1.8兆赫 | –137 | –137 | –137 | –137 | |

| 6.0兆赫 | –148 | –148 | –148 | –148 | |

AD9213 10.25 GSPS高速模數轉換器的電源系統優化

AD9213是一款單通道、12位、6 GSPS或10.25 GSPS射頻(RF)模數轉換器(ADC),輸入帶寬為6.5 GHz。AD9213支持需要寬瞬時帶寬和低轉換錯誤率(CER)的高動態范圍頻域和時域應用。AD9213具有16通道JESD204B接口,支持最大帶寬能力。

圖7顯示了AD9213高速ADC的標準配電網絡(如現成的評估板上所示),由一個LTM4644-1 μModule四通道開關器和兩個線性穩壓器組成。該解決方案相當節省空間和能源效率,但可以改進嗎?如本系列文章所述,優化的第一步是量化AD9213的靈敏度,即實際設置PDN輸出噪聲限值,以免顯著降低ADC性能。在這里,我們將介紹使用兩個μModule穩壓器的替代PDN解決方案,并將其性能與標準現成解決方案進行比較。?

AD9213 10 GSPS ADC需要15個不同的電源軌,分為四組:

1 V 模擬(三軌)

1 V 數字(6 軌)

2 V 模擬(雙軌)

2 V 數字(四軌)

圖7.AD9213高速ADC的標準PDN,現成的評估板提供。

分析:噪聲要求

我們正在探索的優化解決方案是用兩個μModule穩壓器(LTM8024和LTM8074)以及單個LDO后置穩壓器取代一個LTM4644-1 μModule四通道開關穩壓器和兩個線性穩壓器。

圖8.AD9213高速ADC PSMR,1 V模擬和2 V模擬軌,載波頻率為2.6 GHz。

圖8顯示了AD9213在2.6 GHz載波頻率下1 V模擬和2 V模擬電源軌的PSMR結果。由于PSMR較低,1 V模擬軌比2 V模擬軌更敏感。

圖 9 示出了 LTM8024 (帶和不帶 LDO 穩壓器) 在強制連續模式 (FCM) 下的頻譜輸出。圖中還顯示了最大允許電壓紋波閾值的疊加圖,該閾值不會在AD9213輸出頻譜的–98 dBFS本底噪聲中產生雜散。當直接為1 V模擬電源軌供電時,LTM8024輸出的未濾波1/f噪聲和基波開關雜散超過允許的最大紋波閾值。

向 LTM8024 添加一個 ADP1764 LDO 后置穩壓器可將 1/f 噪聲和基波開關紋波及其諧波降至最大允許紋波門限,如圖 9 所示。線性穩壓器的輸入端需要一定的開銷電壓。在這種情況下,LTM8024使用1.3 V輸出至后置穩壓器的輸入端。該300 mV符合LDO穩壓器推薦的裕量電壓規格,同時最大限度地降低其中的功率損耗;這比標準解決方案中的500 mV略好。

圖9.LTM8024頻譜輸出與1 V模擬電源軌的最大允許紋波閾值的關系。

解決2 V電源軌問題:圖10顯示了采用FCM封裝的LTM8074 μModule穩壓器(帶或不帶LC濾波器)的頻譜輸出。還顯示了最大允許電壓紋波閾值。該閾值表示電源紋波電平,超過該閾值時,ADC載波信號中的邊帶雜散高于AD9213輸出頻譜的–98 dBFS本底噪聲。這里,與1 V模擬軌類似,穩壓器開關雜散在直接為2 V模擬軌供電時超過最大允許紋波閾值。不過,不需要LDO穩壓器。相反,LTM8074 輸出端上的一個 LC 濾波器將開關雜散降低到允許的最大紋波門限以下。

圖 10.LTM8074頻譜輸出與2 V模擬軌的最大允許紋波閾值的關系

結果:優化的 PDN

圖11顯示了根據電源靈敏度評估結果優化的配電網絡。與標準解決方案一樣,它使用三個電源IC;在本例中,LTM8024、LTM8074 和 ADP1764。在此解決方案中,LTM8024 μModule 穩壓器 V輸出1由ADP1764進行后置穩壓,為相對敏感的1 V模擬電源軌供電。1 V 數字電源軌直接由 V 供電輸出2的 LTM8024。與AD9175 DAC非常相似,AD9213的數字供電軌對電源噪聲不太敏感,因此可以直接為這些供電軌供電,而不會降低ADC動態性能。帶有LC濾波器的LTM8074為2 V模擬和2 V數字電源軌供電。

圖 11.針對AD9213高速ADC的優化PDN。

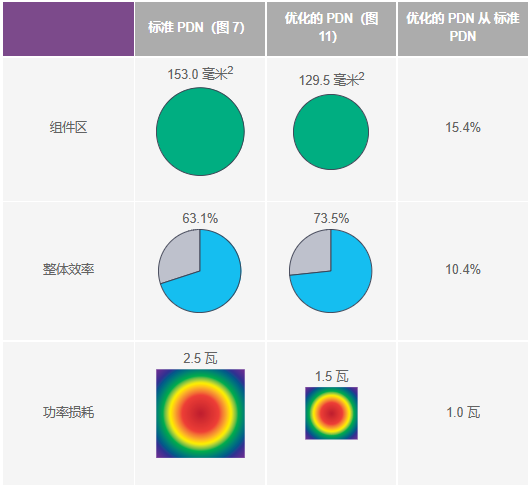

表 3 將優化后的 PDN 的性能與標準的現成 PDN 進行了比較。如圖7所示,標準PDN使用帶有兩個LDO穩壓器的四通道降壓開關。組件面積減少15.4%,效率從63.1%提高到73.5%,整體功耗節省1.0W。

為了驗證優化后的PDN的性能,對AD9213進行了SFDR和SNR評估,并通過檢查載波周圍邊帶雜散的FFT輸出頻譜。SNR和SFDR性能顯示的結果在數據手冊規格限值范圍內,如表4所示。圖12顯示了AD9213的FFT輸出頻譜,具有干凈的載波頻率,沒有可見的邊帶雜散。

| 模數轉換器參數 | 評價結果 | 數據表規格 | ||

| 最小值 | 典型值 | 麥克斯 | ||

| 信噪比 (dBFS) | 52.6 | 50.1 | 52.3 | — |

| SFDR (dBFS) | 72.0 | 60.0 | 76.0 | — |

圖 12.AD9213(2.6 GHz,–1 dBFS載波)的FFT頻譜,使用圖11所示的優化PDN。

結論

用于高性能數據轉換器的現成評估板設置了配電網絡,旨在滿足這些信號處理IC的噪聲要求。即使在評估板的設計中進行了仔細考慮,配電網絡仍有改進的余地。在這里,我們研究了兩個PDN:一個用于高速DAC,另一個用于高速ADC。與標準 PDN 相比,我們在空間要求、效率和特別重要的熱性能方面進行了改進。可以通過替代設計或當前不可用的設備對某些參數進行進一步改進。請繼續關注本電源系統優化系列的更多條目,包括射頻收發器的PDN優化。

審核編輯:郭婷

-

電源

+關注

關注

184文章

17574瀏覽量

249483 -

收發器

+關注

關注

10文章

3393瀏覽量

105860 -

dac

+關注

關注

43文章

2269瀏覽量

190834

發布評論請先 登錄

相關推薦

基于對高性能信號鏈中電源紋波影響的概括性概述

基于對高性能信號鏈中電源紋波影響的概括性概述

評論