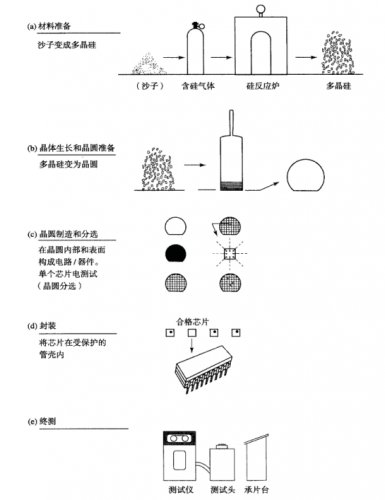

半導(dǎo)體集成電路是將很多元件集成到一個(gè)芯片內(nèi), 以處理和儲(chǔ)存各種功能的電子部件。而芯片制造主要分為5個(gè)階段:材料制備、晶體生長(zhǎng)或晶圓制備、晶圓制造和分揀、封裝、終測(cè)。如下圖所示:

半導(dǎo)體生產(chǎn)階段

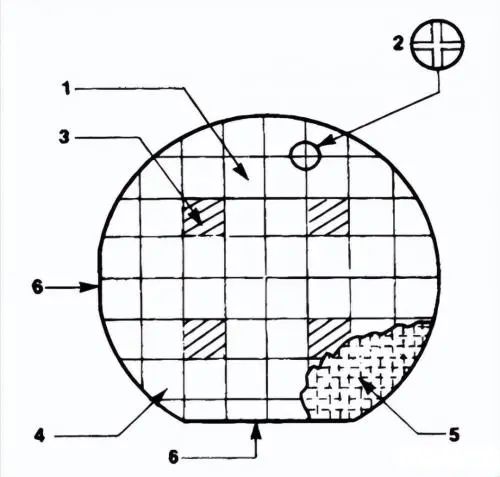

半導(dǎo)體集成電路是在晶圓的薄基板的基礎(chǔ)上,通過制造多個(gè)相同電路而產(chǎn)生的。如同制作披薩時(shí)添加配料之前先做面團(tuán)一樣,晶圓作為半導(dǎo)體的基礎(chǔ),是指將硅(Si)、砷化鎵(GaAs)等生成的單晶柱切成薄片的圓盤。本文就將講述晶圓制造的相關(guān)基礎(chǔ)知識(shí)。晶圓制造(wafer fabricaTIon)是在晶圓表面上或表面內(nèi)制造出半導(dǎo)體器件的一系列生產(chǎn)過程。正文開始前,首先介紹一些晶圓術(shù)語(yǔ),以方便后續(xù)理解。

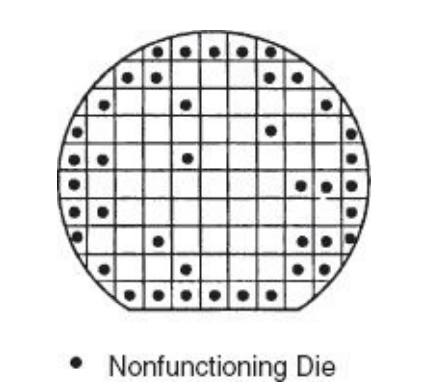

?芯片(chip、die)、器件(device)、電路(circuit)、微芯片(microchip)或條碼(bar):所有這些名詞都是指占大部分面積的微芯片圖形。

?劃片線(scribe line、saw line)或街區(qū)(street、avenue):晶圓上用來(lái)分隔不同芯片的間隔區(qū)。劃片區(qū)通常是空白的,但有時(shí)也會(huì)在間隔區(qū)放置對(duì)準(zhǔn)標(biāo)記(十字mark)或測(cè)試結(jié)構(gòu)(testkey)。

?工程試驗(yàn)芯片(engineering die)和測(cè)試芯片(test die):這些芯片與正式芯片不同,它主要用于對(duì)晶圓生產(chǎn)工藝單額電性能測(cè)試監(jiān)控。

?邊緣芯片(edge die):晶圓邊緣殘缺的芯片。這部分芯片占比越高產(chǎn)生的損耗就越大,晶圓尺寸增大可以減小邊緣芯片的比例。

?晶圓的晶面(wafer crystal plane):晶格方向,與器件的方向是相關(guān)的。

?晶圓定位邊(wafer flat/notche):分主定位邊(major flat)和副定位邊(minor flat),如下圖定位邊表示這是一個(gè)P型<100>晶相的晶圓。

芯片制造工藝

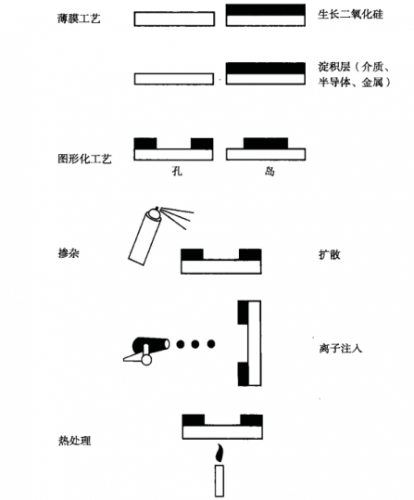

芯片制造主要根據(jù)薄膜工藝、圖形化工藝、摻雜和熱處理4個(gè)基本的工藝步驟來(lái)生產(chǎn)出特定的器件。

晶圓制造基本工藝

薄膜工藝

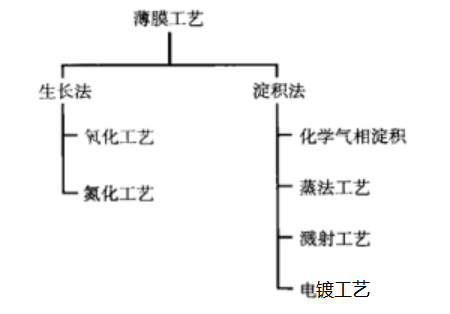

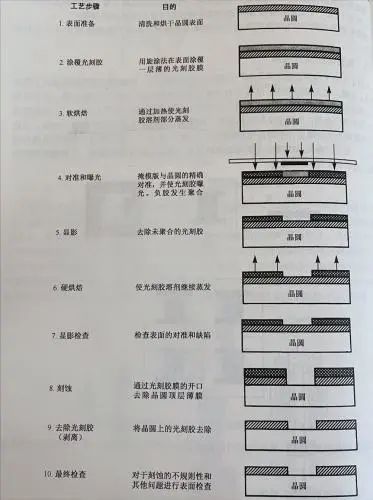

薄膜工藝(layering)是在晶圓表面形成薄膜的加工工藝。在芯片制造過程中,需要在晶圓表面形成各種各樣的薄膜。這些薄膜可以是絕緣體、半導(dǎo)體或者半導(dǎo)體,它們由不同材料使用多種工藝技術(shù)生長(zhǎng)或沉積而成。

薄膜工藝

以下列舉了薄膜制備的工藝分類和工藝與材料的對(duì)照表。

薄膜工藝分類

工藝與材料對(duì)照表

圖形化工藝

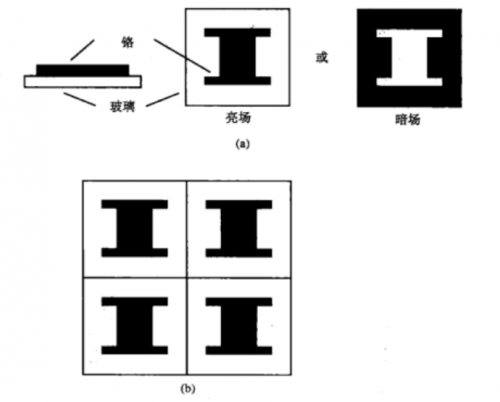

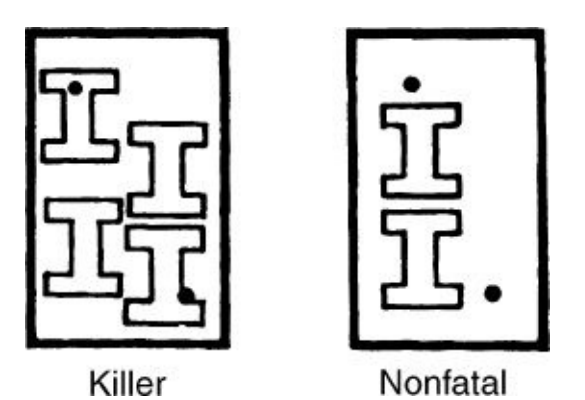

圖形化工藝(patterning)是通過一系列步驟將晶圓表面薄膜的特定部分去除以形成特定圖形的工藝。圖形化工藝的目標(biāo)是根據(jù)設(shè)計(jì)需要在晶圓上形成尺寸精確的特征圖形,在晶圓上的位置要正確且與其他關(guān)聯(lián)層的關(guān)聯(lián)也要正確。圖形化工藝也被廣泛稱為光掩模(photomasking)、掩模(masking)、光刻(photolithography)。

圖形化工藝是4個(gè)基本工藝步驟中最關(guān)鍵的,其確定了器件的關(guān)鍵尺寸。圖形化工藝過程的錯(cuò)誤可能會(huì)導(dǎo)致圖形的歪曲或套準(zhǔn)不好,最終對(duì)器件的電性能產(chǎn)生影響。圖形化工藝在現(xiàn)代晶圓生產(chǎn)過程中要完成30層或更多。

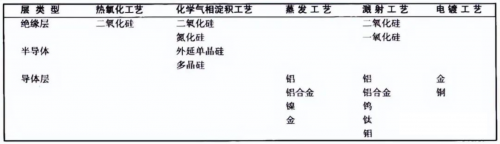

光刻工藝依靠光刻模板(reTIcle)和掩模版(mask)將特定圖形轉(zhuǎn)移至晶圓上。光刻模板可以直接用于進(jìn)行光刻也可以用來(lái)制造掩模版。掩模版就是在玻璃底板表面鍍鉻,進(jìn)行光刻步驟時(shí)光束會(huì)穿過未鍍鉻的亮場(chǎng)部分曝光在晶圓上的光刻膠上已達(dá)到圖形轉(zhuǎn)移的目的。

光刻模板和掩模板

光刻模板和掩模板一般由工廠的單獨(dú)部分制造或者從外部供應(yīng)商購(gòu)買。每個(gè)電路都有自己的光刻母版和掩模板。

以下為基本十步圖形化工藝:

光刻十步法工藝

摻雜

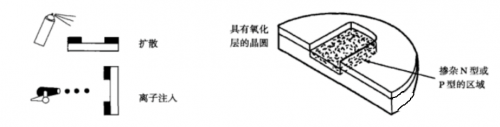

摻雜是將特定量的雜質(zhì)通過薄膜開口引入的晶圓表層的工藝過程。摻雜有兩種工藝方法:熱擴(kuò)散(thermal diffusion)和離子注入(ion implantaTIon)。熱擴(kuò)散是在1000℃下,摻雜原子通過擴(kuò)散化學(xué)反應(yīng)遷移帶暴露的晶圓表面,形成一層薄膜。離子注入是摻雜原子離子化后,被電場(chǎng)加速到很高的速度,從而注入至晶圓表層。

摻雜技術(shù)

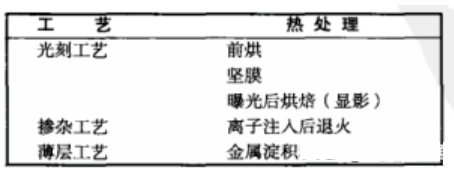

熱處理

熱處理是將晶圓加熱或冷卻來(lái)達(dá)到特性結(jié)果的工藝步驟。熱處理過程中晶圓沒有增加或減少任何物質(zhì)。離子注入后會(huì)有一步重要的熱處理過程,摻雜原子的注入會(huì)造成晶圓損傷,熱處理可以修復(fù)損傷,這稱為退火(anneal),溫度在1000℃左右。金屬導(dǎo)線制程后會(huì)有一步熱處理過程以確保金屬連線與晶圓表面緊密熔合從而確保良好的導(dǎo)電性。

熱處理表

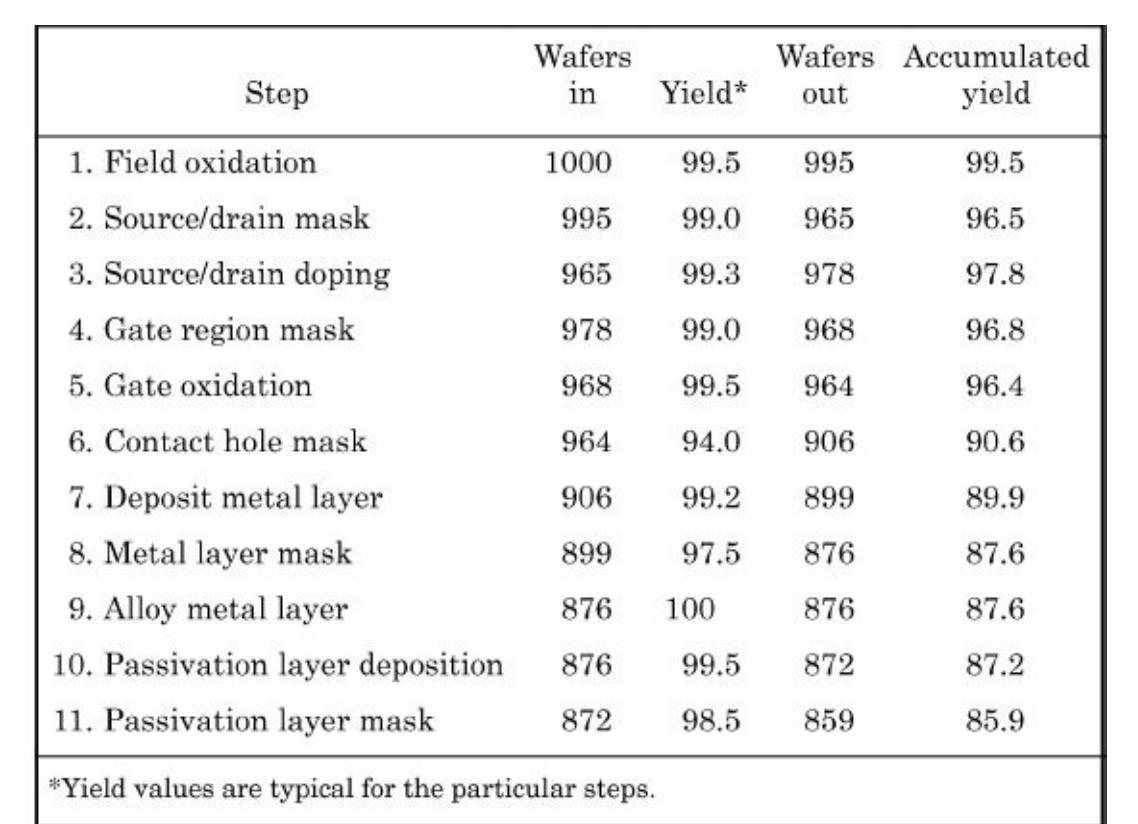

晶圓制造實(shí)例

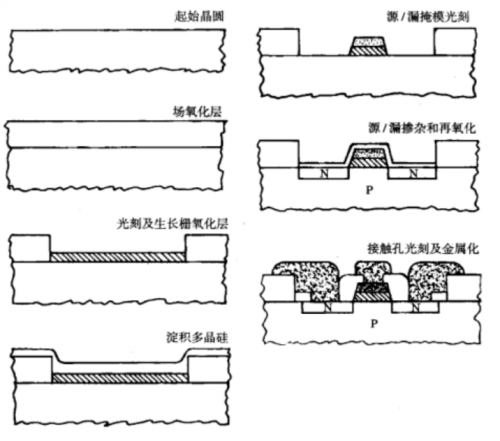

硅柵MOSFET工藝步驟

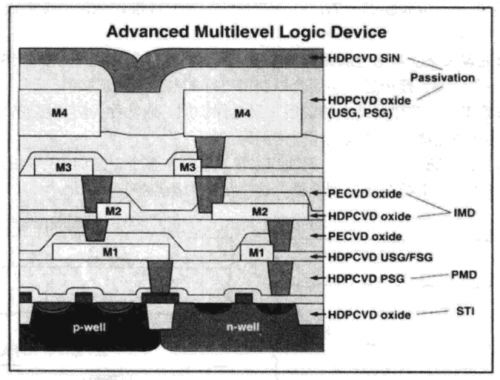

現(xiàn)代芯片結(jié)構(gòu)

還要說(shuō)明的是,半導(dǎo)體產(chǎn)業(yè)包括生產(chǎn)晶圓的晶圓產(chǎn)業(yè)以及以晶圓為材料設(shè)計(jì)和制造的晶圓加工產(chǎn)業(yè)——制造行業(yè) (Fabrication, FAB)。另外,還有組裝產(chǎn)業(yè),它將 加工過的晶圓切割成晶粒,并包裝好以防止受潮或受壓。

審核編輯 :李倩

-

集成電路

+關(guān)注

關(guān)注

5381文章

11388瀏覽量

360878 -

半導(dǎo)體

+關(guān)注

關(guān)注

334文章

27014瀏覽量

216333 -

晶圓制造

+關(guān)注

關(guān)注

7文章

272瀏覽量

24015

原文標(biāo)題:晶圓制造相關(guān)術(shù)語(yǔ)及工藝介紹

文章出處:【微信號(hào):射頻美學(xué),微信公眾號(hào):射頻美學(xué)】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

晶圓上的‘凸’然驚喜:甲酸回流工藝大揭秘

晶圓制造良率限制因素簡(jiǎn)述(1)

碳化硅晶圓和硅晶圓的區(qū)別是什么

WD4000系列晶圓幾何量測(cè)系統(tǒng):全面支持半導(dǎo)體制造工藝量測(cè),保障晶圓制造工藝質(zhì)量

WD4000系列晶圓幾何量測(cè)系統(tǒng):全面支持半導(dǎo)體制造工藝量測(cè),保障晶圓制造工藝質(zhì)量

半導(dǎo)體的晶圓與流片是什么意思?

半導(dǎo)體工藝晶圓片的制備過程

晶圓表面特性和質(zhì)量測(cè)量的幾個(gè)重要特性

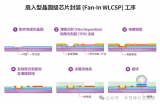

晶圓級(jí)封裝的五項(xiàng)基本工藝

晶圓鍵合設(shè)備及工藝

晶圓制造相關(guān)術(shù)語(yǔ)及工藝介紹

晶圓制造相關(guān)術(shù)語(yǔ)及工藝介紹

評(píng)論