我們正在經(jīng)歷對帶寬需求的爆炸性增長,這推動了 載波頻率為幾十兆赫茲。在這些極端 高頻,消費者可以享受更寬的帶寬而不必擔心 過度擁擠的頻譜。但是,隨著頻率的增加, 針對這些設備和頻率的儀器儀表解決方案可以成為 極其復雜。這源于對一個數(shù)量級更好的需求 儀器解決方案的性能,以防止在以下情況下?lián)p壞設備 測試。在本文中,我們將回顧幾種低相位噪聲信號的方法 代。我們將展示這些的優(yōu)點和缺點 方法并引入轉(zhuǎn)換循環(huán)設備,它充分利用了 所有頻率生成方法,無需復雜,可實現(xiàn)超低頻 相位噪聲信號生成。

鎖相環(huán)電路剖析

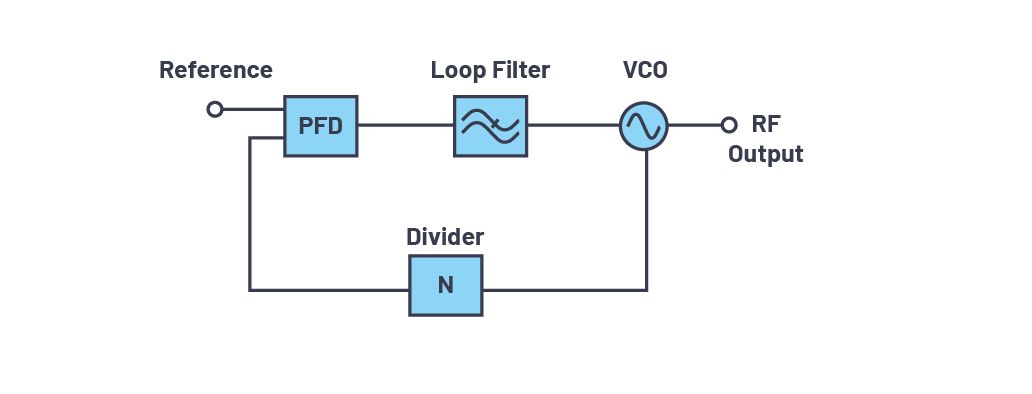

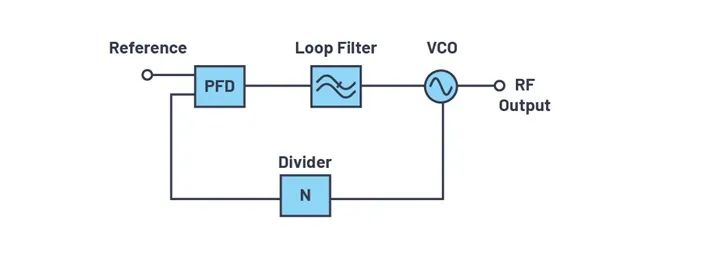

鎖相環(huán)(PLL)電路常見于許多頻率發(fā)生設備中。這些設備確保在 器件相位對齊或鎖定至參考信號。圖 1 顯示了一個 PLL的簡化框圖。壓控振蕩器的輸出 (VCO) 使用 N 計數(shù)器進行分頻,并與參考信號進行比較,使用 相位/頻率檢測器 (PFD) 電路。這個簡單的電路一直是 大量教科書并廣泛研究。我們將使用一些眾所周知的 確定如何大幅降低輸出端相位噪聲所需的基礎知識。

圖1.鎖相環(huán)電路。

每個構(gòu)建塊的缺陷或相位噪聲會影響整體 PLL電路的相位噪聲。與每個模塊相關的相位噪聲可以是 建模,并且可以精確預測PLL的整體相位噪聲 通過模擬和分析計算。讓我們回顧一下這些塊中的每一個 并討論它們?nèi)绾斡绊戄敵鱿辔辉肼暋?/p>

PFD模塊將參考信號與分頻輸出頻率進行比較。 該模塊產(chǎn)生一個誤差信號,該信號被饋送到電荷泵電路 產(chǎn)生控制電壓,控制VCO直到器件的輸出相位 匹配參考相位。大多數(shù)現(xiàn)代頻率發(fā)生設備 集成PFD電路在其數(shù)據(jù)手冊中提供了品質(zhì)因數(shù)(FOM)。用 FOM,帶內(nèi)相位噪聲可以計算如下:

哪里f聚苯乙烯是PFD頻率,N是輸出頻率的值 分。請注意,輸出頻率是f聚苯乙烯和 N 分頻器值。對于給定的輸出頻率,如f聚苯乙烯增加一個因素, N 值按相同的因子減小。這將導致整體較低 輸出相位噪聲,因為N值的任何減小都會降低相位 噪聲增加速度的兩倍,由于f聚苯乙烯術(shù)語。我們可以得出結(jié)論 PFD頻率越高,近載波相位噪聲越低 是。我們將在本文的以下部分中利用這一發(fā)現(xiàn)。

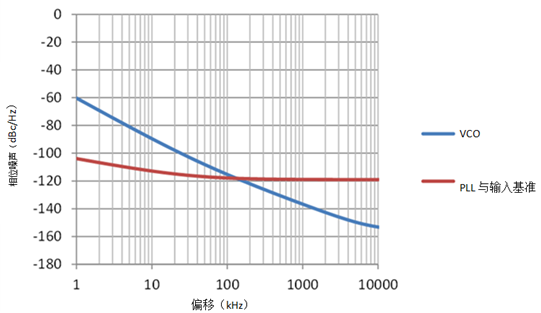

環(huán)路濾波器跟隨PFD,并平滑來自 控制VCO的PFD設備。它是通過使用 系統(tǒng),例如電荷泵電流、VCO 靈敏度和 PFD 頻率。 環(huán)路濾波器的一個不太強調(diào)的功能是它確定 負反饋控制環(huán)路的帶寬。參考信號將具有 控制帶寬內(nèi)輸出信號相位噪聲的影響 環(huán)路篩選器。超過此截止頻率,整體相位噪聲性能 將由VCO特性定義。我們將在下面利用這一事實 部分來優(yōu)化系統(tǒng)的整體相位噪聲。

VCO 根據(jù)施加的控制電壓創(chuàng)建輸出頻率 在其輸入。VCO輸出頻率由控制環(huán)路更新,直到 鎖相到參考信號的相位。VCO直接影響 系統(tǒng)的整體相位噪聲。一般來說,作為質(zhì)量因素 VCO增加,其相位噪聲變低。但是,更高的質(zhì)量因素 通常需要通常限制整體可調(diào)諧范圍的組件。視頻辦公室 針對窄頻率操作進行調(diào)諧的通常具有最佳相位 噪聲性能。

頻率生成選項

有許多方法可以使用各種振蕩器拓撲生成信號 不同的質(zhì)量水平。儀器儀表應用通常力求做到最好 在低相位噪聲和雜散電平方面的性能。讓我們回顧一下 一些頻率發(fā)生選項可以實現(xiàn)非常低的相位噪聲。

使用固定頻率振蕩器生成頻率

一類具有出色相位噪聲的信號發(fā)生器件 性能是固定頻率振蕩器。這些設備通常具有非常 高品質(zhì)因數(shù),可實現(xiàn)卓越的近載波相位噪聲性能。這些 振蕩器以預定頻率工作,主要由幾何形狀定義 以及具有一定可調(diào)性的器件結(jié)構(gòu),以實現(xiàn)相位鎖定 到參考源。恒溫箱控制晶體振蕩器 (OCXO),溫度 補償晶體振蕩器 (TCXO) 和壓控 SAW 振蕩器 (VCSO) 是這些類型設備的一些示例。一個主要缺點 固定頻率振蕩器是這些器件的有限頻率覆蓋范圍。 雖然它們可能適用于以一組固定頻率或 它們的倍數(shù),大多數(shù)儀表設備都需要變頻覆蓋。

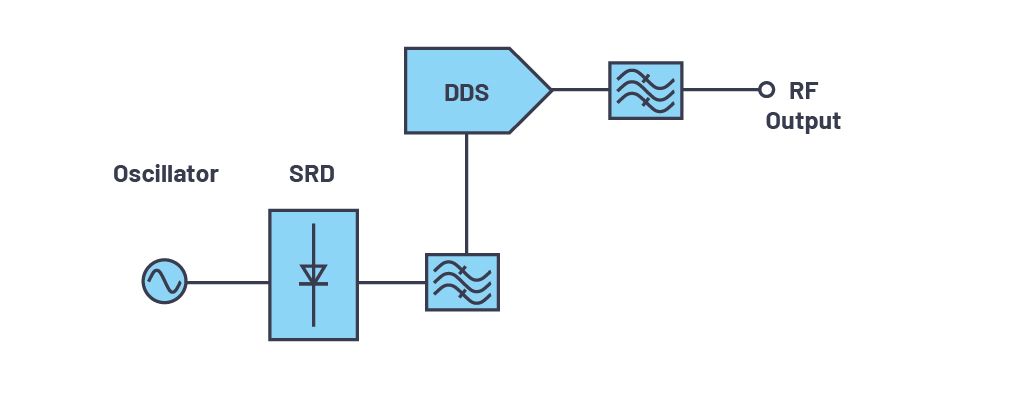

圖2.使用固定源進行變頻生成。

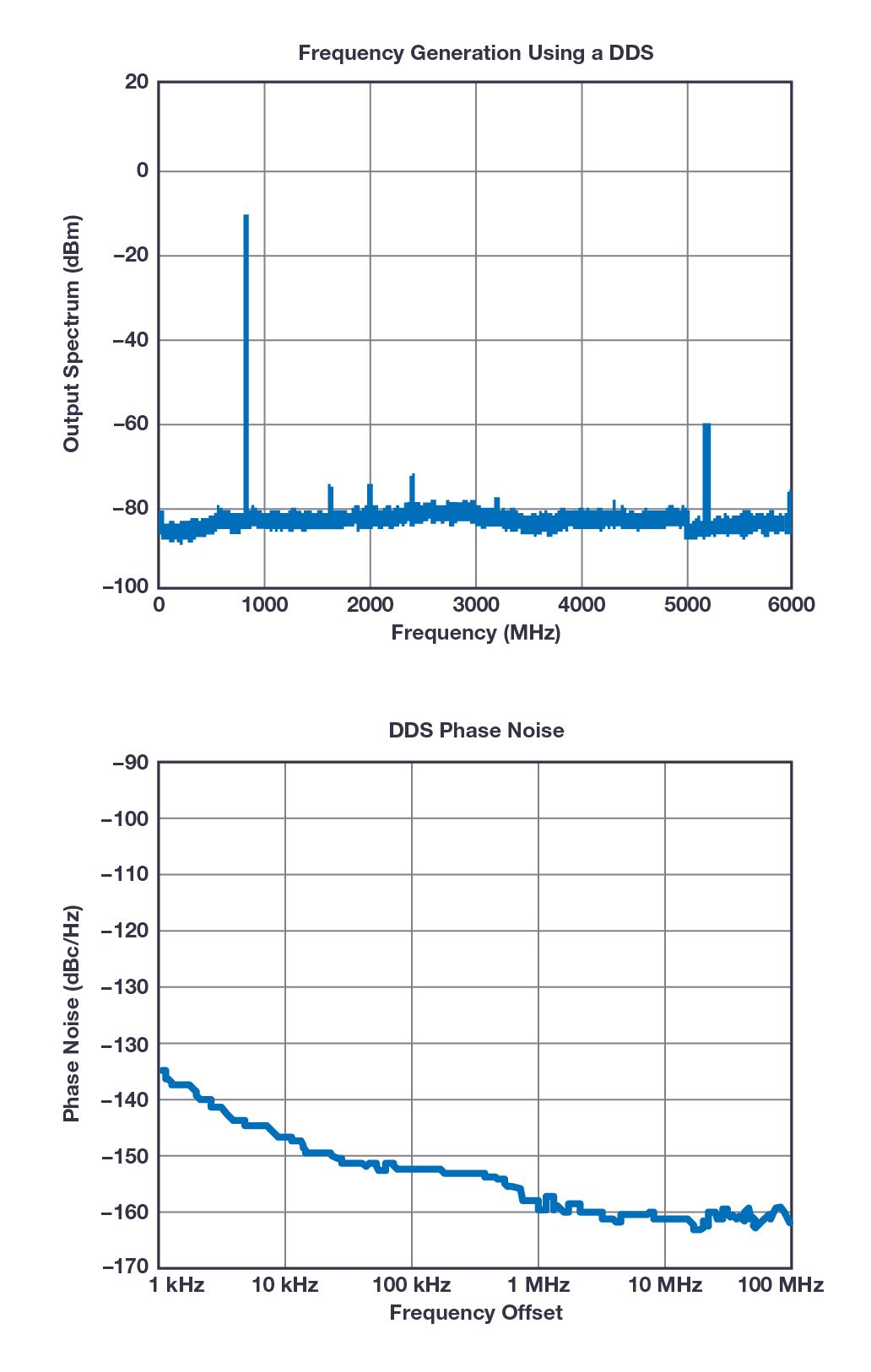

這個問題的一個解決方案是使用直接數(shù)字合成(DDS)或 數(shù)模轉(zhuǎn)換器 (DAC) 器件。可以使用固定頻率信號 以驅(qū)動DDS器件的采樣時鐘,如圖2所示。振蕩器的 頻率可以根據(jù)需要通過倍頻器或步進相乘 恢復二極管(SRD)并在應用于DDS之前進行濾波。DDS可以 創(chuàng)建任意頻率,最多為第一個采樣頻率的一半 奈奎斯特行動區(qū)。一些現(xiàn)代DAC器件甚至可以在第二奈奎斯特區(qū)舒適地工作。圖3顯示了一個示例輸出頻譜和 AD9164的相位噪聲圖,由低相位噪聲介電諧振驅(qū)動 6 GHz 的振蕩器 (DRO)。相位噪聲圖顯示輸出極低 相位噪聲,輸出頻譜的雜散電平小于–70 dBc。

倍增采樣時鐘的頻譜純度對輸出有直接影響 的設備。一旦信號乘以,許多諧波將出現(xiàn)在 輸出。需要對所需信號進行濾波,以實現(xiàn)極低的雜散 DDS 輸出端的水平。通常,采樣時存在的雜散 時鐘將以類似的級別出現(xiàn)在輸出中。對于較大的乘法因子, 過濾器可能需要非常鋒利,這可能需要很大的區(qū)域。

此外,乘法信號的相位噪聲隨著乘法的增加而增加 因子增加。例如,每當信號頻率加倍時, 相位噪聲增加6 dB。根據(jù)起始相位噪聲曲線和乘法因子,本底噪聲(遠端相位噪聲)可能會顯著增加, 使整體解決方案不那么吸引人。這是一個眾所周知的困境,其中 利用單頻、高質(zhì)量因數(shù)器件的近載波相位噪聲 帶有遠端相位本底噪聲損失。例如,表面聲學 波 (SAW) 器件具有出色的載波近載波相位噪聲性能 頻率約為 1 GHz。工作在 40 GHz 以上的毫米波設備將 要求乘法因子高達 40。這可能會導致 32 dB 或更高 相位本底噪聲增加,這可能會降低解決方案的吸引力。

圖3.AD9164在800 MHz時的輸出頻譜和相位噪聲,使用固定頻率振蕩器作為采樣時鐘。

使用寬帶PLL器件生成頻率

寬帶頻率合成器解決了與單個頻率合成器相關的許多挑戰(zhàn) 頻率設備。這些器件,如ADF4372微波頻率合成器, 使用多個VCO內(nèi)核,這些內(nèi)核進一步劃分為多個重疊頻帶。 這種架構(gòu)使每個內(nèi)核和頻段都能實現(xiàn)高質(zhì)量。這 與 利用單核的架構(gòu)。

與基于晶體或SAW的振蕩器相比,這些器件的一個關鍵優(yōu)勢是具有更高的基本工作頻率。許多現(xiàn)代VCO可以擁有 基頻范圍為 4 GHz 至 20 GHz 及更高。這使得 它們在毫米波應用中的遠端相位噪聲更具吸引力。 例如,在 10 GHz 基頻下工作的器件需要 系數(shù)為 4,將頻率擴展到 40 GHz。這轉(zhuǎn)化為相位噪聲 底板增加 12 dB,而晶體振蕩器增加 32 dB。

與這些多核和多頻段設備相關的一個挑戰(zhàn)是發(fā)現(xiàn) 合成目標頻率的最佳頻段。這可能涉及創(chuàng)建 查找表以識別正確的波段。配備自動校準的設備 ADF4372和ADF5610等特性使此過程更加容易, 對溫度和工藝變化具有魯棒性。這大大簡化了整體 可對頻率變化進行簡單編程的設備操作 進入設備的寄存器,最佳工作頻段是 自動確定。

此選項的另一個挑戰(zhàn)是與近端相位噪聲相關的 與單頻相比,這些器件通常要高得多 設備。即使整體相位本底噪聲較低,近距離相位也較高 噪聲可以轉(zhuǎn)化為更高的整體集成噪聲。這可能會限制使用 這些器件適用于需要較低集成相位噪聲的應用。

翻譯循環(huán)

轉(zhuǎn)換循環(huán)方法充分利用所有頻率生成 前面回顧的方法沒有采取其缺點。讓我們總結(jié)一下什么 到目前為止,在討論翻譯循環(huán)的細節(jié)之前,我們已經(jīng)發(fā)現(xiàn)了。

單頻器件,如OCXO、SAW和高質(zhì)量的晶體 因子具有最佳的近載波相位噪聲。這些單頻器件 通常基頻較低,使其相位噪聲遠 當它們乘以毫米波頻率時,吸引力較小。一個理想 解決方案可以采取這些設備的近距離性能,而不會太遠 相位噪聲損失。

DDS 或 DAC 器件可用于使用固定頻率產(chǎn)生可變頻率 頻率設備。這些設備還受到較大的乘法因子的影響 毫米波頻率需要,濾波需要抑制次諧波和其他不需要的雜散。容忍這些缺點可以使 理想的解決方案。

寬帶合成器可以具有非常高的基頻,具有出色的 遠端相位噪聲性能。但是,這些設備實際上并沒有很高 品質(zhì)因素,使得它們的近載波相位噪聲比較差 到單頻設備。利用其遠端相位噪聲,無需 降低近載波相位噪聲是必要的。

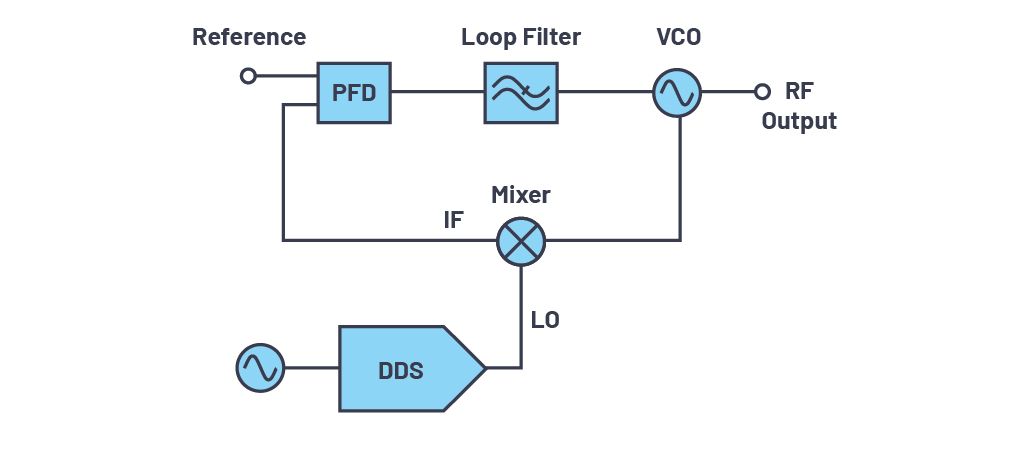

這就引出了轉(zhuǎn)換循環(huán)設備,如圖 4 所示。而不是 將輸出頻率除以大分頻器值,混頻器 用于將輸出信號轉(zhuǎn)換為匹配的中頻 (IF) 參考信號的頻率。這有效地將分頻器值降低到 1, 消除通常較大的分壓器值產(chǎn)生的噪聲貢獻 用于傳統(tǒng)PLL設備。這也影響了LO的相位噪聲曲線 在控制回路上。我們可以使用具有出色近距離的單頻設備 性能和DDS以創(chuàng)建此LO信號。

圖4.轉(zhuǎn)換循環(huán)體系結(jié)構(gòu)。

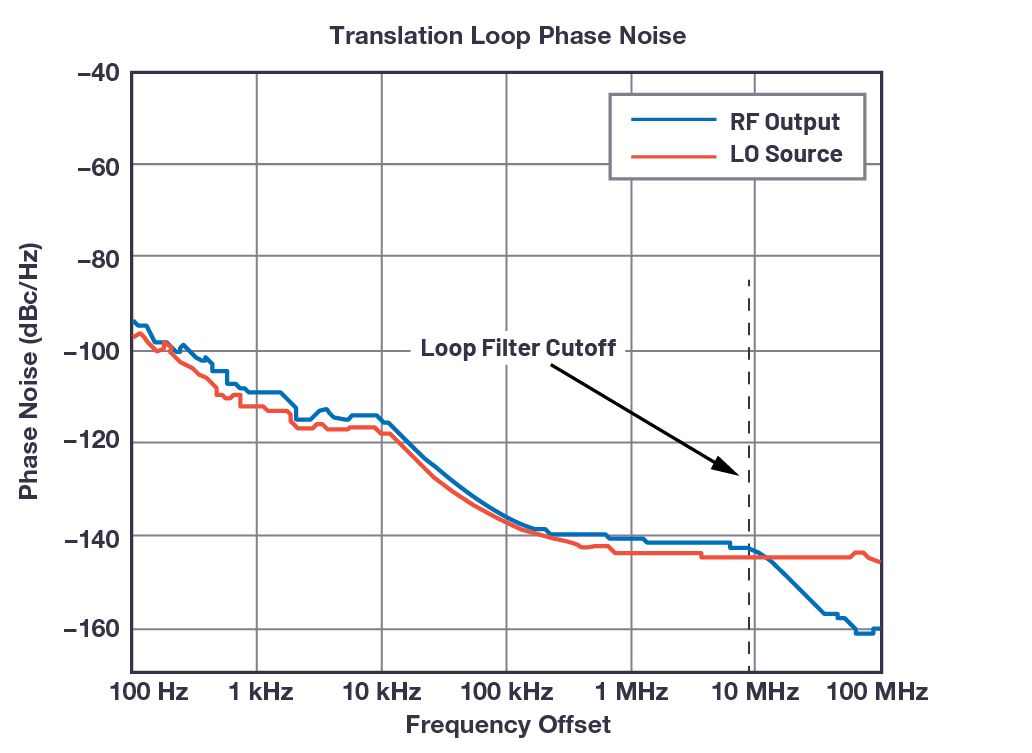

環(huán)路濾波器帶寬是轉(zhuǎn)換環(huán)路的關鍵設計參數(shù) 裝置。如前所述,環(huán)路濾波器決定了總帶寬 的控制回路。換句話說,它定義了參考和LO信號的距離 對輸出相位噪聲有影響。我們可以選擇一個大循環(huán) 轉(zhuǎn)換環(huán)路情況下的濾波器帶寬,因為近載波相位噪聲 極低。圖5顯示了轉(zhuǎn)換環(huán)路的相位噪聲曲線 器件及其LO輸入。請注意,雖然LO的特寫鏡頭極低 相位噪聲,遠端本底噪聲高。RF輸出跟蹤LO相位 噪聲高達環(huán)路濾波器帶寬。在此頻率偏移后,遠 相位噪聲由VCO定義,VCO極低。

轉(zhuǎn)換環(huán)路器件基本上利用了使用DDS器件作為LO的單頻器件所需的近距離性能,并利用 通過選擇大環(huán)路帶寬來獲得寬帶VCO的遠端相位噪聲。 這不僅打破了眾所周知的相位噪聲區(qū)域應為哪個的困境。 優(yōu)化,但也會產(chǎn)生極低的輸出相位噪聲。

圖5.轉(zhuǎn)換環(huán)路設備的相位噪聲曲線。

轉(zhuǎn)換環(huán)路的出色相位噪聲性能使其非常有用 在許多毫米波儀器儀表應用中。除了階段 噪聲性能,儀器儀表解決方案有望抑制雜散 信號到極低的水平。這對于轉(zhuǎn)換環(huán)路設備來說可能極具挑戰(zhàn)性,因為存在幾個具有不同 頻率。在許多情況下,防止LO的饋通是非常具有挑戰(zhàn)性的 和 IF 信號到輸出。此外,IF、LO、 并且可以在輸出端創(chuàng)建射頻信號。這些雜散信號可能導致 整體儀器儀表解決方案具有較差的雜散性能。

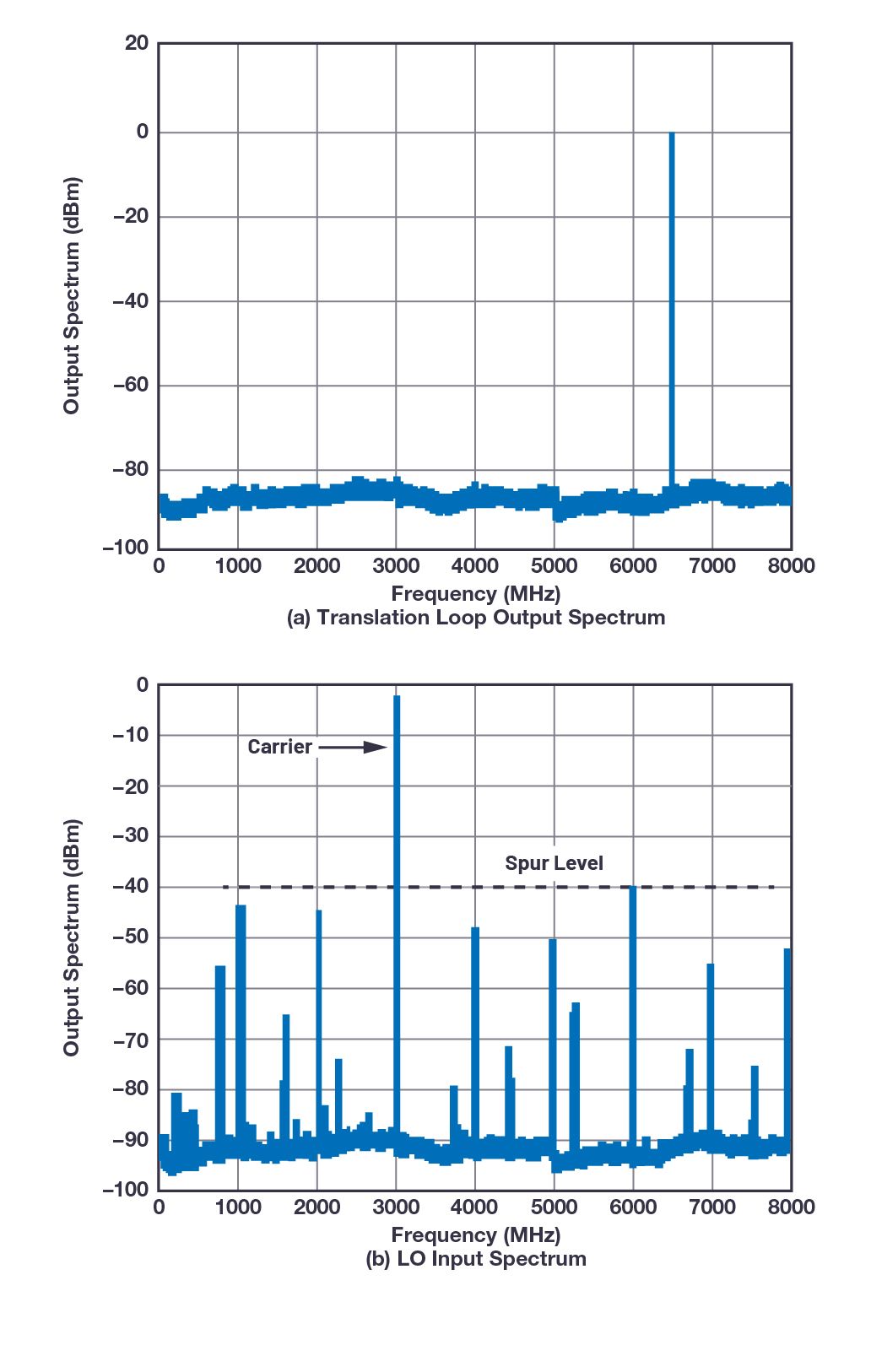

ADI公司提供完全集成的轉(zhuǎn)換環(huán)路器件ADF4401A、 它解決了其中的許多挑戰(zhàn)。它消除了所有饋通路徑 這可能存在于離散實現(xiàn)中。這是通過內(nèi)置的 屏蔽和整體設計實踐,最大限度地減少饋通機制。 此外,它還具有–90 dBc或無與倫比的雜散抑制性能 更低,可與釔鐵石榴石 (YIG) 球形振蕩器解決方案相媲美。這 即使系統(tǒng)的輸入 不太理想。圖6a顯示了帶LO 的ADF4401A的輸出頻譜 輸入包含許多雜散,雜散電平約為–40 dBc,如圖6b所示。 通常,這種類型的LO信號不能在儀器儀表解決方案中使用,因為 到所需的大量過濾。但是,ADF4401A可以接受 此LO輸入無需任何額外濾波即可產(chǎn)生輸出 頻譜如圖6a所示。

圖6.(a) 6.5 GHz 的轉(zhuǎn)換環(huán)路輸出頻譜和 (b) 3 GHz 的 LO 輸入頻譜。 使用ADF4401A的內(nèi)部LO倍頻器,有效LO頻率變?yōu)? GHz。在本例中,IF頻率為500 MHz。

該設備配備了自動校準引擎,可以識別 給定目標頻率的最佳VCO頻段。在校準模式下, 設備可以在實際溫度下搜索正確的頻段,并且 工藝條件,使調(diào)頻過程無縫銜接。

總結(jié)

儀器儀表解決方案需要非常低的相位噪聲載波信號 極低的雜散信號電平,滿足毫米波需求 設備。雖然有多種方法可以合成這些信號,但所有這些 具有重大權(quán)衡,使整體解決方案變得越來越復雜。這 ADI轉(zhuǎn)換環(huán)路器件ADF4401A具有多種不同的優(yōu)勢。 頻率生成選項沒有缺點。它可以實現(xiàn) 超低相位噪聲,具有無與倫比的雜散性能,無需 復雜的過濾。

審核編輯:郭婷

-

振蕩器

+關注

關注

28文章

3813瀏覽量

138904 -

pll

+關注

關注

6文章

775瀏覽量

135052 -

倍頻器

+關注

關注

8文章

76瀏覽量

35493

發(fā)布評論請先 登錄

相關推薦

如何選擇環(huán)路帶寬平衡抖動、相位噪聲、鎖定時間或雜散

全集成頻率綜合器——外國PLL博士論文

選擇環(huán)路帶寬涉及抖動、相位噪聲、鎖定時間或雜散問題

DAC相位噪聲性能改進包含殘余相位噪聲測量方法和最佳穩(wěn)壓器選擇

雙環(huán)路時鐘發(fā)生器可清除抖動并提供多個高頻輸出

具有輸入過壓保護的完全集成降壓轉(zhuǎn)換器參考設計

Maxim推出完全集成的PMIC

Maxim推出完全集成的高壓掃描驅(qū)動器

如何在鎖相環(huán)中實現(xiàn)相位噪聲和雜散性能

高度集成的射頻集成電路(RFIC)的相位噪聲性能

完全集成的即插即用轉(zhuǎn)換環(huán)

CN0147 利用低噪聲LDO調(diào)節(jié)器ADP150為ADF4350 PLL和VCO供電,以降低相位噪聲

為什么完全集成的轉(zhuǎn)換環(huán)路器件可實現(xiàn)最佳的相位噪聲性能

為什么完全集成的轉(zhuǎn)換環(huán)路器件可實現(xiàn)最佳的相位噪聲性能

評論