作者:Pablo Perez, Jr. and Patrick Errgy Pasaquian

從 5G 到工業(yè)應(yīng)用,收集、通信和存儲(chǔ)的數(shù)據(jù)量不斷增加,這擴(kuò)大了模擬信號(hào)處理設(shè)備的性能極限,有些達(dá)到每秒千兆采樣。隨著創(chuàng)新的步伐永遠(yuǎn)不會(huì)放緩,下一代電子解決方案將導(dǎo)致解決方案數(shù)量進(jìn)一步縮小,提高電源效率,并對(duì)更好的噪聲性能提出更大的需求。

人們可能會(huì)認(rèn)為,在各種電源域(模擬、數(shù)字、串行數(shù)字和數(shù)字輸入輸出(I/O))中產(chǎn)生的噪聲應(yīng)該簡(jiǎn)單地最小化或隔離,以實(shí)現(xiàn)最佳的動(dòng)態(tài)性能,但追求噪聲的絕對(duì)最小值可能是對(duì)收益遞減的研究。設(shè)計(jì)人員如何知道一個(gè)或多個(gè)電源的噪聲性能何時(shí)足夠?一個(gè)好的開(kāi)始是量化器件的靈敏度,以便電源頻譜輸出可以與域匹配。知識(shí)就是力量:它可以極大地幫助設(shè)計(jì),即避免過(guò)度設(shè)計(jì),從而節(jié)省設(shè)計(jì)時(shí)間。

本文概述了如何量化信號(hào)處理鏈中負(fù)載的電源噪聲靈敏度,以及如何計(jì)算最大可接受的電源噪聲。還討論了測(cè)量設(shè)置。最后,我們將介紹一些策略,以滿(mǎn)足電源域靈敏度和實(shí)際電源噪聲要求。本系列的后續(xù)文章將深入探討如何優(yōu)化ADC、DAC和RF收發(fā)器的配電網(wǎng)絡(luò)(PDN)。

了解和量化信號(hào)處理負(fù)載對(duì)電源噪聲的敏感性

電源優(yōu)化的第一步是研究模擬信號(hào)處理器件對(duì)電源噪聲的真實(shí)靈敏度。這包括了解電源噪聲對(duì)關(guān)鍵動(dòng)態(tài)性能規(guī)格的影響,以及電源噪聲靈敏度的表征,即電源調(diào)制比(PSMR)和電源抑制比(PSRR)。

PSMR和PSRR具有良好的電源抑制特性,但僅靠它們不足以確定紋波應(yīng)該有多低。本文演示如何使用PSMR和PSRR建立紋波容限閾值或最大允許電源噪聲。將此閾值與電源頻譜輸出相匹配是設(shè)計(jì)優(yōu)化電源系統(tǒng)設(shè)計(jì)的基礎(chǔ)。如果電源噪聲低于其最大規(guī)格,優(yōu)化的電源不會(huì)降低每個(gè)模擬信號(hào)處理器件的動(dòng)態(tài)性能。

電源噪聲對(duì)模擬信號(hào)處理器件的影響

應(yīng)了解電源噪聲對(duì)信號(hào)處理設(shè)備的影響。這些影響可以通過(guò)三個(gè)測(cè)量參數(shù)來(lái)量化:

無(wú)雜散動(dòng)態(tài)范圍 (SFDR)

信噪比 (SNR)

相位噪聲 (PN)

了解電源噪聲對(duì)這些參數(shù)的影響是優(yōu)化電源噪聲規(guī)格的第一步。

無(wú)雜散動(dòng)態(tài)范圍 (SFDR)

電源噪聲可以耦合到任何模擬信號(hào)處理系統(tǒng)的載波信號(hào)中。電源噪聲的影響取決于其相對(duì)于頻域中載波信號(hào)的強(qiáng)度。一種度量是SFDR,它表示可以與大干擾信號(hào)區(qū)分開(kāi)來(lái)的最小信號(hào),具體而言,載波信號(hào)的幅度與最高雜散信號(hào)的幅度之比,無(wú)論它落在頻譜中的哪個(gè)位置,因此:

SFDR = 無(wú)雜散動(dòng)態(tài)范圍 (dB)

載波信號(hào)=載波信號(hào)幅度(峰值或滿(mǎn)量程)的均方根值

雜散信號(hào) = 頻譜中最高雜散幅度的均方根值

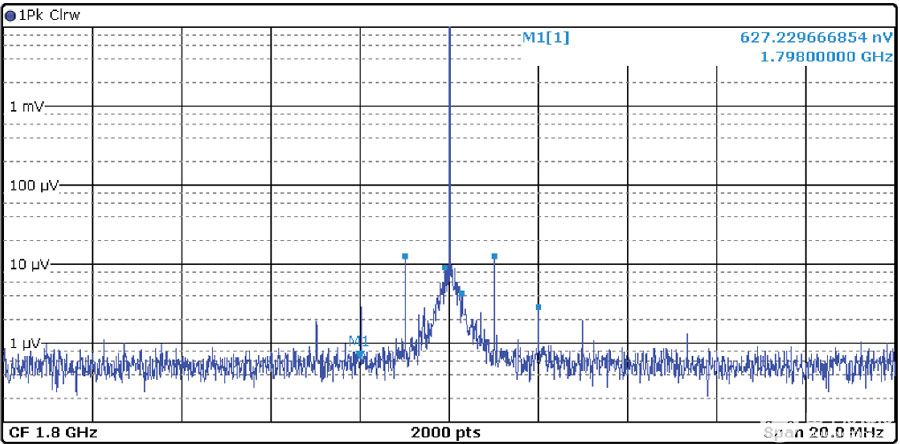

圖1.AD9208高速ADC的SFDR,使用(a)清潔電源和(b)噪聲電源。

SFDR可以相對(duì)于滿(mǎn)量程(dBFS)或載波信號(hào)(dBc)指定。電源紋波會(huì)耦合到載波信號(hào)中,從而產(chǎn)生不需要的雜散,從而降低SFDR。圖1比較了高速ADCAD9208采用干凈電源供電時(shí)與噪聲電源供電時(shí)的SFDR性能。在這種情況下,當(dāng)1 MHz電源紋波在ADC的快速傅里葉變換(FFT)頻譜輸出中以調(diào)制雜散的形式出現(xiàn)在載波頻率旁邊時(shí),電源噪聲會(huì)使SFDR降低約10 dB。

信噪比 (SNR)

SFDR取決于頻譜中的最高雜散,而SNR取決于頻譜內(nèi)的總噪聲。SNR限制了模擬信號(hào)處理系統(tǒng)查看低幅度信號(hào)的能力,理論上受到系統(tǒng)中轉(zhuǎn)換器分辨率的限制。SNR在數(shù)學(xué)上定義為載波信號(hào)電平與所有噪聲頻譜分量之和之比,但前五個(gè)諧波和直流除外,其中:

信噪比 = 信噪比 (dB)

載波信號(hào) = 載波信號(hào)的均方根值(峰值或滿(mǎn)量程)

頻譜噪聲 = 除前五個(gè)諧波外的所有噪聲頻譜分量的均方根和

噪聲電源可以通過(guò)耦合載波信號(hào)并在輸出頻譜中添加噪聲頻譜分量來(lái)降低SNR。如圖2所示,當(dāng)1 MHz電源紋波在FFT輸出頻譜中產(chǎn)生頻譜噪聲分量時(shí),AD9208高速ADC的SNR從56.8 dBFS降至51.7 dBFS。

相位噪聲 (PN)

相位噪聲是衡量信號(hào)頻率穩(wěn)定性的指標(biāo)。理想情況下,振蕩器應(yīng)該能夠在特定的時(shí)間段內(nèi)產(chǎn)生一組特定的穩(wěn)定頻率。然而,在現(xiàn)實(shí)世界中,信號(hào)上總是存在小的、不需要的幅度和相位波動(dòng)。這些相位波動(dòng)或抖動(dòng)可以在頻譜中信號(hào)的兩側(cè)擴(kuò)散。

相位噪聲可以通過(guò)多種方式定義。在本文中,相位噪聲被定義為單邊帶(SSB)相位噪聲,這是一個(gè)常用的定義,它使用載波信號(hào)偏移頻率的功率密度與載波信號(hào)總功率的比值,其中:

SSB PN = 單邊帶相位噪聲 (dBc/Hz)

邊帶功率密度 = 載波信號(hào)偏移頻率下每 1 Hz 帶寬的噪聲功率 (W/Hz)

載波功率 = 總載波功率 (W)

圖2.AD9208高速ADC的SNR,使用(a)干凈電源和(b)噪聲電源。

圖3.(a) 兩種不同的電源,輸出噪聲成分存在顯著差異。(b) ADRV9009分別由這兩個(gè)電源供電時(shí)的相位噪聲性能。

在模擬信號(hào)處理器件中,通過(guò)時(shí)鐘電源電壓耦合到器件時(shí)鐘的電壓噪聲會(huì)產(chǎn)生相位噪聲,進(jìn)而影響內(nèi)部本振(LO)的頻率穩(wěn)定性。這擴(kuò)大了頻譜中LO頻率的范圍,增加了載波相應(yīng)偏移頻率處的功率密度,從而增加了相位噪聲。

圖3顯示了ADRV9009收發(fā)器由兩個(gè)不同電源供電時(shí)的相位噪聲性能比較。圖3a顯示了兩個(gè)電源的噪聲頻譜,圖3b顯示了產(chǎn)生的相位噪聲。兩個(gè)電源均基于 LTM8063 μModule 穩(wěn)壓器,擴(kuò)頻頻率調(diào)制 (SSFM) 接通。SSFM的優(yōu)點(diǎn)是,通過(guò)將基波分布到一定頻率范圍內(nèi),它可以改善轉(zhuǎn)換器基波開(kāi)關(guān)頻率及其諧波的噪聲性能。這可以從圖3a中看出——注意1 MHz處相對(duì)較寬的噪聲峰值及其諧波。代價(jià)是SSFM的三角波調(diào)制頻率產(chǎn)生低于100 kHz的噪聲,請(qǐng)注意峰值從2 kHz左右開(kāi)始。?

備用電源增加了一個(gè)低通濾波器,以抑制1 MHz以上的噪聲,并增加了一個(gè)低壓差(LDO)后置穩(wěn)壓器ADP1764,以降低整體本底噪聲,特別是低于10 kHz(主要是SSFM引起的噪聲)。由于附加濾波,電源噪聲的整體改善導(dǎo)致相位噪聲性能增強(qiáng),低于10 kHz失調(diào)頻率,如圖3b所示。

模擬信號(hào)處理器件的電源噪聲靈敏度

負(fù)載對(duì)電源紋波的靈敏度可以通過(guò)兩個(gè)參數(shù)來(lái)量化:

電源抑制比 (PSRR)

電源調(diào)制比

電源抑制比 (PSRR)

PSRR表示器件在一定頻率范圍內(nèi)衰減電源引腳噪聲的能力。通常,有兩種類(lèi)型的PSRR:靜態(tài)(直流)PSRR和動(dòng)態(tài)(交流)PSRR。直流PSRR用作衡量由直流電源電壓變化引起的輸出失調(diào)變化的指標(biāo)。這是一個(gè)最小的問(wèn)題,因?yàn)殡娫聪到y(tǒng)應(yīng)為負(fù)載提供經(jīng)過(guò)良好調(diào)節(jié)的直流電壓。另一方面,AC PSRR表示設(shè)備在一定頻率范圍內(nèi)抑制直流電源中的交流信號(hào)的能力。

AC PSRR 是通過(guò)在器件的電源引腳上注入正弦波信號(hào)并觀察注入頻率下數(shù)據(jù)轉(zhuǎn)換器/收發(fā)器輸出頻譜本底噪聲上出現(xiàn)的誤差雜散來(lái)確定的(圖 4)。AC PSRR定義為注入信號(hào)的測(cè)量幅度與輸出頻譜上誤差雜散的相應(yīng)幅度之比,其中:

誤差雜散 = 由于注入紋波而在輸出頻譜中看到的雜散幅度

注入紋波 = 在輸入電源引腳耦合和測(cè)量的正弦波幅度

圖4.由于電源紋波,模擬信號(hào)處理設(shè)備的輸出頻譜會(huì)出現(xiàn)誤差。

圖5顯示了典型PSRR設(shè)置的框圖。以10 GSPS高速ADC9213為例,1 MHz、13.3 mV p-p正弦波在1.0 V模擬電源軌處有效耦合。相應(yīng)的1 MHz數(shù)字化雜散出現(xiàn)在ADC的–108 dBFS FFT頻譜本底噪聲上方。1 MHz數(shù)字化雜散為–81 dBFS,對(duì)應(yīng)于124.8 μV的峰峰值電壓,參考模擬輸入滿(mǎn)量程范圍1.4 V p-p。使用公式4計(jì)算1 MHz時(shí)的交流PSRR,得出1 MHz時(shí)的交流PSRR為40.5 dB。 圖6顯示了AD9213在1.0 V AVDD供電軌下的交流PSRR。

圖5.PSRR/PSMR 測(cè)試設(shè)置的簡(jiǎn)化框圖。

Figure 6. AD9213 high speed ADC ac PSRR for a 1.0 V AVDD rail.

Power Supply Modulation Ratio (PSMR)

PSMR對(duì)模擬信號(hào)處理設(shè)備的影響與PSRR不同。PSMR顯示器件在與RF載波信號(hào)調(diào)制時(shí)對(duì)電源噪聲的靈敏度。該效應(yīng)可以看作是施加到器件的載波頻率周?chē)恼{(diào)制雜散,并顯示為載波邊帶。

電源調(diào)制是通過(guò)使用線路饋電器/耦合電路將輸入紋波信號(hào)與干凈的直流電壓相結(jié)合來(lái)實(shí)現(xiàn)的。電源紋波作為正弦波信號(hào)從信號(hào)發(fā)生器注入電源引腳。調(diào)制到RF載波的正弦波產(chǎn)生邊帶雜散,其偏移頻率等于正弦波頻率。雜散的電平受正弦波幅度和器件靈敏度的影響。簡(jiǎn)化的PSMR測(cè)試設(shè)置與PSRR相同,如圖5所示,但輸出顯示集中在載波頻率及其邊帶雜散上,如圖7所示。PSMR定義為電源注入紋波幅度與載波周?chē){(diào)制邊帶雜散幅度的比值,其中:

調(diào)制雜散 = 由于注入紋波而在載波頻率邊帶處的雜散幅度

注入紋波 = 在輸入電源引腳耦合和測(cè)量的正弦波幅度

圖7.由于電源紋波,載波信號(hào)中的調(diào)制邊帶雜散。

考慮AD9175 12.6 GSPS高速DAC,采用100 MHz載波工作,10 MHz電源紋波約為3.05 mV p-p,在1.0 V AVDD供電軌上主動(dòng)耦合。載波信號(hào)的邊帶中出現(xiàn)相應(yīng)的24.6 μV p-p調(diào)制雜散,失調(diào)等于約10 MHz的電源紋波頻率。 使用公式5計(jì)算10 MHz時(shí)的PSMR得到41.9 dB。圖8所示為AD9175 1.0V AVDD電源軌PSMR,用于通道DAC0在不同載波頻率下。

圖8.AD9175高速DAC PSMR,用于1.0 V AVDD供電軌(通道DAC0)。

確定最大允許電源紋波

PSMR可以與用電器件的基準(zhǔn)閾值結(jié)合使用,以確定模擬信號(hào)處理器件每個(gè)電源域上的最大允許電壓紋波。基準(zhǔn)閾值本身可以是代表器件可以承受的允許雜散水平(由電源紋波引起)的幾個(gè)值之一,而不會(huì)顯著影響其動(dòng)態(tài)性能。該雜散電平可以是無(wú)雜散動(dòng)態(tài)范圍(SFDR)、最小有效位(LSB)的百分比或輸出頻譜本底噪聲。公式6顯示了最大允許輸入紋波(VR_MAX) 作為 PSMR 和每個(gè)設(shè)備的測(cè)量本底噪聲的函數(shù),其中:

VR_MAX= 在輸出頻譜本底噪聲中產(chǎn)生雜散之前每個(gè)電源軌上的最大允許電壓紋波

PSMR = 目標(biāo)電源軌的噪聲靈敏度(單位:dB)

閾值 = 預(yù)定義的參考閾值(在本文中,輸出頻譜本底噪聲)

例如,AD9175的輸出頻譜本底噪聲約為1 μV p-p。1800 MHz載波在10 MHz紋波時(shí)的PSMR約為20.9 dB。使用公式6,器件電源引腳在不降低動(dòng)態(tài)性能的情況下可以承受的最大允許紋波為11.1 μV p-p。

圖9顯示了LT8650S降壓靜音開(kāi)關(guān)穩(wěn)壓器穩(wěn)壓器(帶或不帶輸出LC濾波器)的頻譜輸出與AD9175在1.0 V AVDD供電軌上的最大允許紋波的綜合結(jié)果。穩(wěn)壓器頻譜輸出包含基波開(kāi)關(guān)頻率及其諧波的雜散。LT8650S直接為AD9175供電會(huì)產(chǎn)生超過(guò)最大允許閾值的基波,導(dǎo)致輸出頻譜中產(chǎn)生調(diào)制邊帶雜散,如圖10所示。只需添加一個(gè)LC濾波器,開(kāi)關(guān)雜散就會(huì)降低到最大允許紋波以下,如圖11所示。?

圖9.LT8650S電源頻譜輸出與1.0 V AVDD軌下最大允許電壓紋波的關(guān)系。

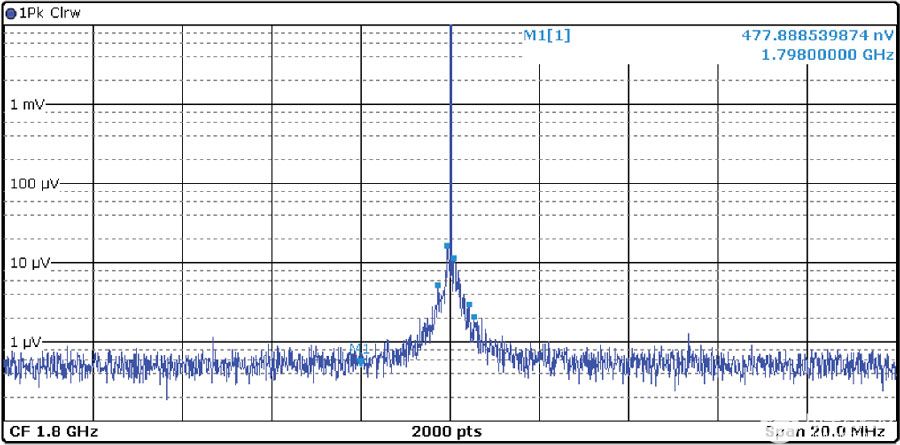

圖 10.AD9175 DAC0輸出頻譜,載波頻率為1800 MHz,采用LT8650S直流-直流靜音開(kāi)關(guān)轉(zhuǎn)換器直接輸出至AVDD電源軌。

圖 11.AD9175 DAC0輸出頻譜,載波頻率為1800 MHz,采用LT8650S和LC濾波器電源。

結(jié)論

高速模擬信號(hào)處理器件的卓越動(dòng)態(tài)性能很容易被電源噪聲所削弱。必須徹底了解信號(hào)鏈對(duì)電源噪聲的敏感性,以避免系統(tǒng)性能下降。這可以通過(guò)建立最大允許紋波來(lái)確定,這對(duì)于設(shè)計(jì)配電網(wǎng)絡(luò)(PDN)至關(guān)重要。當(dāng)已知最大允許紋波閾值時(shí),可以采用各種方法來(lái)設(shè)計(jì)優(yōu)化的電源。與最大允許紋波相差良好表明 PDN 不會(huì)降低高速模擬信號(hào)處理設(shè)備的動(dòng)態(tài)性能。

審核編輯:郭婷

-

電源

+關(guān)注

關(guān)注

184文章

17584瀏覽量

249485 -

adc

+關(guān)注

關(guān)注

98文章

6432瀏覽量

544087 -

RF收發(fā)器

+關(guān)注

關(guān)注

1文章

72瀏覽量

24484

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

電源噪聲對(duì)模擬信號(hào)處理器件的影響

了解麥克風(fēng)靈敏度

揚(yáng)聲器的靈敏度

Multisim中的靈敏度分析方法,為什么沒(méi)有電容的靈敏度,另外靈敏度是怎么判斷的。

優(yōu)化信號(hào)鏈的電源系統(tǒng) — 多少電源噪聲可以接受?

如何計(jì)算信號(hào)處理鏈中負(fù)載最大可接受電源噪聲?

# **LOTO虛擬示波器關(guān)于觸發(fā)靈敏度功能**

什么是接收靈敏度

如何用LNA改善GPS的靈敏度

如何定義接收靈敏度的公式

介紹接收機(jī)靈敏度的定義及性能

無(wú)線模塊性能測(cè)試—靈敏度

電源設(shè)計(jì)的靈敏度分析

如何量化信號(hào)處理鏈中負(fù)載的電源噪聲靈敏度

如何量化信號(hào)處理鏈中負(fù)載的電源噪聲靈敏度

評(píng)論