隨著領先的芯片制造商繼續將 finFET——以及很快的納米片晶體管——縮小到越來越小的間距,最小的金屬線最終將無法使用銅及其liner和barrier金屬。接下來會發生什么?什么時候發生?這還有待確定。因為目前看來,有多種選擇正在探索中,每一種都有自己的一套權衡。

自從 IBM 在 1990 年代向業界介紹采用雙鑲嵌(dual damascene)處理的銅互連以來,半導體行業一直在利用銅的高導電率、低電阻率和可靠互連的優勢。但隨著電阻和電容的增加,RC 延遲將繼續顯著影響器件性能。

盡管可以使用雙鑲嵌來集成如釕和鉬這樣的銅替代品,但它們可能更適合金屬蝕刻的減法方案(subtractive schemes),自鋁互連時代以來,這種方案尚未在邏輯中廣泛使用。盡管如此,領先的設備制造商和設備公司正在尋找一些有趣的途徑來獲取這些最低含量的銅。與此同時,工程師和研究團隊正在進一步擴展銅線,這提供了迄今為止更實惠、更有吸引力的路線。

“在過去的 25 年里,雙鑲嵌一直是并且仍然是互連的基礎。但我們看到,由于 RC 延遲的原因,金屬圖案(metal patterning)可能變得相關,”imec 研究員兼納米互連項目總監 Zsolt Tokei 說。Imec 的方案稱為 semi-damascene,由于向減法工藝的過渡將是顛覆性的,因此可能會被逐步引入。“我們認為一開始它會被用于一層,但后來它會傳播到幾層。這與自對準過孔相(self-aligned vias)結合,可能還會改變到線的中間。”

同時,如果可能的話,系統性能驅動因素使得將存儲設備轉移到生產線后端變得有吸引力。如果并且當行業開始引入具有較低熱預算的互連工藝時,內存或其他設備集成等事情就變得可行了。但首先,必須解決擴展銅線和引入背面配電方案的直接工程挑戰。

銅還能走多遠

在 2nm 邏輯節點,銅線和通孔正在通過創造性的方式延伸。一些最有吸引力的選擇包括限制barrier和liner對電阻率的影響,方法是使這些薄膜更薄( films thinner)——從化學氣相沉積 (CVD) 到原子層沉積 (ALD)——或者消除它們,例如,沿垂直方向過孔和線路之間的路徑。

TEL 和 Applied Materials 都提供使用自組裝單分子層 (SAM:self-assembled monolayers) 實現選擇性沉積的集成工藝。這些使用 CVD 或旋涂薄膜的 SAM 通常有選擇地沉積在金屬上,而不是電介質上,因此鈷或釕liners或 ALD Ta/TaN 等barriers會粘附到所需表面。

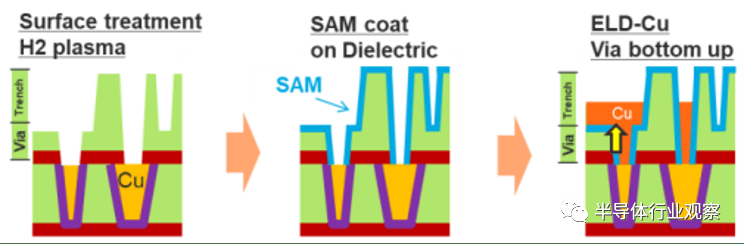

在 IITC 的一次演講中,Yuki Kikuchi 及其 TEL 企業研發部和 JSR Micro 的同事展示了與使用 JSR 的 SAM 抑制 ALD TaN 相關的電阻和銅體積的改善,甚至取代了銅阻擋層金屬。對低 k 電介質 (2.5) 的最佳選擇性是通過在通孔底部使用一種 SAM (SAM_B),然后在低 k 上使用另一種材料 (SAM_F) 實現的(見圖 1)。該流程能夠完全消除通路側壁(sidewalls)上的釕liner。

圖 1:氫氣預處理(hydrogen pretreatment)后,自組裝單層 (SAM) 在使用化學沉積的預通孔填充過程中充當屏障(barrier)。資料來源:IITC 2022

有趣的是,研究人員測試了一種預通孔填充( pre-via-fill)工藝,在這種工藝中,銅填充下方沒有使用阻擋層 (TaN),而是在化學沉積 (ELD) 之后沉積。設備制造商正在進行更廣泛的預填充通孔測試,以降低電阻率、確保可靠性并提高銅流的生產率。

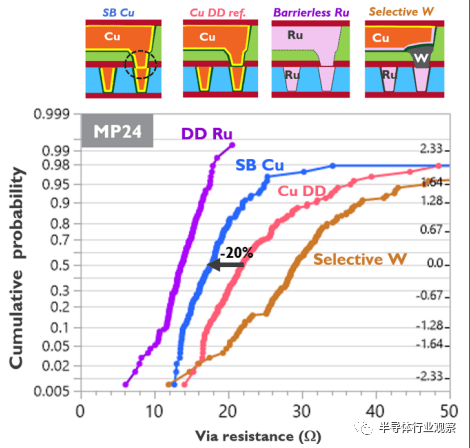

微小的過孔是互連鏈中最薄弱的環節。Imec 和 Applied Materials 比較了釕、鎢和銅通孔,以了解與在 24nm 通孔中使用鎢或釕的對比狀況,通過消除銅中的底部 Ta 阻擋層可以獲得哪些電阻優勢(見圖 2)。“關鍵工藝步驟是在對通孔底部的裸露銅進行原位界面( in-situ interface )工程之后,在電介質上選擇性 ALD TaN 阻擋層沉積。”imec 互連金屬化專家 Marleen van der Veen 說. 該團隊確定通過消除障礙實現了 20% 的通孔電阻降低。在較小的尺寸下,減少會更大。

圖 2:比較雙鑲嵌銅參考與選擇性阻擋銅、無阻擋雙鑲嵌釕和混合鎢/銅的單通孔電阻顯示,消除通孔底部的阻擋層有 20% 的好處。資料來源:IITC 2022

拐點:引入減法蝕刻(subtractive etch)

在 2nm 節點之后的某個時候,該行業可能會從雙鑲嵌轉變為一種減法金屬化(subtractive metallization )形式。這代表著巨大的變化,而且不會掉以輕心。

Imec 的減法金屬化版本稱為半鑲嵌,因為它從溝槽的介電蝕刻開始,類似于雙鑲嵌。“這是非常大的一步,因為它是一個新模塊并且存在風險,”imec 的 Tokei 說。“然后,縱橫比可以逐漸增加,在某些時候可以加入氣隙(air gaps)。” 該工藝使用電介質 CMP 步驟,類似于在淺溝槽隔離 (STI) 步驟執行的電介質 CMP。

Tokei 預計最有可能進行四代釕半鑲嵌工藝。之后,二元或三元金屬合金可能會發揮作用。“根據電阻率和其他一些因素,我們已經確定了幾個很好的候選者,但這是非常早期的研發工作,”他說。“我們有大約六年的時間來真正縮小到最佳候選的范圍。”

在半鑲嵌中,通孔首先在電介質堆疊中形成圖案,然后進行釕沉積,這會溢出特征。然后對該金屬層進行掩蔽和蝕刻以形成與通孔正交的線路層。金屬圖案化后,線路可以填充電介質或用于在局部層形成部分氣隙。根據 imec 模擬,該工藝的成本與雙鑲嵌相當。

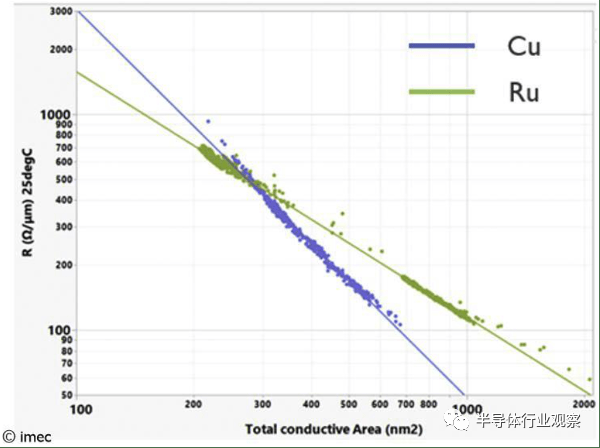

那么銅互連的規模有多遠?在與釕的直接比較中,最近的一項研究發現,就電阻率而言,從銅到釕的交叉點剛好低于 300nm2,約為 17 x 17nm(見圖 3)。

有多種制造氣隙(air gaps)的方法,包括部分間隙填充(gap fill )或使用sacrificial材料。然而,Tokei 指出,在類似尺寸的晶圓上實現一致的氣隙深度是一個行業挑戰。他強調,氣隙的形成不需要額外的掩膜層,而是作為加工的一部分形成。此外,必須特別注意散熱,因為空氣是劣質導體。

圖 3:釕的電阻率在 300nm2 以下低于銅。資料來源:VLSI 2022

過渡到subtractive metallization具有根本優勢,包括不會因 CMP 和蝕刻而造成介電損壞,能夠采用更高縱橫比的線(降低電阻),以及可能更簡單的工藝。盡管如此,蝕刻工藝的負擔要大得多,尤其是當 CD 向 10nm 金屬間距發展時。

Lam Research 和 imec 探討了與氧基釕蝕刻化學品相關的一些挑戰。通常,釕通過濺射(物理氣相沉積或 PVD)沉積,然后在 400°C 左右退火以實現最低電阻率。Si3N4/TiN 硬掩模(mandrels)中的間隔圖案用于形成緊密尺寸,從中蝕刻 >3 縱橫比的釕線。一個關鍵挑戰涉及在硬掩模的側壁上生長氧化層,這會顯著縮小溝槽。實施高級清潔步驟和原位等離子清潔(in-situ plasma cleans)以去除殘留物并限制 TiN 底切(undercut)。

對于 Cl 2 /O 2化學中的鉬蝕刻,Lam 和 imec 確定主要問題是側壁鈍化不足(insufficient sidewall passivation)和金屬氧化。該團隊能夠通過在部分鉬蝕刻后沉積薄氧化物來解決這個問題,他們指出,由于金屬的氧化電位,封裝可能是必要的。

“根據數據,我們在釕方面取得的進展比在鉬方面取得的進展更多,”imec 的 Tokei 說。“鉬的一個問題是氧化,這使得它更適合鑲嵌類型的方法。這對于中線來說非常有趣,而且它是一種廉價的金屬。”

工藝建模在幫助建立設計規則、評估工藝窗口和提高產量方面發揮著關鍵作用。Lam計算產品副總裁大衛·弗里德 (David Fried) 表示:“虛擬制造是對工藝和工藝流程的逐步行為描述,它與關鍵設計信息相結合,以創建晶圓中發生的事情的硅精確 3D 模型。”

例如,Lam 的 Coventor 部門的 SEMulator3D 平臺被用來評估 imec 的帶有工藝助推器的半鑲嵌流如何影響金屬間距為 14nm 和 16nm(1.5nm 節點)的新掩模組的 RC 性能。性能助推器,包括完全自對準圖案、高 AR 金屬線和氣隙,都經過建模和確認。在其他發現中,模擬器比較了不同的通孔自對準方法,以確定哪種方法在 10 納米和 7 納米節點上實現了最寬的覆蓋公差。

“因為這些模型必須精確到硅,我們在校準技術上花費了大量時間,”Fried 說。“通過我們的基線流程模型,我們使用機器學習技術對流程模型進行多元非線性優化,從而創建該流程的可視化表示。當它被校準到過程空間中的多個點時,它就可以預測過程窗口的其余部分。”

連接背面電源

背面電源傳輸 (BPD) 是一種從晶圓背面向晶體管傳輸電源的創新方式,釋放了正面互連以僅傳輸信號。這緩解了擁堵,領先的芯片制造商將在 2nm 節點上實施它。Lam Research 的高級工程總監 Tom Mountsier 說:“利用晶圓背面進行配電可以有效地增加芯片的功能面積,而不會增加其占地面積。”

“背面電源集成的最大挑戰之一是電連接晶圓的正面和背面。這就是 TSV 的用武之地,”Mountsier 說,并指出芯片制造商正在評估不同的集成方案。所有選項都涉及蝕刻和金屬填充。

最具挑戰性的方案涉及到源極外延的直接背面接觸。“通孔將很小,縱橫比很高,”他說。“您還需要與外延層進行低電阻接觸,就像在正面對源極/漏極接觸所做的那樣。因此,填充鎢或鉬可能是可能的選擇。由于重大的集成挑戰,例如將背面接觸與正面外延對齊,以及在降低的溫度(400°C 或更低)下在金屬和外延之間進行歐姆接觸,實施將需要時間。”

Lam 的高級半導體工藝工程師 Assawer Soussou 總結道:“背面電源傳輸以工藝復雜性為代價實現了技術優勢。”

電力輸送也已成為企業封裝方面的熱門話題。“最近,人們對光子學很感興趣,尤其是聯合封裝光學器件,”ASE 銷售和營銷高級副總裁 Yin Chang 說。“這大大增加了數據傳輸的帶寬。許多公司都在通過基板承載多少帶寬方面遇到了限制,如果您無法滿足這些要求,那么光子學確實是唯一的選擇。所以基板真的變成了一個電力傳輸系統。”

結論

目前,雙鑲嵌銅的間距已擴展到 20 納米,但即將徹底改變涉及釕或其他替代金屬的減法方案。就電阻率而言,隨著功能下降到 17 x 17nm 以下,領先的設備制造商正在接近,釕變得很有吸引力。公司可以在為重大轉型做準備的同時,使用barrierless via bottoms 獲得額外收益。

審核編輯 :李倩

-

半導體

+關注

關注

334文章

27063瀏覽量

216494 -

晶體管

+關注

關注

77文章

9641瀏覽量

137876 -

銅線

+關注

關注

2文章

56瀏覽量

16804

原文標題:銅互連,還能撐多久?

文章出處:【微信號:深圳市賽姆烯金科技有限公司,微信公眾號:深圳市賽姆烯金科技有限公司】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

光纜用銅嗎

集成電路的互連線材料及其發展

銅包銀和無氧銅網線哪個好

無氧銅和銅包鋁的網線哪個好用

銅互連,尚能飯否?

銅激光焊接技術篇——銅激光焊接難點分析

銅互連,還能撐多久?

銅互連,還能撐多久?

評論