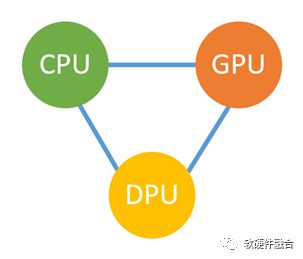

CPU、GPU和DPU是數據中心的三大芯片,通常情況下:CPU主要用于業務應用的處理,GPU用于性能敏感業務的彈性加速,而DPU則是基礎設施加速。站在CPU的視角:一開始所有事情都是我的,然后GPU從我這“搶”過去了一部分工作,現在又出現個DPU來跟我“搶食”。是可忍孰不可忍,必須堅決反擊!

01CPU視角看硬件加速

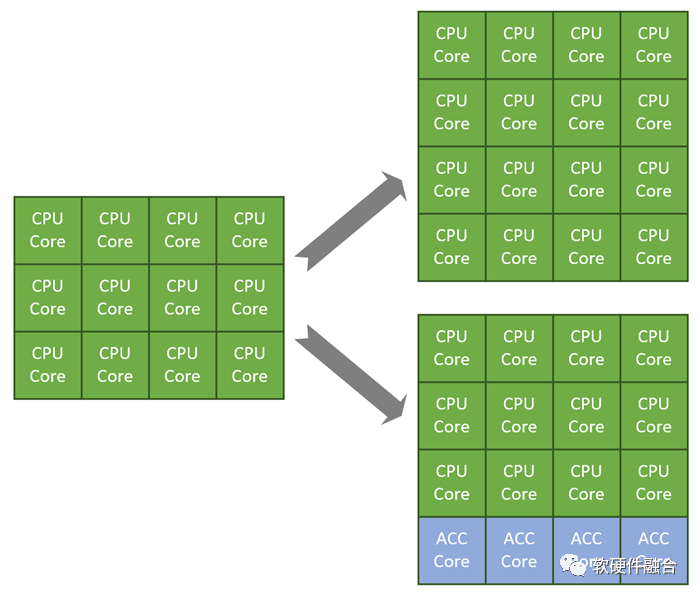

站在CPU視角,最開始,一切處理都通過處理器CPU的常規指令集完成。隨著CPU性能瓶頸,需要硬件加速的方式來提升性能。硬件加速大致有如下幾種方式:

方式1:實現支持擴展指令集的協處理器,實現一定程度的加速能力。比如Intel集成的AVX和AMX指令集,ARM的NEON指令集等。

方式3:獨立的多架構集成加速器。比如DPU。

方式4:即將開始的一種方式,集成單個或多個加速器。

這里需要大家區分兩個概念:處理器核和處理器芯片。處理器芯片是由同構或異構的處理器核組成的。

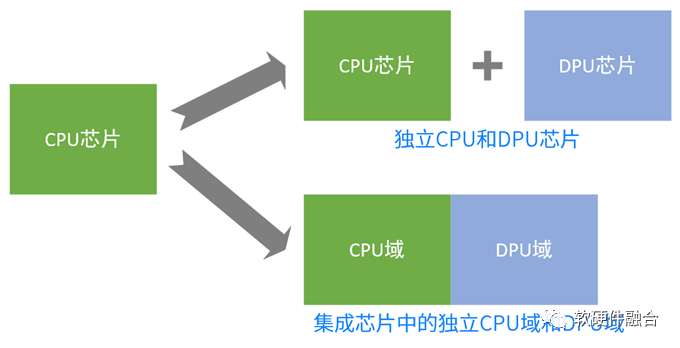

CPU已經到了性能瓶頸,這是大家的共識;當CPU遇到性能瓶頸的時候,通過加速的方式進一步提升性能,也是大家的共識。但是,加速的實現形態,是分立的多個芯片,還是集成的單個芯片,就是“仁者見仁智者見智”的事情了。獨立的DPU公司會認為,獨立的DPU有很多的優勢;但是在CPU廠家而言,通過CPU集成加速器核,使得CPU成為某種程度上的類SOC芯片,也是完全可行的。

02獨立DPU的價值基礎并不牢靠

DPU作為獨立的集成加速平臺,其價值可以從四個方面進行闡述:

價值一:為了進一步提升性能,DPU實現CPU工作任務的卸載和加速;

價值二:從I/O的硬件虛擬化(也可以看做是I/O模擬的硬件卸載)開始,DPU實現I/O模擬、I/O Workload以及整個虛擬化和基礎設施層的全量卸載和加速;

價值三:從運維和管理視角,DPU重要的價值在于實現了業務和基礎設施分離,實現了業務主機的安全訪問;

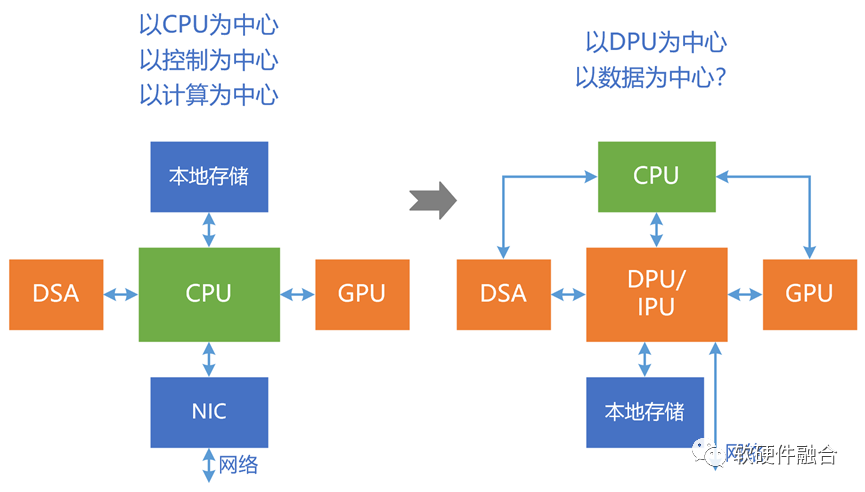

價值四:面向更大計算量和數據吞吐量,DPU實現從“以計算為中心”到“以數據為中心”。

DPU的前三個價值,其實現:可以是獨立的DPU芯片實現,也可以是集成的DPU域實現。這對功能和特征沒有任何影響,甚至集成的方式,還有一些優勢:優化訪問效率,提升性能;集成芯片進一步降低成本和功耗。

DPU的第四個價值,一方面,和獨立或集成無關,也就是說獨立或集成都可以;另一方面,DPU并不一定能夠實現以數據為中心的價值。

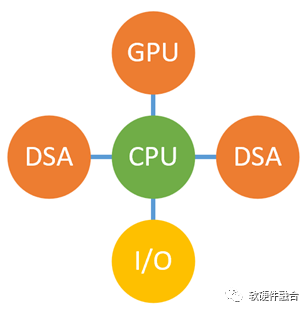

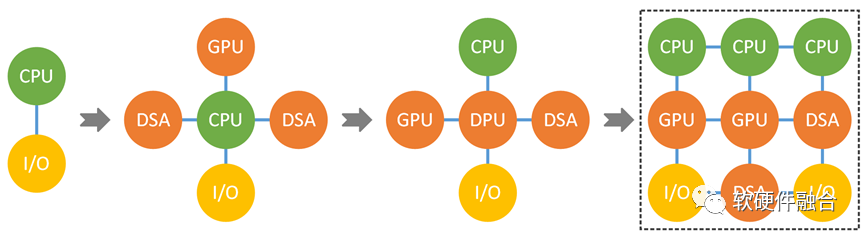

上面這張圖,通常把左邊的稱為“以計算為中心”,右邊的稱為“以數據為中心”。然而,這種表述是有問題的。嚴格來說,左邊稱為“以CPU為中心”、“以控制為中心”或者“以計算為中心”是可以的,右邊這張圖稱為“以DPU為中心”是合適的,但如果稱為“以數據為中心”則是不準確的。“以DPU為中心”并不一定等于“以數據為中心”,“以DPU為中心”,完全可能是“以‘CPU’為中心”,或者說是“以計算為中心”。

最終的結論是:很多DPU其實并非嚴格意義上的數據驅動處理器,并且即使DPU是數據驅動的,依然無法保證整個計算機系統是完全數據驅動的。

03Intel Sapphire Rapids CPU介紹

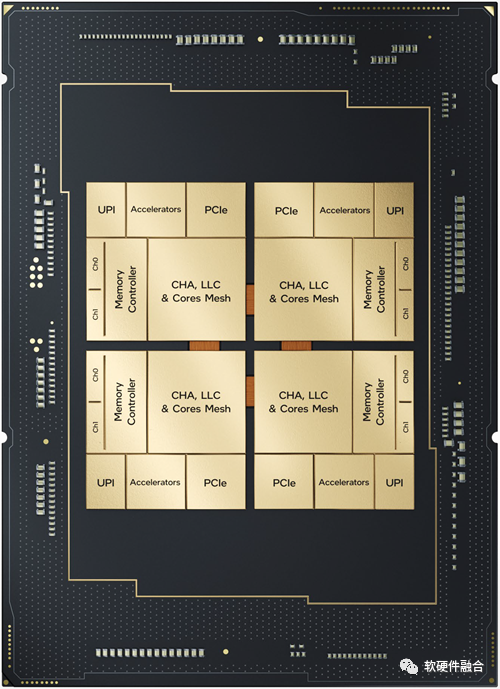

Sapphire Rapids是Intel新一代的數據中心CPU,用于接替Ice Lake。Sapphire Rapids相比Ice lake,從單個TILE變成了4個TILE的Chiplet集成。

Sapphire Rapids可以提供更高的單節點性能:

處理器方面,如更高性能的微架構實現、更多的內核數量、AMX擴展、多個集成的加速引擎等;

存儲方面,如更大的私有/共享緩存、DDR5/HBM等;

I/O方面,如采用PCIe 5.0、UPI2.0、支持新一代Optane等;

Chiplet封裝:EMIB總線實現多TILE集成。

除了單芯片的性能提升之外,Sapphire Rapids還提供更高的數據中心整體性能,例如快速VM遷移、更強的遙測能力、更強的I/O虛擬化、緩存和內存性能一致性、新一代QoS、CXL1.1、更加的彈性,以及提升資源利用率等等。

而Sapphire Rapids的最大創新則是:AIA。通過AIA集成多種加速引擎,包括數據流加速器DSA(Data Stream Accelerator,不是Domain Specific Architecture)、QAT等。我們將在接下來的一節對AIA詳細介紹。

04Intel里程碑:AIA

4.1 背景知識:加速器接口/架構

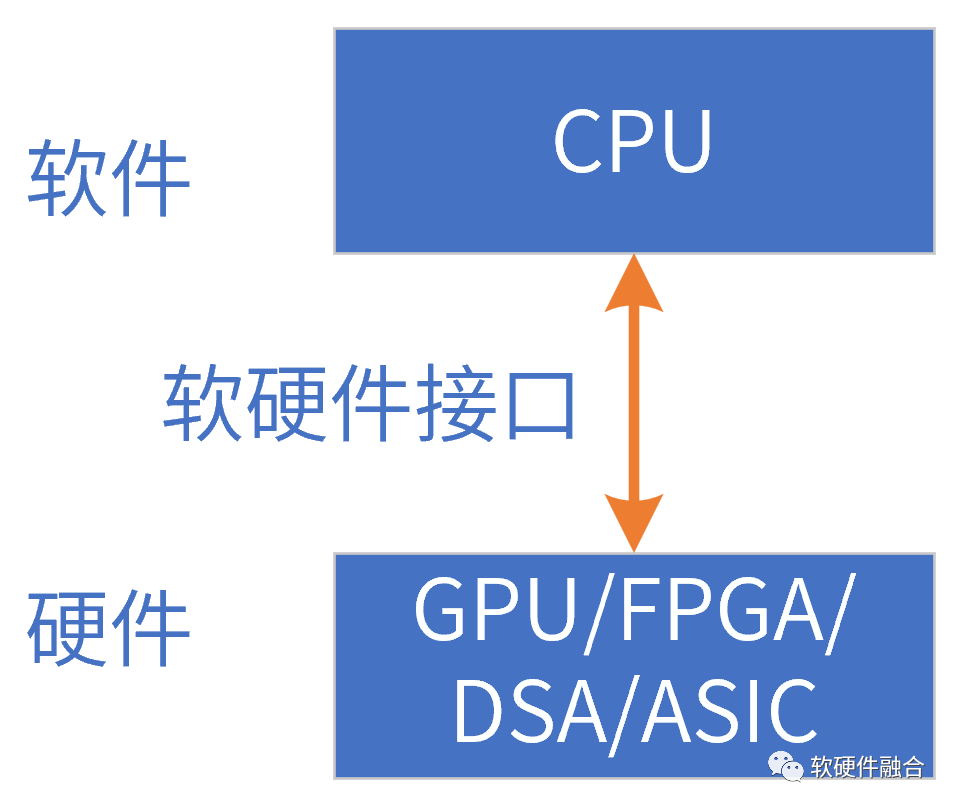

相對于CPU,其他類型的處理器,都可以稱為加速處理器,如:GPU、DSA和ASIC等(FPGA需要具體的處理器實現)。這些加速器都是非圖靈完備的,因此都需要和CPU組合成Host CPU+xPU的異構計算方式工作。

加速器接口,也即加速器呈現給Host CPU的軟件訪問接口,也可以稱為加速器架構。在這里,架構和接口的概念是等同的。

4.2 AIA技術介紹

AIA(Accelerator interfacing Architecture,加速器接口架構)不是一個簡單的功能或特征實現,而是一組相關技術能力的組合(類比Intel的VT-x和VT-d技術)。從Intel新一代Xeon處理器Sapphire Rapids開始,提供加速接口技術AIA,其技術點包括如下:

任務分配指令(MOVDIRI、MOVDIR64B、ENQCMD/S)用于優化任務卸載,ENQCMD/S支持共享任務隊列;

用戶態等待指令(UMONITOR、UMWAIT、TPAUSE),用于高效同步;

低延遲用戶態中斷;

共享虛擬內存;

輕量的可擴展I/O虛擬化S-IOV。

AIA目前支持的加速類型有:數據流處理DSA、加解密和數據壓縮QAT等。

4.3 Intel AIA的戰略意圖分析

作為全能型的處理器,通吃整個計算市場幾十年的CPU,面臨性能瓶頸的巨大挑戰。于是,各種加速處理器,如GPU、DPU等,都在拼命地“挖CPU的墻角”。

作為CPU的霸主,Intel肯定不會“坐以待斃”,一定會“奮起反擊”。AIA就是Intel準備的“核彈”級的武器,AIA是Intel CPU的重要里程碑,其戰略意圖(可能)是:

捍衛CPU的核心地位,所有的一切加速器都需要圍繞著CPU技術生態展開;

Intel試圖通過AIA統一加速器接口、架構和生態。以GPU作為案例:一方面GPU是獨立的架構和生態,與CPU架構是解耦的,可以基于x86架構,也可以遷移到ARM或RISCv架構;另一方面,GPU架構是各自封閉的,NVIDIA有自己的架構和生態,AMD有自己的架構和生態。AIA也許無法把所有的不同加速器類型都統一到一個標準的AIA,但是把GPU統一一個,各種領域加速器DSA各統一一個,是完全可能并且技術上可行的。

一些常見的、關鍵的加速器,就自己搞定,集成到CPU中,比如Sapphire Rapids集成了數據流處理DSA(DSA可以把很多數據處理類的加速統一進來,如網絡和存儲等)和QAT,未來再集成AI、網絡、存儲、虛擬化卸載、安全等基礎設施層處理(也即DPU覆蓋的范疇)功能或加速器,其可能性也是非常的高。

05Intel CPU的未來發展分析

CPU發展的幾個重要里程碑:

里程碑0:CPU的出現。基于簡單運算指令的通用處理器,實現軟件和硬件的完全解耦。從此后,軟件作為獨立的工作領域而存在,軟件開發人員不用關心硬件細節。

里程碑1:多核CPU,從串行計算走向并行計算。

里程碑2:VT-x和VT-d等CPU硬件虛擬化技術,實現無性能損耗的多租戶多系統的獨立運行;

里程碑3:AIA技術的出現,通過AIA,支持獨立或集成加速器,并且規范加速器的接口/架構和生態。

Sapphire Rapids的出現,第一次從CPU的視角,試圖統一各種加速器和CPU的控制和數據交互方式,也即加速器呈現給Host CPU的架構。未來,AIA的方式能否成功,大家拭目以待。

硬件加速,不管是獨立或集成的加速引擎/芯片,都是可行的路徑。但拋開具體的芯片實現,在架構上,硬件加速的形態會再往何處發展?這里我們拋磚引玉:

標準的交互(Host CPU和加速器的接口或稱為架構),統一加速器架構。可能無法把不同類型的加速器統一,但同類型的架構走向統一。

標準交互的同時,需要開放,需要跟CPU架構解耦,可以跨不同的CPU架構實現同樣的交互協議;

基于標準的交互,基于一定的機制,要實現業務應用的跨處理器類型運行。

Intel Sapphire Rapids,代表著CPU的一個重要的發展趨勢是:CPU芯片不斷融合各類加速器核,使得自己成為更加綜合和均衡的新型處理器。

06CPU、GPU、DPU,

從競爭/協同到混戰/融合

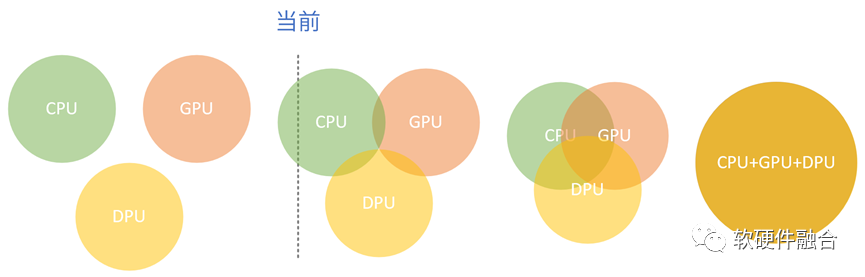

目前,CPU、GPU和DPU,數據中心的三大芯片,從“井水不犯河水”,走向“跨越邊界,侵入對方領地”的混戰階段。

CPU、GPU和DPU,既是協同的關系,又是競爭的關系。三者處于一個動態平衡的狀態,在協同中競爭,在競爭中協同。這個趨勢不斷發展,走向更加深度地協同甚至融合。

從CPU單個處理器的“合”,走向眾多加速器的“分”,再“從分到合”,逐步融合成一個新型的超級處理器。

審核編輯 :李倩

-

cpu

+關注

關注

68文章

10826瀏覽量

211160 -

SoC芯片

+關注

關注

1文章

608瀏覽量

34870 -

DPU

+關注

關注

0文章

354瀏覽量

24129

原文標題:Intel Sapphire Rapids CPU,吹響反攻DPU的號角

文章出處:【微信號:算力基建,微信公眾號:算力基建】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

RAPIDS cuDF將pandas提速近150倍

【「算力芯片 | 高性能 CPU/GPU/NPU 微架構分析」閱讀體驗】--全書概覽

數據中心應用中適用于Intel Xeon Sapphire Rapids可擴展處理器的負載點解決方案

數據中心應用中適用于Intel? Xeon? Sapphire Rapids可擴展處理器的負載點解決方案

Intel預告下一代至強處理器:Diamond Rapids攜LGA9324接口震撼登場

IaaS+on+DPU(IoD)+下一代高性能算力底座技術白皮書

SAPPHIRE SF NX 簡介

明天線上見!DPU構建高性能云算力底座——DPU技術開放日最新議程公布!

拓維信息吹響龍年沖鋒第一聲號角

Intel酷睿Ultra CPU IPC性能實測

Intel Sapphire Rapids CPU,吹響反攻DPU的號角

Intel Sapphire Rapids CPU,吹響反攻DPU的號角

評論