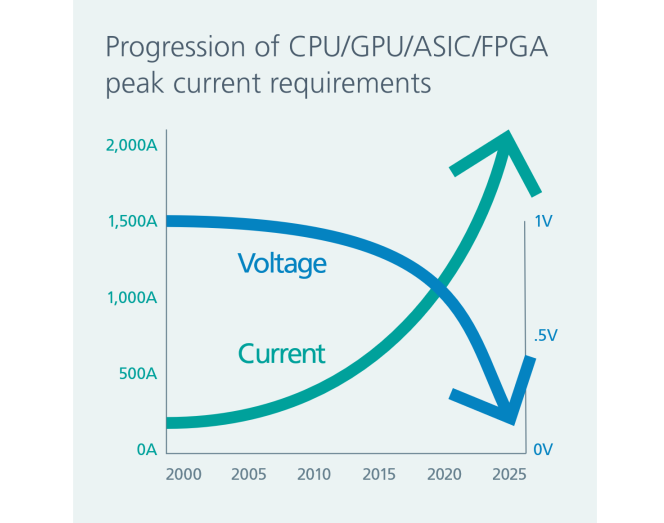

隨著先進工藝節(jié)點的出現(xiàn),高性能人工智能 (AI) 處理器的功率不斷上升,內(nèi)核電壓則在不斷下降。這些發(fā)展給電源系統(tǒng)設(shè)計人員帶來很大挑戰(zhàn),例如需要管理因為供電網(wǎng)絡(luò) (PDN) 阻抗壓降不斷上升的而引起大電流低電壓處理器電源引腳間的電壓梯度、瞬態(tài)性能規(guī)格以及功耗等難題。

圖 1:晶體管幾何尺寸及核心電壓的降低導(dǎo)致電流需求急劇上升。

以集群計算為例,緊密排列的處理器陣列可提高機器學(xué)習(xí)的速度和性能。PDN 的復(fù)雜性顯著增加,因為電流傳輸必須從陣列的下方垂直進行。設(shè)計 PDN 時在負載點使用 Vicor 分比式電源架構(gòu) (FPA)和電流倍增器, 代替?zhèn)鹘y(tǒng)平均功率技術(shù),可顯著提高性能。這要歸功于高品質(zhì)的負載點 (PoL) 電源組件:高電流密度、組件數(shù)更少,而且更為重要的是高度靈活的布置。因此,PoL 電源組件可為 AI 處理器內(nèi)核和存儲器實現(xiàn)橫向或垂直傳輸電流,是因為最大限度降低 了 PDN 阻抗。

現(xiàn)代 GPU 有數(shù)百億個晶體管。增加處理器性能的代價是,呈指數(shù)級增長的電源需求。在大多數(shù)情況下,供電現(xiàn)已成了計算性能的限制因素。供電不僅涉及配電,而且還涉及效率、規(guī)模、成本和散熱性能。

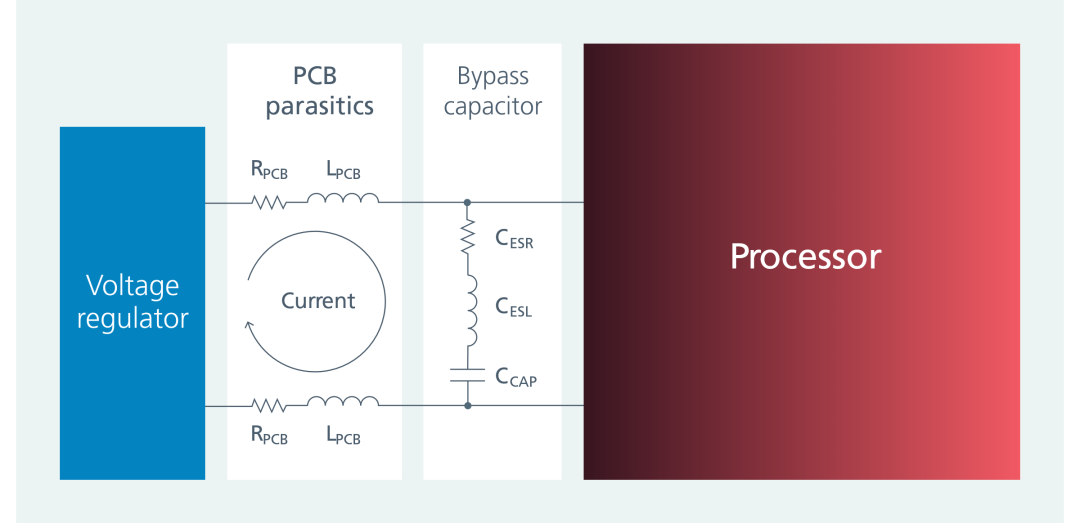

圖 2:典型高性能處理器 PDN 的架構(gòu)。

目前典型的 GPU 峰值電流的需求高達 2000A。為響應(yīng)這些需求,一些 xPU 公司正在評估多路供電方案,將主要內(nèi)核供電線路分成五組以上較小電流電源輸入。每個線路的 PDN 在經(jīng)歷單獨嚴格穩(wěn)壓的同時,仍須提供大電流,這為 PDN 的密度及其在加速卡上的物理位置帶來了壓力。

高度動態(tài)性的機器學(xué)習(xí)工作負載將導(dǎo)致持續(xù)數(shù)微秒的高 di/dt 瞬態(tài),進一步增加了這種復(fù)雜性。這些瞬態(tài)將在高性能處理器模塊或加速卡的 PDN 處理上產(chǎn)生很大挑戰(zhàn)。

開放式計算項目 (OCP) 聯(lián)盟的工作有助于建立基于機架及板卡的處理器開發(fā)標準框架。開放式機架標準 V2.2 為主要用于 AI 和機器學(xué)習(xí)工作負載的開放式加速器模塊 (OAM) 定義了 48V 服務(wù)器背板和 48V 工作電壓。為了保持與原有 12V 系統(tǒng)的兼容性,該標準規(guī)定了符合 12 至 48V 及 48 至 12V 要求的性能。

技術(shù)進步主要集中在電壓值調(diào)節(jié)的下降趨勢、對內(nèi)核電壓精度的要求更趨嚴格以及電流的上升趨勢。在電路板層面,這些因素的影響以多種方式體現(xiàn)。

遇到的峰值電流密度對任何 PCB 都很極端。對能處理這些巨大負載的電源路徑進行布線的任務(wù)需要格外注意。高動態(tài)工作負載會產(chǎn)生尖峰瞬態(tài)電壓,這些尖峰電壓對精密的處理器具有潛在的破壞性。然而,一個處理器電路板有數(shù)百個其它的無源組件、存儲器以及對運行至關(guān)重要的 IC,它們也需要放置它們。

然后就是 I2R 損耗:電源路徑長度一定要短,因此電源轉(zhuǎn)換模塊應(yīng)該盡量靠近處理器,處理器就近取得電流并減少熱量消耗。

分比式電源架構(gòu)

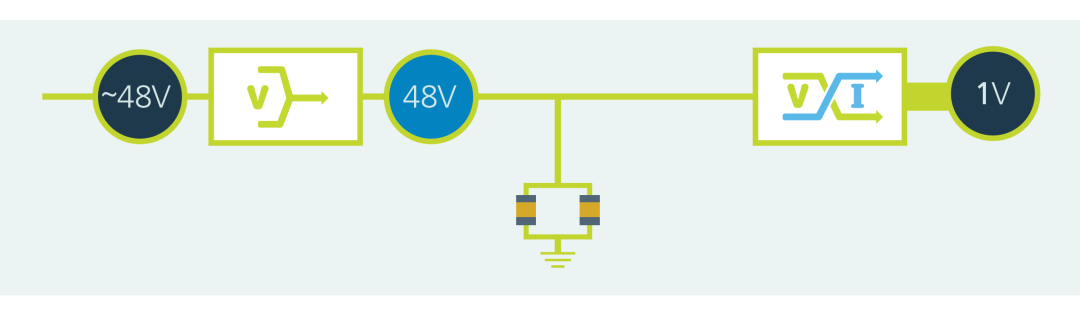

圖 3:分比式電源架構(gòu) (FPA) 將電源分解為專門的穩(wěn)壓和變壓功能。這兩個功能都可以單獨優(yōu)化和部署,以提供高功率密度和高效率。

全新的理念、架構(gòu)、拓撲和技術(shù)可提供一條通向更可靠的可擴展 PDN 的道路。Vicor 分比式電源架構(gòu) (FPA) 是為當下前所未有的高性能計算需求提供更高效電源的基礎(chǔ)。

Vicor FPA 將電源轉(zhuǎn)換器的任務(wù)劃分為穩(wěn)壓和變壓的不同專用功能。將這兩種功能分開,可對其進行單獨優(yōu)化,以實現(xiàn)高效率及高密度。FPA與正弦振幅轉(zhuǎn)換器 (SAC)拓撲共同支撐了多個創(chuàng)新的電源架構(gòu),幫助釋放當前處理器的高性能。

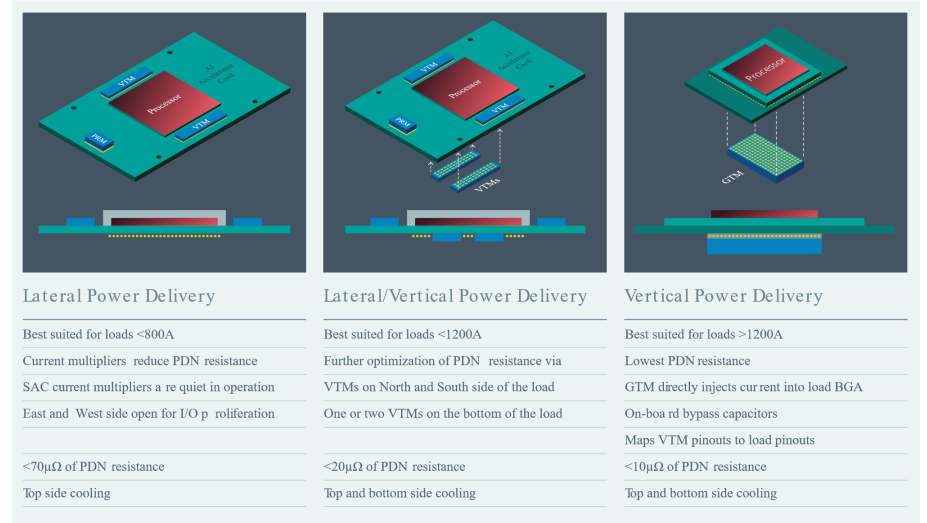

圖 4:Vicor 利用 FPA,可通過橫向供電 (LPD) 和垂直供電 (VPDd) 最大限度降低“最后一英寸”電阻。在 LPD 中,兩個電流倍增器(Vicor VTM 模塊)位于處理器的南北側(cè)或東西側(cè)。該技術(shù)適用于標稱電壓為 0.8V 時約 800A 的負載電流,在 100°C 下,PDN 的相關(guān)電阻為 70μΩ。使用這些數(shù)字,我們可以計算大約 45W 的功耗。覆蓋 2.8 毫米高的電流倍增器和處理器的散熱器有助于散熱。點擊圖片放大。

橫向供電是一項創(chuàng)新技術(shù),其中兩個電流倍增器(Vicor VTM 模塊)位于處理器的南北側(cè)或東西側(cè)。該技術(shù)適用于標稱電壓為 0.8V 時約 800A 的負載電流,在 100°C 下,PDN 的相關(guān)抗阻為 70μΩ。這種架構(gòu)非常適合為圖形加速卡(OAM 或其它產(chǎn)品)供電,并用于為超大規(guī)模數(shù)據(jù)中心或超級計算機機柜 的 ASIC 和 APU 聯(lián)網(wǎng)。

橫向-垂直供電技術(shù)與橫向供電技術(shù)相似,但也有一點差異:只有 70% 的功率是通過處理器側(cè)面的電流倍增器橫向傳輸?shù)摹L幚砥鞯撞康牧硪粋€電流倍增器將剩余 30% 的負載電流直接傳輸至處理器 BGA。橫向和縱向的混合可將 PDN 損耗銳減至原來的四分之一!此外,該技術(shù)還可釋放電路板空間,以容納電路板頂部處理器的次級大電流(aux) 軌或 HBM 存儲軌。

另一方面,垂直- 橫向供電還可通過增加處理器底部的電流倍增器數(shù)量來分擔接近超過 50% 的負載電流。與橫向-縱向方案相比,該技術(shù)可使 PDN 損耗再減一半。一個 1200A 的設(shè)計現(xiàn)在可實現(xiàn)僅 10μΩ 的 PDN 抗阻,從而可實現(xiàn)小于 14.4W 的功耗。在這種情況下,散熱器可在空間允許的情況下為負載的頂部和底部散熱。這種架構(gòu)對于那些必須容納來自電路板頂部 ASIC 外圍的高速信號路由的應(yīng)用特別有效,因此在那里無法放置更多電源組件,例如 CPO、NPO 以及網(wǎng)絡(luò)/寬帶通信器件。

垂直供電是以最低 PDN 抗阻在處理器內(nèi)核低電壓下提供大電流的最終方式。在這種情況下,電流倍增器和旁路電容器一起堆疊,形成一個集成電源模塊(Pin 針重新適配的變速電流倍增器),可取代旁路電容器組合,直接安裝在處理器下面。Vicor GCM 是量身定制的器件,不僅可將電流倍增器插腳引線映射至 AI 處理器 BGA,而且還可提供模塊本身所需的所有旁路電容器。這種技術(shù)使得那種需要處理器外圍的 PCB 布滿高速信號路由的應(yīng)用更為方便,例如CPO(合封光學(xué)器件、網(wǎng)絡(luò)處理器)和高速信號 ASIC 等應(yīng)用可以利用這種供電技術(shù)。

Vicor 架構(gòu)非常靈活,完全能夠適應(yīng)各種高性能計算場景。Vicor 架構(gòu)可將主板抗阻銳降至 1/50,還可將處理器電源引腳數(shù)銳減至 1/10 以下。利用 FPA功率分比架構(gòu),Vicor 可通過將橫向供電 (LPD) 和垂直供電 (VPD)完美結(jié)合,最大限度減少“最后一英寸”抗阻。所有這些均可幫助處理器實現(xiàn)以前無法實現(xiàn)的性能,為呈指數(shù)級增長的 HPC 處理需求提供有力支持。

FPA 架構(gòu)在電流密度以及降低 PDN 功耗方面是無與倫比的。專有的架構(gòu)、拓撲和小巧的模塊尺寸在電源行業(yè)中獨一無二。新一代處理器需要能夠適應(yīng)、擴展并能提供高密度電源的電源架構(gòu)。在電源需求日新月異的動態(tài)系統(tǒng)中,結(jié)合創(chuàng)新拓撲、穩(wěn)健而可靠的電源模塊必不可少。為了滿足這一永恒需求,不僅需要創(chuàng)新,而且還需要能夠使用模塊化電源來適應(yīng)和擴展未來應(yīng)用。

審核編輯 :李倩

-

數(shù)據(jù)

+關(guān)注

關(guān)注

8文章

6909瀏覽量

88850 -

散熱器

+關(guān)注

關(guān)注

2文章

1056瀏覽量

37495 -

Vicor

+關(guān)注

關(guān)注

4文章

191瀏覽量

58405

原文標題:垂直供電助力尖端數(shù)據(jù)處理

文章出處:【微信號:Vicor,微信公眾號:Vicor】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

eda中常用的數(shù)據(jù)處理方法

海量數(shù)據(jù)處理需要多少RAM內(nèi)存

FPGA在數(shù)據(jù)處理中的應(yīng)用實例

實時數(shù)據(jù)處理的邊緣計算應(yīng)用

天拓四方:工業(yè)數(shù)據(jù)采集網(wǎng)關(guān)在智能邊緣計算與實時數(shù)據(jù)處理的應(yīng)用

邊緣計算物聯(lián)網(wǎng)關(guān)如何優(yōu)化數(shù)據(jù)處理流程

巖土工程監(jiān)測中振弦采集儀數(shù)據(jù)處理與解讀的挑戰(zhàn)與方法

振弦采集儀在巖土工程監(jiān)測中的數(shù)據(jù)處理與結(jié)果展示

工程監(jiān)測振弦采集儀在振動監(jiān)測中的應(yīng)用與數(shù)據(jù)處理技術(shù)

工程監(jiān)測領(lǐng)域振弦采集儀的數(shù)據(jù)處理與分析方法探討

工程監(jiān)測中振弦采集儀的數(shù)據(jù)處理方法研究

數(shù)據(jù)處理

虹科方案 | 車內(nèi)智慧大腦:基于車載網(wǎng)絡(luò)捕獲的全景數(shù)據(jù)處理

垂直供電助力尖端數(shù)據(jù)處理

垂直供電助力尖端數(shù)據(jù)處理

評論