數(shù)字門級(jí)電路可分為兩大類:組合邏輯和時(shí)序邏輯。鎖存器是組合邏輯和時(shí)序邏輯的一個(gè)交叉點(diǎn),在后面會(huì)作為單獨(dú)的主題處理。

組合邏輯描述了門級(jí)電路,其中邏輯塊的輸出直接反映到該塊的輸入值的組合,例如,雙輸入AND門的輸出是兩個(gè)輸入的邏輯與。如果輸入值發(fā)生變化,輸出值將反映這一變化,組合邏輯的RTL模型需要反映這種門級(jí)行為,這意味著邏輯塊的輸出必須始終反映該邏輯塊當(dāng)前輸入值的組合。

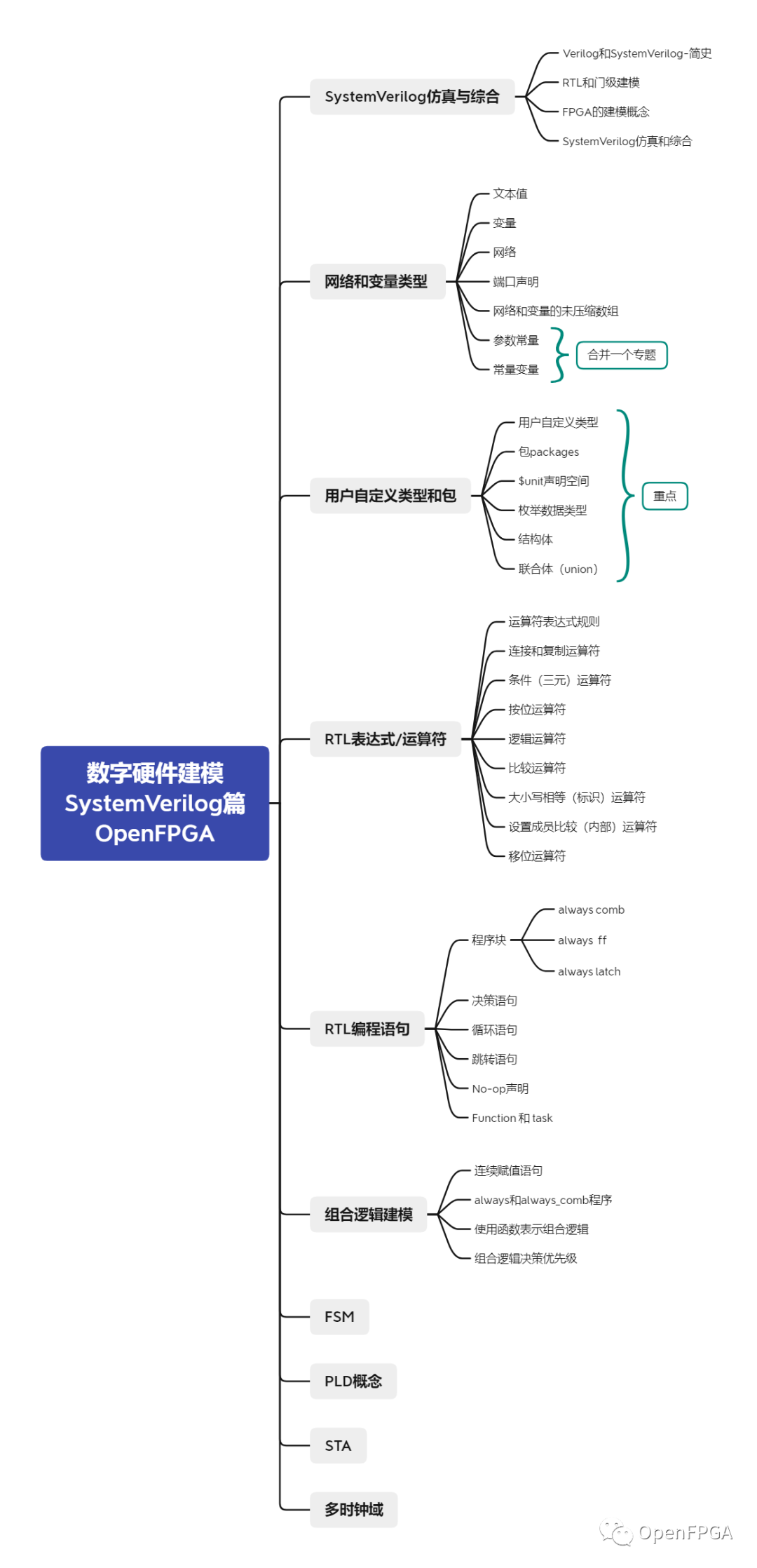

SystemVerilog有三種在可綜合RTL級(jí)別表示組合邏輯的方法:連續(xù)賦值語(yǔ)句、always程序塊和函數(shù)。接下來(lái)幾篇文章將探討每種編碼風(fēng)格,并推薦最佳實(shí)踐編碼風(fēng)格。

使用函數(shù)表示組合邏輯

當(dāng)編碼正確時(shí),函數(shù)的行為和綜合就像組合邏輯一樣。

| 最佳實(shí)踐指南7-7 |

|---|

| 將RTL模型中使用的函數(shù)聲明為自動(dòng)automatic。 |

為了表示組合邏輯行為,每次調(diào)用函數(shù)時(shí)都必須計(jì)算一個(gè)新的函數(shù)返回值。如果調(diào)用了靜態(tài)函數(shù),但沒(méi)有指定返回值,則靜態(tài)函數(shù)將隱式返回其上一次調(diào)用的值。這是鎖存邏輯的行為,而不是組合邏輯。通過(guò)將RTL模型中使用的所有函數(shù)聲明為自動(dòng)函數(shù)(automatic),可以避免這種編碼錯(cuò)誤。

例7-2定義了一個(gè)使用Russian Peasant Multiplication算法(一系列加法和移位運(yùn)算)計(jì)算乘法運(yùn)算的函數(shù)。該函數(shù)被定義在一個(gè)包中,任何模塊都可以使用該乘法器算法。

SystemVerilog會(huì)推斷出一個(gè)與函數(shù)名稱和數(shù)據(jù)類型相同的變量,示例7-2中的代碼就是利用了這一點(diǎn)。函數(shù)名multiply_f被用作臨時(shí)變量來(lái)保存for循環(huán)中的中間計(jì)算結(jié)果,函數(shù)名中存儲(chǔ)的最終值在函數(shù)退出時(shí)成為函數(shù)返回值。

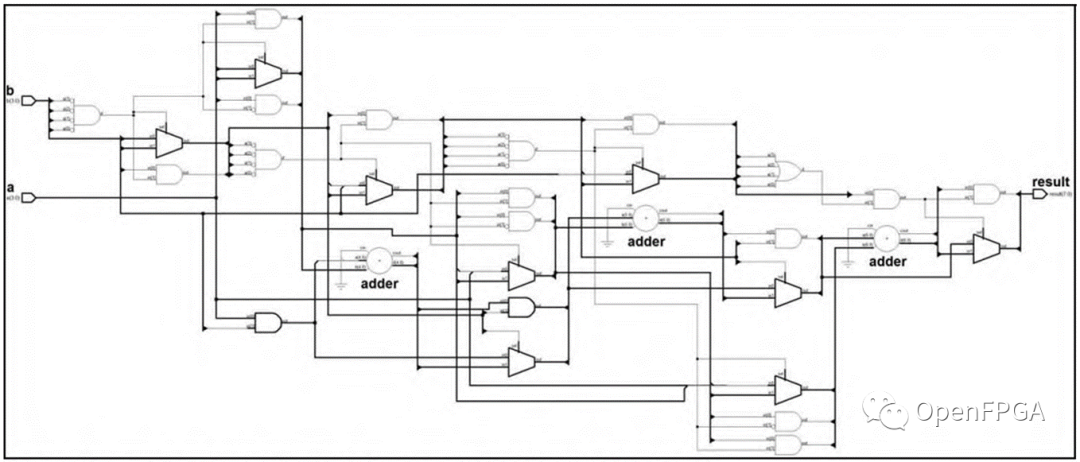

圖7-2顯示了綜合該函數(shù)的結(jié)果,以及從連續(xù)賦值語(yǔ)句調(diào)用該函數(shù)的模塊。

示例7-2:定義乘法運(yùn)算的算法函數(shù)

//`begin_keywords"1800-2012"http://useSystemVerilog-2012keywords packagedefinitions_pkg; timeunit1ns;timeprecision1ns; //RussianPeasantMultiplicationAlgorithm functionautomatic[7:0]multiply_f([7:0]a,b); multiply_f=0; for(inti=0;i<=3;?i++)?begin? ??????if?(b?==?0)?continue;?//?all?done,?finish?looping ??????else?begin? ?????????if?(b?&?1)?multiply_f?+=?a; ?????????a?<<=?1;??//?multiply?by?2 ?????????b?>>=1;//divideby2 end end endfunction endpackage:definitions_pkg //`end_keywords //`begin_keywords"1800-2012"http://useSystemVerilog-2012keywords modulealgorithmic_multiplier importdefinitions_pkg::*; (inputlogic[3:0]a,b, outputlogic[7:0]result ); timeunit1ns;timeprecision1ns; assignresult=multiply_f(a,b); endmodule:algorithmic_multiplier //`end_keywords圖7-2:示例7-2的綜合結(jié)果:作為組合邏輯的函數(shù)

| 最佳實(shí)踐指南7-8 |

|---|

| 在可能的情況下,使用SystemVerilog運(yùn)算符,如*,而不是使用循環(huán)和其他編程語(yǔ)句。 |

算法乘法器的示例7-2還說(shuō)明了為什么在乘法和除法等復(fù)雜運(yùn)算中最好使用SystemVerilog運(yùn)算符。如果在示例7-2中使用了乘法運(yùn)算符(*),則綜合編譯器可以將該運(yùn)算符映射到ASIC或FPGA的最有效的乘法器。

設(shè)計(jì)工程師在使用算術(shù)運(yùn)算符或算法來(lái)表示復(fù)雜操作時(shí)需要謹(jǐn)慎。RTL模型不是在具有大量?jī)?nèi)存資源的通用計(jì)算機(jī)上運(yùn)行的軟件程序。RTL模型是門級(jí)實(shí)現(xiàn)的抽象。所表示的功能需要在物理上適合目標(biāo)ASIC或FPGA,并且在時(shí)間上在有限的數(shù)量或時(shí)鐘周期內(nèi)。之前的文章有詳細(xì)介紹了在RTL模型中使用算術(shù)運(yùn)算符(如乘法和除法)的指導(dǎo)原則。

審核編輯:郭婷

-

鎖存器

+關(guān)注

關(guān)注

8文章

904瀏覽量

41444 -

組合邏輯

+關(guān)注

關(guān)注

0文章

47瀏覽量

10033 -

and

+關(guān)注

關(guān)注

0文章

32瀏覽量

7242

原文標(biāo)題:使用函數(shù)表示組合邏輯

文章出處:【微信號(hào):Open_FPGA,微信公眾號(hào):OpenFPGA】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

使用函數(shù)表示組合邏輯的方法

使用函數(shù)表示組合邏輯的方法

評(píng)論