時序約束條件

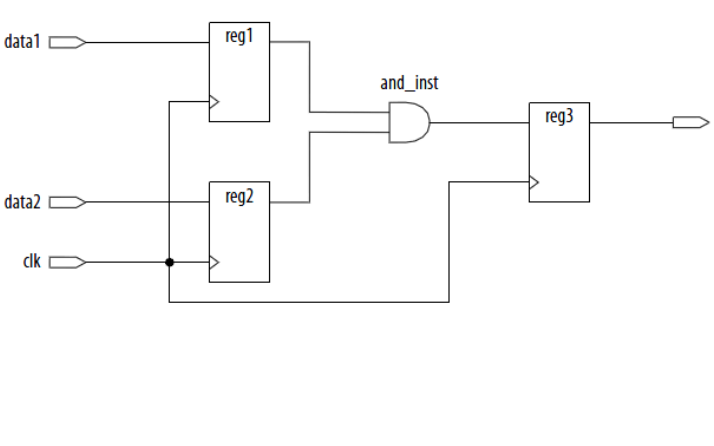

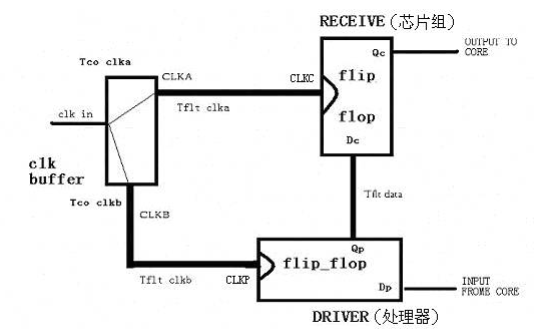

下面來具體討論一下系統時序需要滿足的一些基本條件。我們仍然以下圖的結構為例,并可以據此畫出相應的時序分析示意圖。

在上面的時序圖中,存在兩個時序環,我們稱實線的環為建立時間環,而虛線的環我們稱之為保持時間環。可以看到,這兩個環都不是閉合的,缺口的大小就代表了時序裕量的多少,因此設計者總希望盡可能增大這個缺口。同時還要注意到,每個環上的箭頭方向不是一致的,而是朝著正反兩個方向,因為整個系統時序是以時鐘上升沿為基準的,所以我們時序環的起點為系統時鐘clk in的上升沿,而所有箭頭最終指向接收端的控制時鐘CLKC的邊沿。

先來分析建立時間環:

缺口的左邊的半個時序環代表了從第一個系統時鐘上升沿開始,直到數據傳輸至接收端的總的延時,我們計為數據延時,以Tdata_tot表示:

Tdata_tot=Tco_clkb+Tflt_clkb +Tco_data +Tflt_data

上式中:Tco_clkb是系統時鐘信號CLKB在時鐘驅動器的內部延遲;Tflt_ clkb 是CLKB從時鐘驅動器輸出后到達發送端(CPU)觸發器的飛行時間;Tco_data是數據在發送端的內部延遲;Tflt_data是數據從發送端輸出到接收端的飛行時間。

從CLKC時鐘邊沿的右邊半個時序環代表了系統時鐘到達接收端的總的沿時,我們計為時鐘延時,以Tclk_tot表示:

Tclk_tot =Tcycle +Tco_clka +Tflt_clka – Tjitter

其中,Tcycle是時鐘信號周期;Tco_clka 是系統時鐘信號CLKA(第二個上升沿)在時鐘驅動器的內部延遲;Tflt_clka是時鐘信號從時鐘驅動器輸出到達接收端觸發器的飛行時間;Tjitter是時鐘的抖動誤差。

因此我們可以根據建立時間裕量的定義,得到:

Tsetup_margin = Tclk_tot – Tdata tot – Tsetup

將前面的相應等式帶入可得:

Tsetup_magrin = Tcycle + Tco_clka + Tflt_clka – Tjitter – Tco_clkb – Tflt_clkb – Tco_data – Tflt_data – Tsetup

我們定義時鐘驅動器(PLL)的兩個時鐘輸出之間的偏移為Tclock_Skew ,兩根CLOCK走線之間的時鐘偏移為TPCB_Skew ,即:

Tclock_Skew = Tco_clkb - Tco_clka;

TPCB_Skew = Tflt_clkb - Tflt_clka

這樣就可以得到建立時間裕量的標準計算公式:

Tsetup_magrin =Tcycle – TPCB_skew –Tclock_skew –Tjitter – Tco_ data -Tflt_data-Tsetup (1.6.1)

再來看保持時間環:

對照上圖,我們可以同樣的進行分析:

Tdata_delay = Tco_clkb + Tflt_clkb + Tco_data + Tflt_data

Tclock delay = Tco_clka + Tflt_clka

于是可以得出保持時間裕量的計算公式:

Thold margin = Tdata_delay – Tclock_dalay – Thold_time

即: Thold margin = Tco_data + Tflt_data + Tclock_skew + Tpcb_skew – Thold (1.6.2)

可以看到,式1.6.2中不包含時鐘抖動Jitter的參數。這是因為Jitter是指時鐘周期間(Cycle to Cycle)的誤差,而保持時間的計算和時鐘周期無關。

對于任何時鐘控制系統,如果要能保證正常工作,就必須使建立時間余量和保持時間裕量都至少大于零,即Tsetup marin 》0;Thold margin 》0,將公式1.6.1和1.6.2分別帶入就可以得到普通時鐘系統的時序約束條件不等式:

TPCB_skew +Tclock_skew +Tjitter + Tco_data + Tflt_data+Tsetup《 Tcycle (1.6.3)

Tco_data + Tflt_data + Tclock_skew + Tpcb_skew 》 Thold (1.6.4)

需要注意的是:

1. 數據在發送端的內部延時Tco_data可以從芯片的datasheet查到,這個值是一個范圍,在式1.6.3中取最大值,在式1.6.4中取最小值。

2.數據在傳輸線上的飛行時間Tflt_data在實際計算中應該取最大/最小飛行時間參數,在式1.6.3中取最大飛行時間,在式1.6.4中取最小飛行時間。

3. 時鐘的偏移TPCB_skew和Tclock_skew也是一個變化的不確定參數,一般為+/-N ps,同樣,在建立時間約束條件1.6.3中取+Nps,而在保持時間約束條件1.6.4中取-Nps。

從上面的分析可以看到,對于PCB設計工程師來說,保證足夠穩定的系統時序最有效的途徑就是盡量減小PCB skew和信號傳輸的飛行時間,而其它的參數都只和芯片本身的性能有關。實際中經常采取的措施就是嚴格控制時鐘和數據的走線長度,調整合理的拓補結構,并盡可能減少信號完整性帶來的影響。然而,即便我們已經考慮的很周全,普通時鐘系統的本身的設計瓶頸始終是無法打破的,也就是建立時間的約束,我們在盡可能減少由PCB布線引起的信號延遲之外,器件本身的特性如Tco、Jitter、TSetup等等將成為最主要的制約因素,盡管我們可以通過提高工藝水平和電路設計技術來不斷提高數字器件的性能,但得到的效果也僅僅是在一定范圍之內提升了系統的主頻,在頻率超過300MHz的情況下,我們將不得不放棄使用這種普通時鐘系統設計。

審核編輯 :李倩

-

FPGA

+關注

關注

1626文章

21678瀏覽量

602035 -

pll

+關注

關注

6文章

775瀏覽量

135054 -

時序圖

+關注

關注

2文章

57瀏覽量

22439 -

時鐘驅動器

+關注

關注

0文章

33瀏覽量

13821

原文標題:FPGA知識匯集-FPGA系統時序理論

文章出處:【微信號:gh_873435264fd4,微信公眾號:FPGA技術聯盟】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

FPGA時序約束的基礎知識

FPGA實戰演練邏輯篇48:基本的時序分析理論1

FPGA時序約束--基礎理論篇

FPGA設計:時序是關鍵

FPGA中的時序約束設計

FPGA時序約束的理論基礎知識說明

FPGA知識匯集-FPGA系統時序理論

FPGA知識匯集-FPGA系統時序理論

評論