Altium Designer 23.0.1

發(fā)布時(shí)間:2022年12月15日

Altium Designer 23.0.1離線包

15天免費(fèi)試用 Altium Designer 22

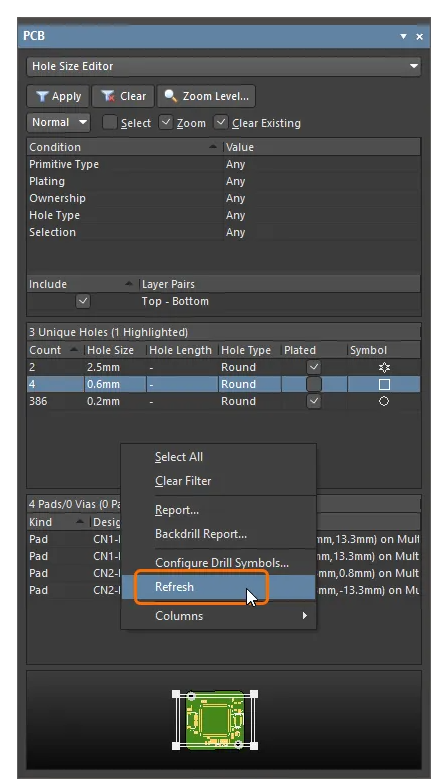

PCB設(shè)計(jì)改進(jìn)

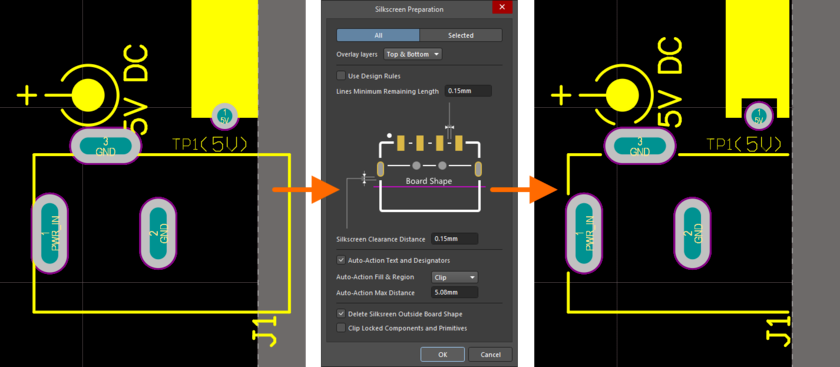

絲印制備

為了幫助解決常見(jiàn)Design for Manufacture(DFM)問(wèn)題,即外露銅皮、孔和板形狀絲印重疊,本次發(fā)布中增加了為電路板制備絲印的專用功能。這些問(wèn)題現(xiàn)在可以通過(guò)以下方式得到有效解決:

絲印線和圓弧自動(dòng)裁剪

填充和區(qū)域的自動(dòng)裁剪或移動(dòng)

絲印文本和元件位號(hào)自動(dòng)移動(dòng)。

可使用主菜單中的Tools ? Silkscreen Preparation命令訪問(wèn)Silkscreen Preparation對(duì)話框,以在PCB封裝編輯器(用于活動(dòng)封裝)和PCB編輯器(跨越一個(gè)或兩個(gè)覆蓋層上的所有或選定對(duì)象)中使用該功能。

如需了解更多信息,請(qǐng)參閱Preparing the Silkscreen on a PCB和Creating a PCB Footprint -Preparing the Silkscreen頁(yè)面。

此功能目前處于Open Beta階段,且僅在Advanced Settings對(duì)話框中啟用PCB.SilkScreenPreparation選項(xiàng)時(shí)可用。

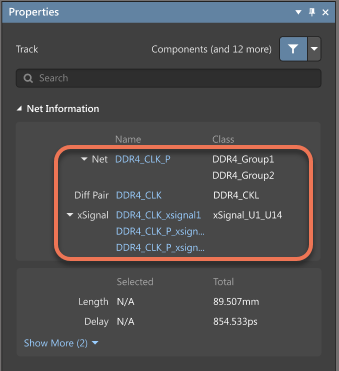

增強(qiáng)版網(wǎng)絡(luò)信息用戶界面

Properties面板的Net Information區(qū)域此時(shí)將顯示所選基元的所有網(wǎng)絡(luò)、差分對(duì)和xSignals。您可以展開(kāi)這些部分,以查看所有列出的信息。

如需了解更多信息,請(qǐng)參閱PCB Placement and Editing Techniques頁(yè)面。

數(shù)據(jù)管理改進(jìn)

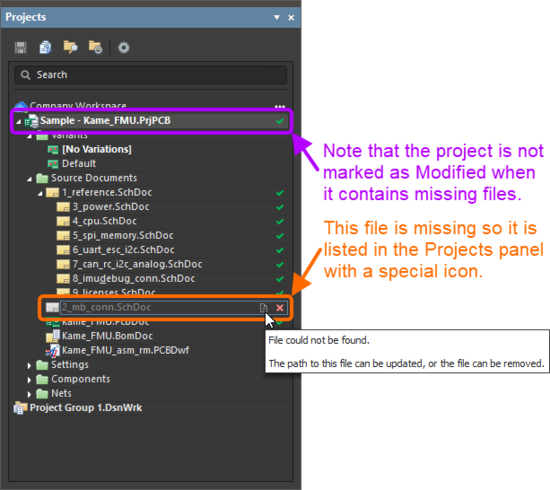

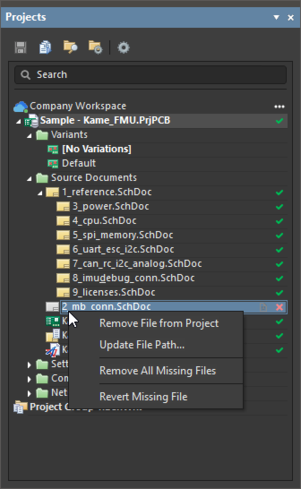

丟失文件管理

以前,丟失文件可在Messages面板中通過(guò)相應(yīng)通知?jiǎng)h除,且在Projects面板中將項(xiàng)目標(biāo)記為已修改。本次發(fā)布中引入一種強(qiáng)化方法,可用于對(duì)在項(xiàng)目文件中定義但在項(xiàng)目文件夾中找不到的文件進(jìn)行管理。這些文件現(xiàn)在被標(biāo)記為‘丟失’,而不是簡(jiǎn)單地將對(duì)此類文件的引用刪除并將項(xiàng)目標(biāo)記為已修改。它們?nèi)匀辉陧?xiàng)目文件中進(jìn)行定義,并且仍顯示在Projects面板的項(xiàng)目結(jié)構(gòu)中,但其以灰色顯示且具有區(qū)分圖標(biāo)。

可以使用關(guān)聯(lián)命令,以確保對(duì)丟失文檔的處理進(jìn)行全面掌控。使用Projects面板中丟失文件的右鍵單擊菜單,從項(xiàng)目中刪除選中文件或所有丟失文件,或者對(duì)文件路徑進(jìn)行更新(即用選中文件替換丟失文件)。對(duì)于受版本控制的項(xiàng)目,您還可以恢復(fù)本地修改以從項(xiàng)目VCS存儲(chǔ)庫(kù)中恢復(fù)丟失文件。

使用項(xiàng)目入口處右鍵單擊菜單中的Add Existing to Project命令,將現(xiàn)有文件添加到項(xiàng)目時(shí),擬添加文件的名稱和路徑與丟失文件的名稱和路徑相同(例如,當(dāng)在Altium Designer中打開(kāi)項(xiàng)目后,將丟失文件添加到項(xiàng)目文件夾中時(shí)可能發(fā)生),將打開(kāi)一個(gè)確認(rèn)對(duì)話框,以詢問(wèn)您是否想要用選中文件替換丟失文件。

如需了解更多信息,請(qǐng)參閱Working with Documents頁(yè)面。

此功能目前處于Open Beta階段,且僅在Advanced Settings對(duì)話框中啟用WSM.ManageMissingFiles選項(xiàng)時(shí)可用。

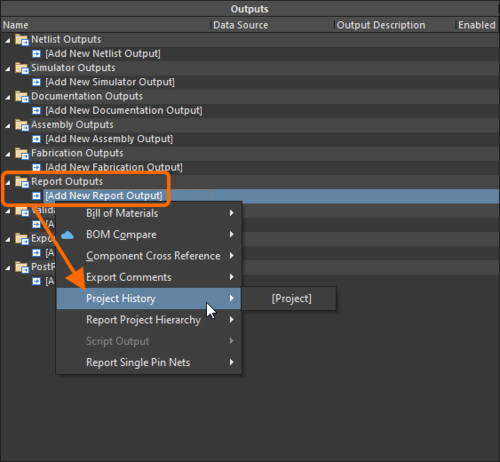

創(chuàng)建項(xiàng)目歷史報(bào)告

此時(shí)可以為Workspace項(xiàng)目,創(chuàng)建Project History PDF報(bào)告。在OutputJob文件(*.OutJob),右鍵單擊與Report Outputs入口關(guān)聯(lián)的[Add New Report Output],然后選擇項(xiàng)目Project History。

然后,可以將新建Project History輸出報(bào)告連接到PDF輸出容器。

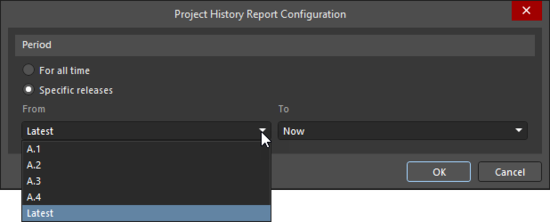

右鍵單擊創(chuàng)建的輸出,然后選中Configure以訪問(wèn)Project History Report Configuration對(duì)話框,并在該對(duì)話框中對(duì)應(yīng)導(dǎo)出報(bào)告的Period進(jìn)行設(shè)置:整個(gè)項(xiàng)目歷史或從/到特定的(或最新的)項(xiàng)目發(fā)布。

添加報(bào)告、鏈接到所需PDF輸出容器并根據(jù)需要進(jìn)行配置后,單擊Generate內(nèi)容或作為項(xiàng)目發(fā)布過(guò)程的一部分生成輸出以導(dǎo)出項(xiàng)目歷史。

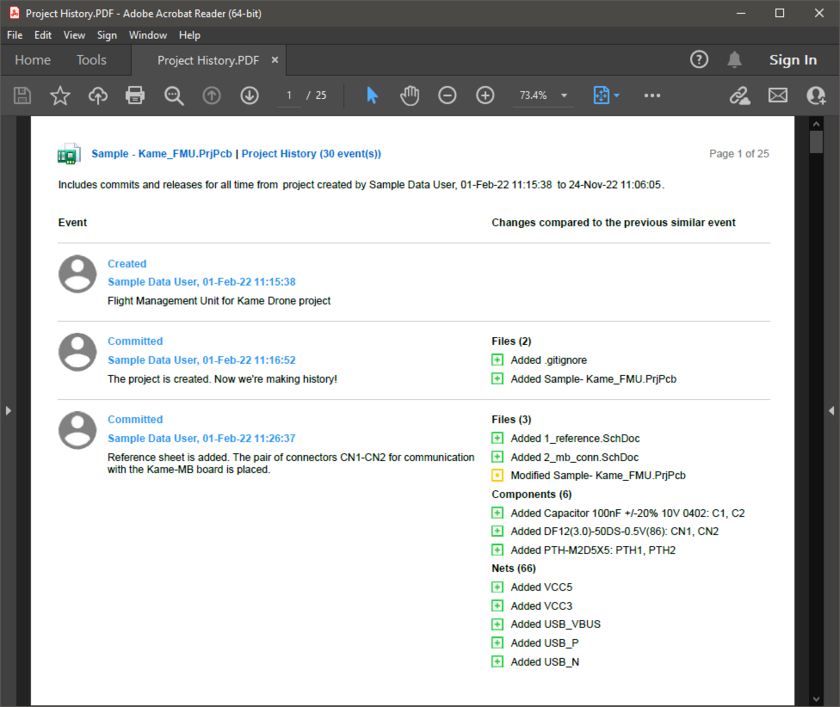

項(xiàng)目歷史報(bào)告示例

請(qǐng)注意,Altium Designer標(biāo)準(zhǔn)訂閱不支持項(xiàng)目歷史報(bào)告導(dǎo)出功能。

如需了解更多信息,請(qǐng)參閱Project History頁(yè)面和Preparing Reports頁(yè)面。

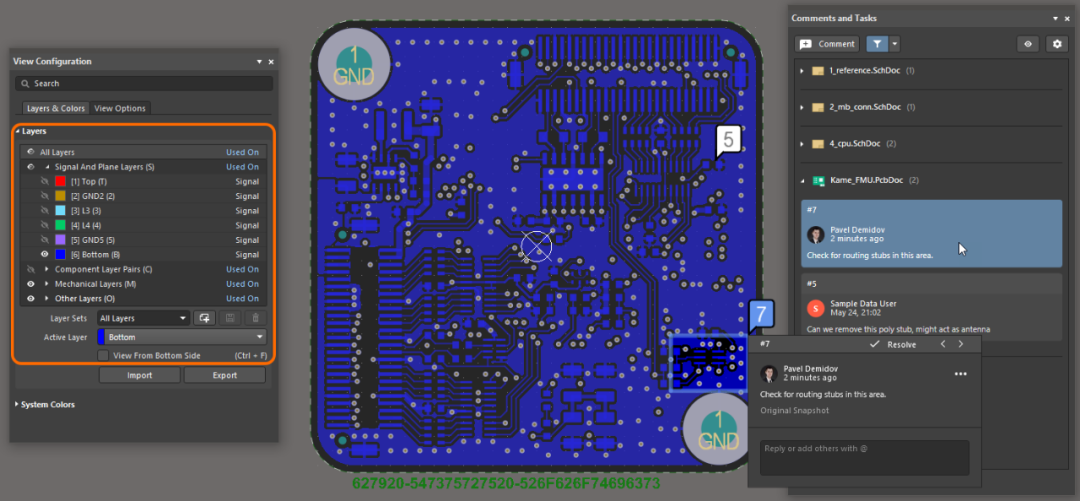

特定層注釋

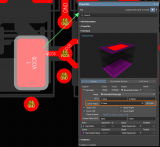

添加了對(duì)PCB上2D特定層注釋的支持。聚焦注釋將自動(dòng)切換至評(píng)審者擁有的相同視圖(可見(jiàn)層、活動(dòng)層、頂層/底層視圖)。

聚焦注釋時(shí)的視圖配置切換示例。此處所示為聚焦注釋前的視圖配置:所有層均已啟用,Top為活動(dòng)層,且電路板從底層顯示。將光標(biāo)懸停在圖像上,以查看聚焦注釋后的電路板(應(yīng)用與添加注釋時(shí)相同的視圖):Bottom為唯一啟用的信號(hào)層,Bottom為活動(dòng)層,且電路板從頂層顯示。

如需了解更多信息,請(qǐng)參閱Document Commenting頁(yè)面。

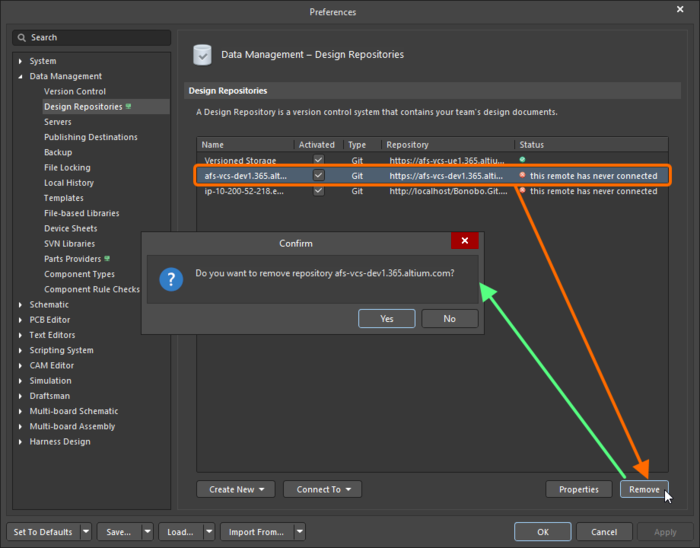

工作區(qū)存儲(chǔ)庫(kù)刪除功能

如果存儲(chǔ)庫(kù)未對(duì)Workspace項(xiàng)目進(jìn)行引用,則將由外部VCS托管的項(xiàng)目遷移至Altium 365 Workspace VCS后,可將Preferences對(duì)話框Data Management - Design Repositories頁(yè)面中顯示的Workspace存儲(chǔ)庫(kù)刪除。

在將項(xiàng)目從外部VCS成功遷移至Workspace VCS后,將自動(dòng)從Workspace中刪除存儲(chǔ)庫(kù)。

說(shuō)明:

僅Workspace管理員擁有刪除存儲(chǔ)庫(kù)的權(quán)限。

如果項(xiàng)目已被軟刪除(移至Trash),則必須將其永久刪除,以確保可刪除引用它的存儲(chǔ)庫(kù)。

無(wú)法刪除Workspace的Versioned Storage存儲(chǔ)庫(kù)。

如需了解更多信息,請(qǐng)參閱Making an Existing Project Available in the Workspace頁(yè)面。

線束設(shè)計(jì)

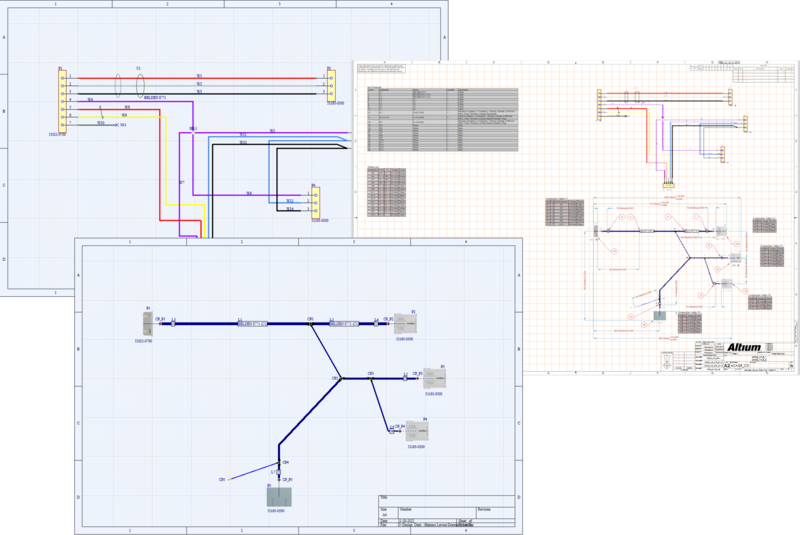

本次發(fā)布首次實(shí)現(xiàn)了Harness Design功能。各類新入行工程師(參與產(chǎn)品設(shè)計(jì)過(guò)程)可使用該新工具,在Altium Designer中工作。其將全面線束設(shè)計(jì)支持引入與PCB和系統(tǒng)設(shè)計(jì)相同的環(huán)境中,從而消除了以前對(duì)第三方軟件的嚴(yán)重依賴。

您可以使用Harness Design工具,創(chuàng)建從引腳間連接到制造文檔的完整線束設(shè)計(jì)。線束設(shè)計(jì)既可作為獨(dú)立項(xiàng)目,亦可作為Multi-board項(xiàng)目的一部分創(chuàng)建。在后一種情況下,Multi-board項(xiàng)目中PCB之間的邏輯連接用于定義線束內(nèi)的連接。

本次發(fā)布引入了一個(gè)與新的多板演示項(xiàng)目(Harness_Demo_MB.PrjMbd)相關(guān)的示例線束設(shè)計(jì)項(xiàng)目(Harness_Demo_Prj.PrjHar),以確保可直接使用線束進(jìn)行試車。

需了解更多信息,請(qǐng)參閱Harness Design頁(yè)面。

此功能目前處于Open Beta階段,且僅在Advanced Settings對(duì)話框中啟用System.HarnessDesignAvailable選項(xiàng)時(shí)可用。請(qǐng)注意,Altium Designer Standard Subscription不支持Harness Design功能。

ActiveBOM增強(qiáng)功能

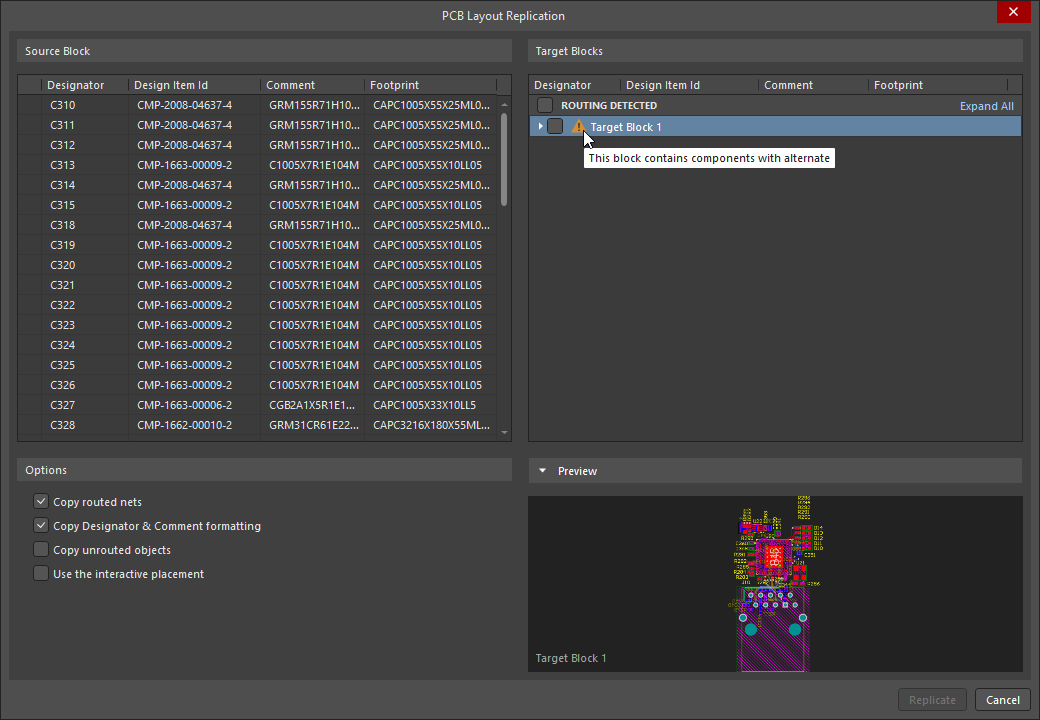

本次發(fā)布引入一些在ActiveBOM中使用替代元件時(shí)的增強(qiáng)功能。

在Add Alternative Item對(duì)話框中保留過(guò)濾器和值

當(dāng)對(duì)相同類型不同元件的對(duì)話框進(jìn)行訪問(wèn)時(shí),可通過(guò)右鍵單擊Workspace元件并選中上下文菜單中的Operations ? Add Alternative Item命令進(jìn)行訪問(wèn)的Add Alternative Item對(duì)話框,將記住所用過(guò)濾器和值。

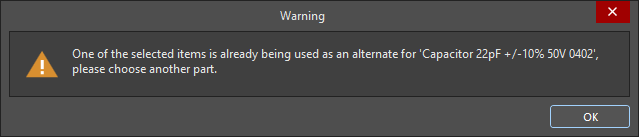

防止使用已用元件替換替代元件

當(dāng)嘗試將替代元件替換為已用作替代元件的元件時(shí),將彈出一個(gè)警告對(duì)話框以發(fā)出提醒。

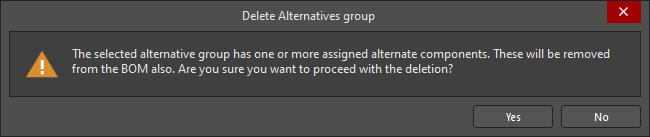

確認(rèn)刪除具有替代元件的替代組

當(dāng)嘗試刪除一組替代元件而該組中的元件已分配替代元件時(shí),將顯示一個(gè)警告對(duì)話框以提醒并要求您確認(rèn)刪除該組。

如需了解更多信息,請(qǐng)參閱Managing Your ActiveBOM Solutions頁(yè)面。

電路仿真改進(jìn)

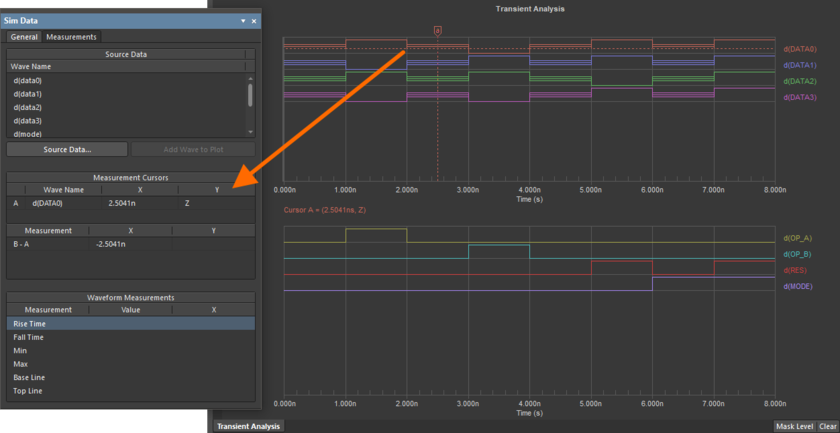

高阻抗?fàn)顟B(tài)

添加了在SimData編輯器中,查看數(shù)字波形高阻抗?fàn)顟B(tài)的功能。

PSpice增強(qiáng)功能

本次發(fā)布中添加了對(duì)以下PSpice基元的支持:

LOGICEXP

Digital delay line

Digital Pullup and Pulldown

DFF

JKFF

DFFDE

JKFFDE

此外,以下PSpice基元的元件已添加到Simulation Generic Components庫(kù)中:

標(biāo)準(zhǔn)門(mén)

三態(tài)門(mén)

數(shù)字激勵(lì)

Altium Designer 23.0版中完全公開(kāi)的功能

以下功能已通過(guò)Open Beta階段,并在本次發(fā)布中過(guò)渡為Public:

自動(dòng)更新設(shè)計(jì)規(guī)則中的位號(hào)- 自22.0版起可用

添加‘新建庫(kù)’對(duì)話框- 自22.5版起可用

自定義焊盤(pán)形狀- 自22.8版起可用

在BOM文檔中添加和編輯注釋- 自22.9版起可用

自定義圓角矩形和新建倒角矩形焊盤(pán)形狀- 自22.11版起可用

審核編輯:湯梓紅

-

pcb

+關(guān)注

關(guān)注

4318文章

23022瀏覽量

396420 -

DFM

+關(guān)注

關(guān)注

8文章

461瀏覽量

28146 -

Altium Designer

+關(guān)注

關(guān)注

47文章

394瀏覽量

44676

原文標(biāo)題:Altium Designer 23.0.1 版本發(fā)布,新功能說(shuō)明

文章出處:【微信號(hào):AltiumChina,微信公眾號(hào):Altium】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

Altium Designer 25.0.2版本的新功能

淺談Xpedition 2409版本的新功能

Xpedition 2409版本新功能說(shuō)明

Altium Designer 24.10.1版本新功能解析

altium designer原理圖生成方法

Altium Designer 24.7.2版本新功能圖解說(shuō)明

Altium Designer 24.3.1版本發(fā)布,新功能說(shuō)明

Altium Designer 24.2.2新功能說(shuō)明

關(guān)于32/64位Altium Designer與Access數(shù)據(jù)庫(kù)兼容的問(wèn)題

Altium Designer 24已發(fā)布 在PCB設(shè)計(jì)和數(shù)據(jù)連接領(lǐng)域?qū)⒂型黄菩赃M(jìn)展

altium designer哪個(gè)版本穩(wěn)定

Altium designer pcb實(shí)用技巧

Altium Designer 24.0.1版本新功能說(shuō)明

Altium Designer功能-使用Section View功能查看剖視圖

Altium Designer 23.0.1版本發(fā)布,新功能說(shuō)明

Altium Designer 23.0.1版本發(fā)布,新功能說(shuō)明

評(píng)論