1 前言

大家好,我是硬件花園! 一名樂于分享的硬件工程師。關注我,了解更多精彩內容!

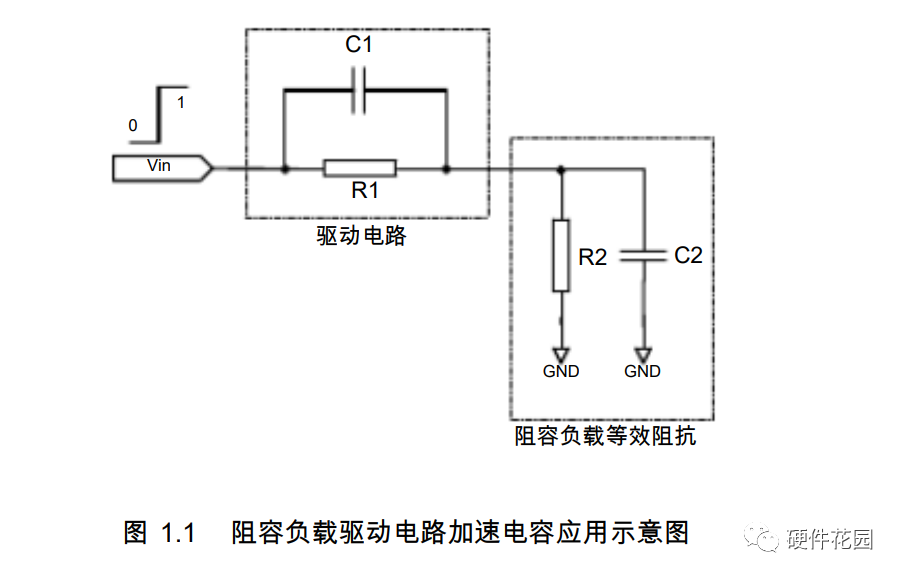

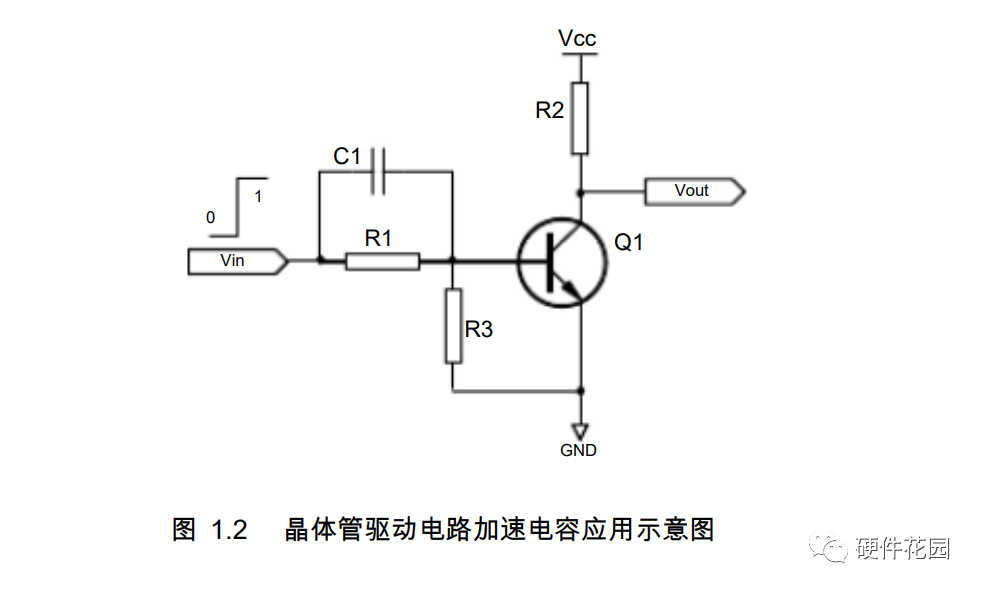

為了加快負載端電壓變化率, 通常會在驅動電路中的電阻兩端并聯一個電容, 這個電容被稱為加速電容。根據負載的不同, 加速電容主要應用于阻容負載驅動電路和晶體管驅動電路兩類場合。

如圖1.1為阻容負載驅動電路的加速應用, R2和C2分別是負載端的等效電阻和等效電容,驅動電路中串入的電阻R1一般起到限制電流或穩定電路等作用,并聯在R1電阻兩端的C1 是加速電容。

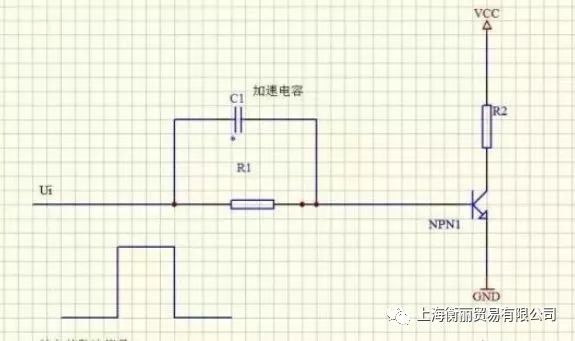

如圖1.2所示為晶體管驅動電路的加速應用,這里以三極管為例,其中R1為基極限流作用,R2為三極管集電極的上拉電阻,R3將輸入端口下拉到地保證在沒有輸入的情況下能夠穩定輸出高電平,同時在三極管截止時給基區過量的電荷提供泄放回路縮短三極管的退飽和時間,C1為加速電容。

2 加速電容原理

不論是阻容負載還是晶體管驅動電路,加速電容根本的加速原因都是利用了電容兩端電壓不能突變的原理,下面將具體分析這兩類驅動電路的加速原理。

2.1 阻容負載驅動電路

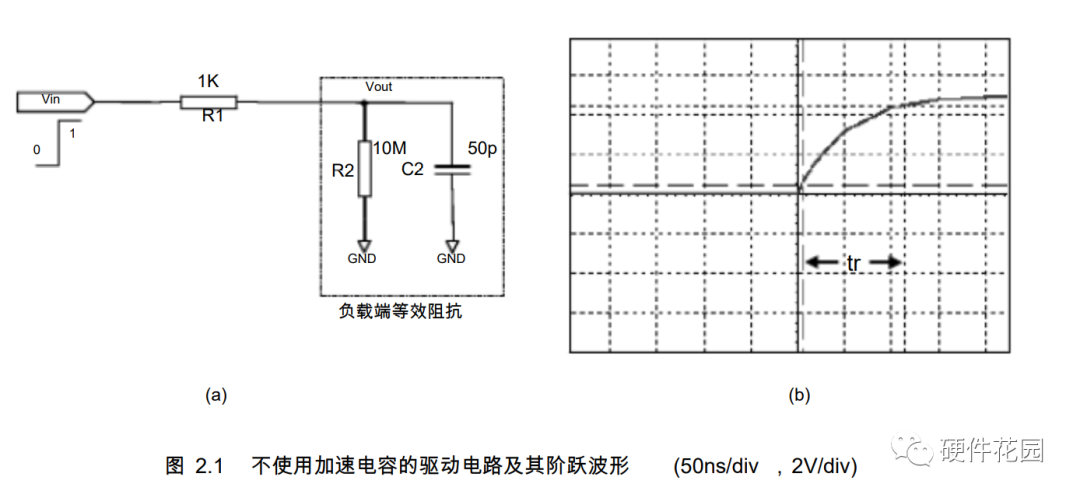

如圖2.1(a)所示為不使用加速電容的驅動電路示意圖,在輸入端加入一個階躍,Vin會通過電阻R1和電阻R2對負載等效電容C2充電,因此Vout電壓不會立刻變化,電壓變化的快慢取決于電容C2的充電時間。

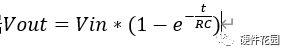

根據Vout的輸出表達式

得到

令Vout=0.9Vin。通過表達式1可以計算出Vout輸出電壓的上升時間tr=115ns。

注:本文所有的上升時間默認為10%~90%上升時間。10%~90%上升時間:階躍響應波形從10%幅度上升到90%幅度所用的時間。

在上述電路的輸入端加入一個5V的階躍,使用Multisim仿真輸出波形如圖2.1(b)所示,輸出電壓沒有緊跟輸入電壓變化而是按指數規律上升,上升所用時間為115ns。

如圖2.2(a)所示為使用加速電容的驅動電路示意圖,電阻R1兩端并聯了一個加速電容C1,當階躍開始時由于C1電容兩端的電壓不能突變將電阻R1短路,所以不存在電阻對電容充電的過程,Vout電壓可以迅速變化。

當t=0時,得到階躍開始時的輸出電壓為:

將C1和C2的值代入表達式3中計算得Vout=0.995Vin,當t=0時Vout已經超過了90%幅度,所以使用加速電容后上升時間tr=0ns。

在圖2.2(a)所示電路的輸入端加入一個5V階躍,使用Multisim仿真輸出波形如圖2.2(b)所示,上升時間為0ns。從上述分析可得,在阻容負載驅動電路的應用中,加速電容利用了電容兩端電壓不能突變的原理,消除了驅動電路中阻容充放電過程,加快了負載端的電壓變化率。

2.2 晶體管驅動電路

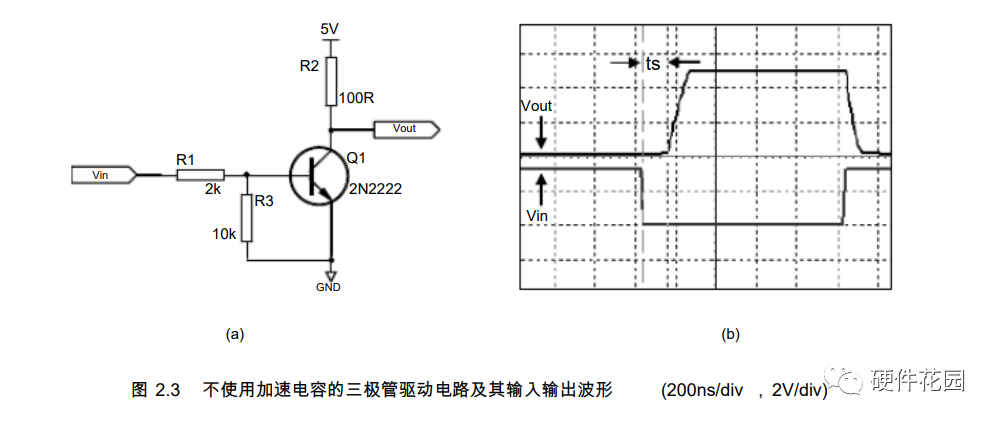

下面以三極管驅動電路為例來分析晶體管驅動電路中的加速電容工作原理。如圖2.3(a)所示為不使用加速電容的三極管驅動電路。其中三極管工作在截止和飽和區,當輸入從高電平變為低電平時,三極管從飽和狀態進入截止狀態,但是由于三極管飽和時會在基區存入過量的電荷,這些電荷只能通過電阻R1和R3緩慢地泄放。基極過量電荷完全泄放所需的時間被稱為三極管的存儲時間ts,在存儲時間階段集電極電壓是不會變化的,所以輸出電壓會延遲ts時間才開始變化。

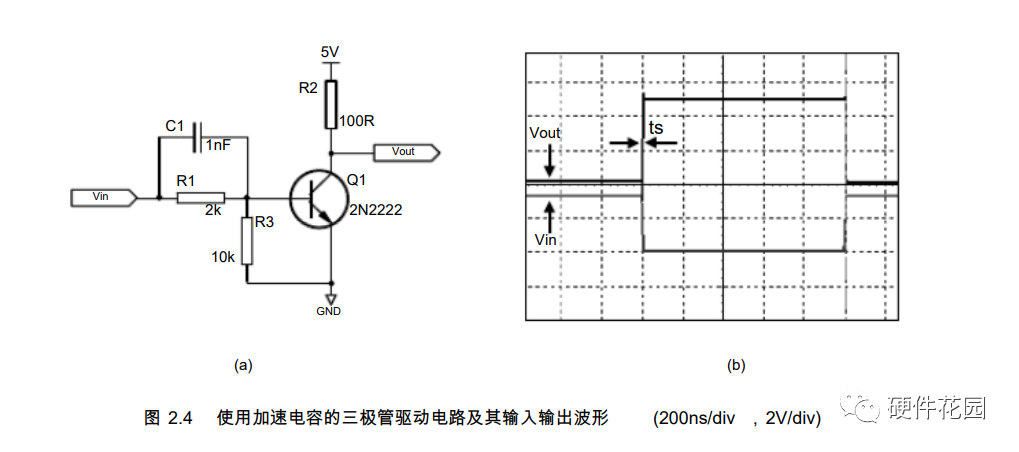

使用Multisim仿真上述電路,輸入頻率為500KHz的3.3V方波,方波邊沿變化速率設置為10ns,仿真結果如圖2.3(b)所示,輸出波形滯后了輸入波形114ns才開始變化。如圖2.4(a)所示為采用加速電容的三極管驅動電路。限流電阻R1兩端并聯了一個1nF的加速電容C1,輸入高電平電容C1充電存儲電荷,當輸入從高電平變為低電平時,由于電容兩端電壓不能突變,電容C1將電阻R1短路,基區過量的電荷和電容C1的存儲電荷迅速中和減少了存儲時間,縮短了輸入輸出的時間延遲。

使用Multisim仿真圖2.4(a)電路,輸入頻率為500KHz的3.3V方波,方波邊沿變化速率設置為10ns,結果如圖2.4(b)所示,輸出電壓緊跟輸入電壓變化幾乎沒有延遲。從上述的分析可得,三極管驅動電路在飽和時給加速電容充電,當三極管截止時利用電容兩端電壓不能突變將限流電阻短路,基區過量的電荷迅速釋放,減少了存儲時間,實現了加速的作用。

審核編輯:湯梓紅

-

電容

+關注

關注

99文章

5995瀏覽量

149999 -

晶體管

+關注

關注

77文章

9634瀏覽量

137847 -

Multisim

+關注

關注

132文章

755瀏覽量

115075 -

驅動電路

+關注

關注

152文章

1520瀏覽量

108370 -

加速電容

+關注

關注

0文章

15瀏覽量

2127

原文標題:加速電容在電路中的妙用

文章出處:【微信號:硬件技術后花園,微信公眾號:硬件技術后花園】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

電容在電源電路中的作用 電容在交流電路中的使用

晶振過驅的影響及其預防措施:電阻與電容在晶振電路中的應用

無功補償電容容量下降如何優化

加速電容在電路中的妙用

加速電容在電路中的妙用

評論