在實際電路中,寄生電感最主要的來源是PCB上的走線以及過孔,PCB板上的走線長度越長,過孔的深度越大,寄生電感就越大。

輸入端走線優化

要減少通電瞬間,寄生電感對輸入電容上電壓的影響,就需要降低電路中寄生電感的感值,最有效的方法就是減少從電路輸入端到輸入電容的走線長度,當從輸入端到輸入電容之間必須使用過孔時,我們可以選擇厚度較薄的PCB板,減少過孔的深度,同時多打過孔,使寄生電感并聯從而降低輸入端到電容之間的電感值。

另外在對電路通電前,要預先檢查輸入電容上的電壓是否有異常的高壓,如果發現電壓過高則需要繼續通過上面的方法進行優化。

芯片端的電路走線優化

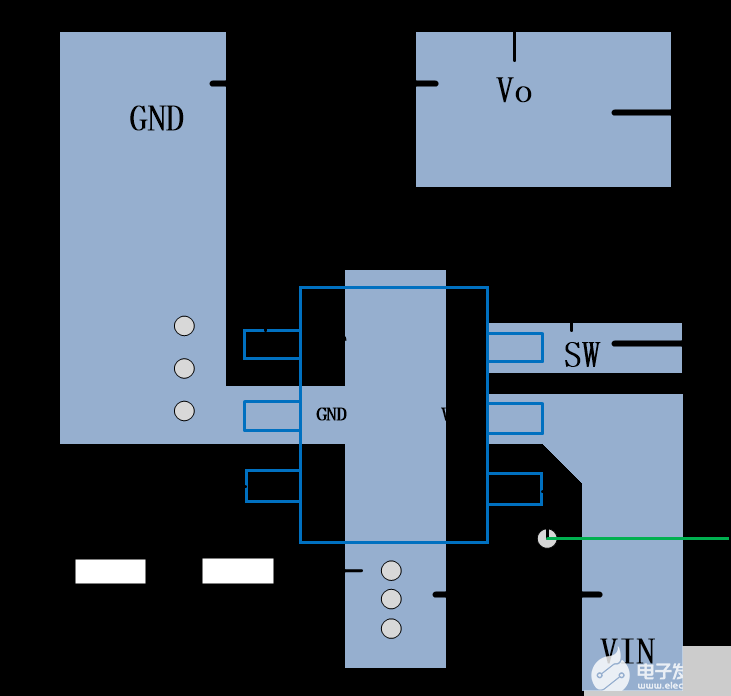

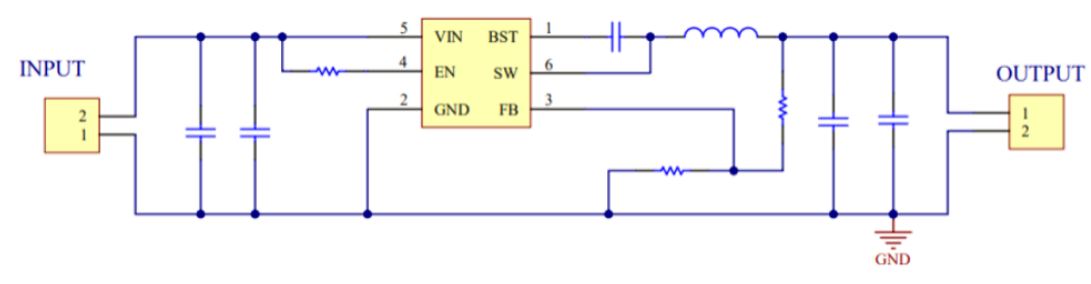

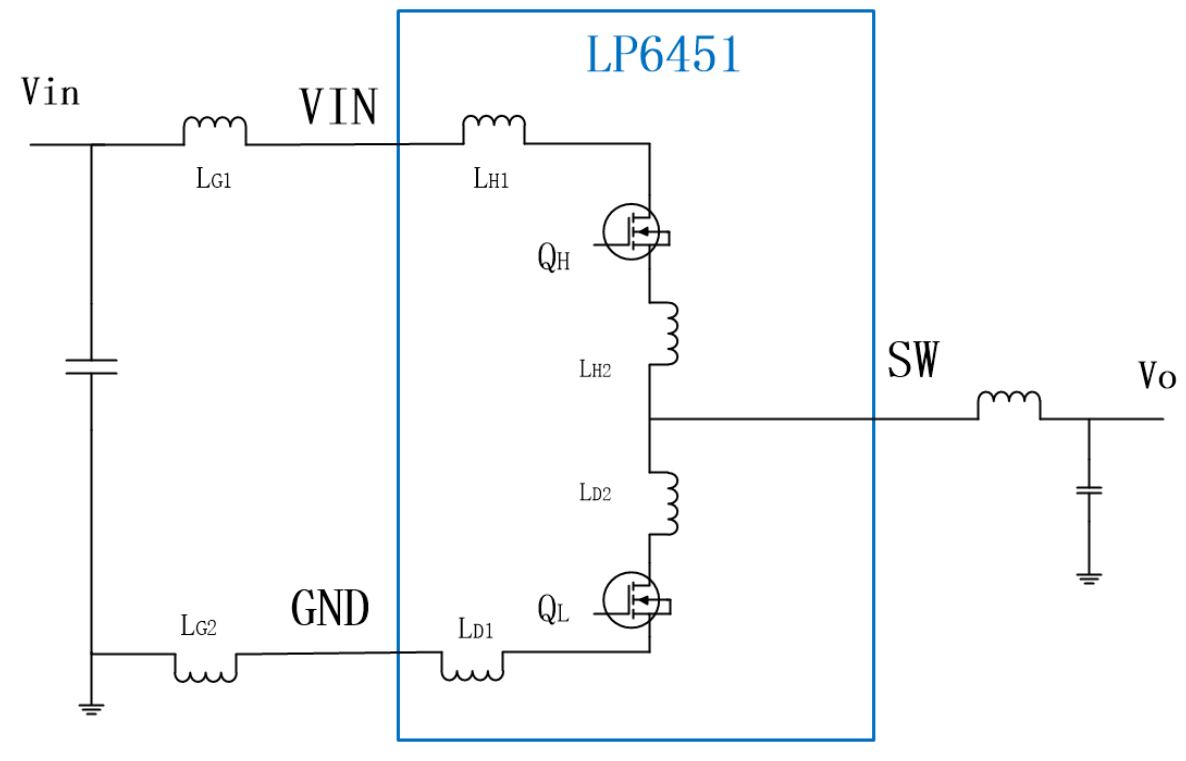

從之前LP6451的分析中可以看到,寄生電感LG1和LG2產生的感應電壓對Buck控制芯片的影響最大,因此在實際電路中,我們希望LG1和LG2越小越好,這也就是我們常說的,輸入電容要盡可能的靠近控制芯片,并且從輸入電容到芯片相應引腳之間的走線最好在同一層,而且越短越好的原因。圖1是LP6451的建議走線圖,輸入電容CIN需要盡可能的靠近芯片的VIN和GND引腳。

圖1:建議Layout 打線圖

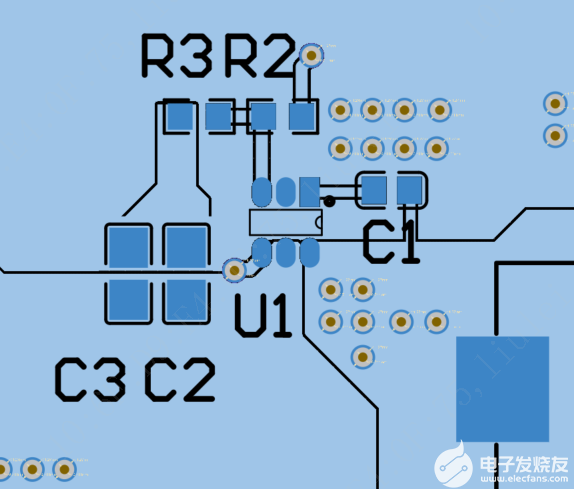

圖2:LP6451 Layout 布線圖

而圖2為LP6451 Demo Board的實際Layout的走線圖,其中輸入電容C2和C3(即圖1中的CIN)盡量靠近控制芯片LP6451,輸入電容的正極和地線也都采用鋪銅的方式在TOP層分別與芯片的VIN和GND引腳連接,這樣能盡可以的減少寄生電感,從而降低寄生電感對電路的影響。

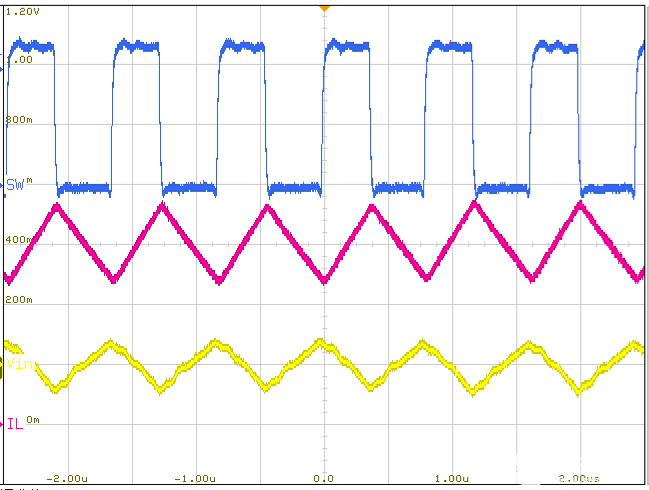

圖3:LP6451 工作波形

圖3為LP6451 Demo Board的實際工作波形,輸入電壓為12VDC,輸出負載為5V/3A,采用優化的Layout走線圖后,Demo Board在滿載工作時測試LP6451的SW引腳,從波形上看沒有任何毛刺,電路工作狀態十分良好。

總結

這里我們介紹了開關電源電路中,寄生電感的來源,與哪些因素有關,寄生電感對電路的影響以及如何采用優化Layout的方法來降低電路中寄生電感。因為寄生電感并不(找元器件現貨上唯樣商城)是工程師們在開發電源時專門設計的,所以很多時候寄生電感造成的不良影響往往就被忽略了,希望通過這三期文章介紹,能讓大家對寄生電感有更多更深入的認識,在設計電源的初期就能引起重視,做到防患于未然。

審核編輯黃昊宇

-

芯片

+關注

關注

454文章

50442瀏覽量

421920 -

電感

+關注

關注

54文章

6113瀏覽量

102170

發布評論請先 登錄

相關推薦

如何通過等效串聯電阻(ESR)和等效串聯電感(ESL)來優化熱回路布局設計

合金電阻的寄生電感及其影響

深入解析晶振時鐘信號干擾源:寄生電容、雜散電容與分布電容

用TPS8802和TPS8804優化光電感煙探測器的信噪比

系統寄生參數對SiC器件開關的影響分析

碳化硅模塊(SiC模塊/MODULE)大電流下的驅動器研究

什么是寄生電感?如何計算過孔的寄生電感?

寄生電感到底是什么?如何計算過孔的寄生電感?

PCB寄生電容的影響 PCB寄生電容計算 PCB寄生電容怎么消除

寄生電感的優化

寄生電感的優化

評論