大數(shù)據(jù)時代,每個人的搜索框在某種程度上都代表著這個人的所思所想。如果將時間放長,樣本量放大,那么一份年度搜索關(guān)鍵詞就會呈現(xiàn)出了這個世界上絕大部分人是如何走過這一年的

搜索產(chǎn)品型號與關(guān)鍵詞

搜索

今天,咱們也將分享這樣一份搜索趨勢數(shù)據(jù),看看各位小伙伴在ADI全平臺上搜索的熱門關(guān)鍵詞,都在關(guān)心什么樣的產(chǎn)品,學(xué)習(xí)什么樣的資料,咨詢什么樣的問題?

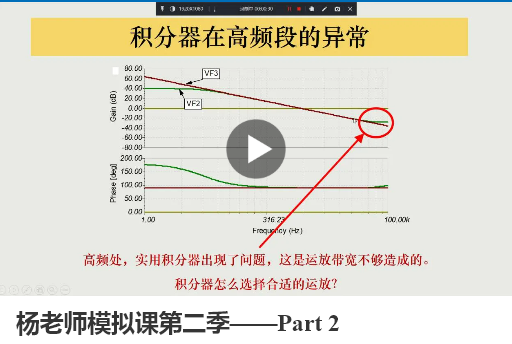

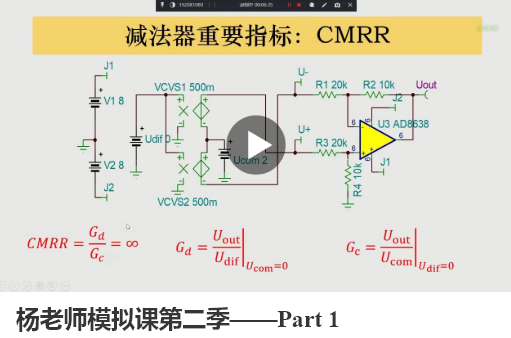

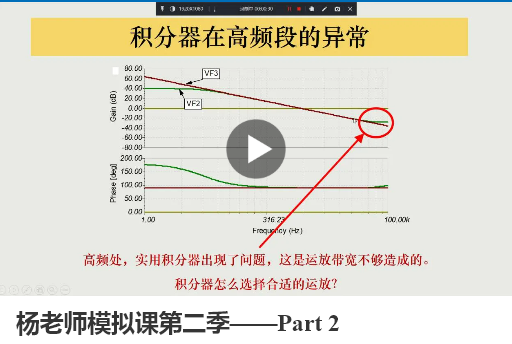

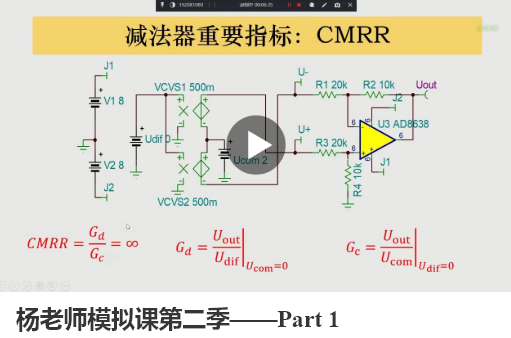

關(guān)鍵詞:楊老師模擬課

“楊老師模擬課”是西安交通大學(xué)電氣工程學(xué)院教授、博士生導(dǎo)師、工學(xué)博士楊建國在多年的執(zhí)教與科研時間中,積累的問題與詳細(xì)解答,并從中精選了最具代表性的10個問題,做出了10堂視頻課,結(jié)合PPT,細(xì)致逐步講解。

“楊老師模擬課”是西安交通大學(xué)電氣工程學(xué)院教授、博士生導(dǎo)師、工學(xué)博士楊建國在多年的執(zhí)教與科研時間中,積累的問題與詳細(xì)解答,并從中精選了最具代表性的10個問題,做出了10堂視頻課,結(jié)合PPT,細(xì)致逐步講解。

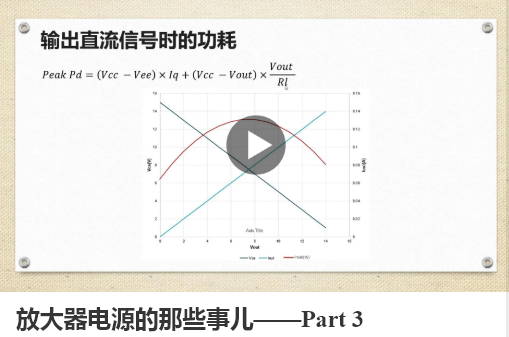

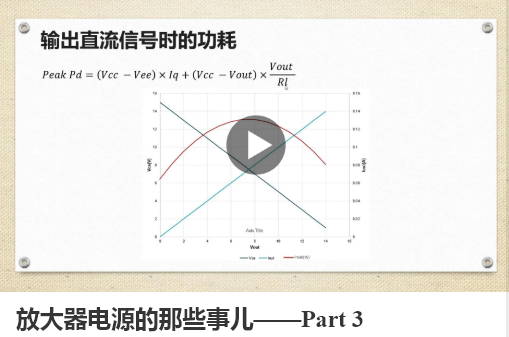

關(guān)鍵詞:放大器電源的那些事兒

放大器是一種有源器件,需要供電才能工作,電源的不同選擇和設(shè)置也會對放大器參數(shù)性能產(chǎn)生影響,因此,不管您是已入職場的設(shè)計人員,還是在正在學(xué)習(xí)電路設(shè)計的學(xué)生,都應(yīng)該對放大器電源有更多的了解。《放大器電源的那些事兒》由ADI放大器應(yīng)用工程師錄制,合計22小節(jié)內(nèi)容,主要介紹放大器的電源應(yīng)用的相關(guān)注意事項。

放大器是一種有源器件,需要供電才能工作,電源的不同選擇和設(shè)置也會對放大器參數(shù)性能產(chǎn)生影響,因此,不管您是已入職場的設(shè)計人員,還是在正在學(xué)習(xí)電路設(shè)計的學(xué)生,都應(yīng)該對放大器電源有更多的了解。《放大器電源的那些事兒》由ADI放大器應(yīng)用工程師錄制,合計22小節(jié)內(nèi)容,主要介紹放大器的電源應(yīng)用的相關(guān)注意事項。

關(guān)鍵詞:放大器設(shè)計問答

?

ADI的工程師們在與客戶的長期溝通過程中,收到并解答了大量關(guān)于放大器的使用問題,很多問題都頗具代表性,為了讓更多工程師能理解和使用好放大器這一器件,ADI特別梳理了相關(guān)內(nèi)容,挑選出75個典型的常見問題并整合出一本《放大器設(shè)計問答》。

關(guān)鍵詞:PCB設(shè)計秘籍

?

本書以ADI公司官方網(wǎng)站、ADI中文技術(shù)論壇、亞德諾半導(dǎo)體官方微信公眾號的PCB設(shè)計內(nèi)容資料為基礎(chǔ)資料來源,按PCB布局布線、散熱技巧、接地指導(dǎo)、抗擾度等角度進(jìn)行分類整理,針對在各種器件、應(yīng)用環(huán)境下,提供了一些實(shí)用的PCB設(shè)計指導(dǎo)以及常見問題解答。

公眾號熱門文章鏈接:

混合信號PCB布局設(shè)計的基本準(zhǔn)則

電源PCB上電感應(yīng)該如何安放?

使用高速轉(zhuǎn)換器時應(yīng)遵循哪些重要的PCB布線規(guī)則?

......

?

?

關(guān)鍵詞:電流測量

?

ADI公司的電流測量信號鏈解決方案包括各種用于在大多數(shù)環(huán)境下精確測量電流的精確、可靠解決方案。從監(jiān)控電機(jī)、DC/DC轉(zhuǎn)換器和螺線管中的相電流到ATE環(huán)境中的漏電流,ADI的信號鏈提供經(jīng)過驗證的性能,并已針對特定的總線電壓范圍、電流范圍和傳感器類型進(jìn)行優(yōu)化。《電流測量信號鏈解決方案》內(nèi)含信號鏈、參考設(shè)計以及深度技術(shù)文章,旨在幫您了解如何應(yīng)用ADI的行業(yè)領(lǐng)先技術(shù)解決電流測量的問題。

?

?

關(guān)鍵詞:ADC/DAC

?

ADC可在各類應(yīng)用中實(shí)現(xiàn)精確可靠的轉(zhuǎn)換性能,ADI公司擁有業(yè)界最齊全的數(shù)據(jù)轉(zhuǎn)換器產(chǎn)品系列,DAC涵蓋8位至24位,面向工業(yè)自動化、可編程邏輯控制器、光收發(fā)器、數(shù)據(jù)采集等各種應(yīng)用,能夠提供精確可靠、無與倫比的轉(zhuǎn)換性能和價值;ADI推出電子書《ADC和DAC的基本架構(gòu)》,旨在梳理ADC和DAC使用中相關(guān)的基礎(chǔ)要點(diǎn)以及構(gòu)架示例。

相關(guān)鏈接:模數(shù)轉(zhuǎn)換器相關(guān)技術(shù)資料

?

?

關(guān)鍵詞:電源管理

?

ADI高性能電源管理解決方案通過先進(jìn)的設(shè)計和封裝技術(shù)滿足嚴(yán)格的電源要求,包括出色的功率密度、超低噪聲技術(shù)和出色的可靠性。ADI低復(fù)雜度的電源管理解決方案得到業(yè)界最全面的、從頭至尾的電源設(shè)計工具套件以及高度可配置的電源互連解決方案的支持,可幫助我們的客戶縮短產(chǎn)品上市時間,同時提供出色的性能。

相關(guān)鏈接:電源管理相關(guān)技術(shù)資料

?

關(guān)鍵詞:精密信號鏈

精密技術(shù)信號鏈允許在各種設(shè)計權(quán)衡之間輕松變換,以為應(yīng)用創(chuàng)建優(yōu)質(zhì)的終端解決方案。利用ADI公司完整的精密技術(shù)信號鏈加速技術(shù)選擇和實(shí)施,這些信號鏈匯集了50多年的洞察力和專業(yè)知識。結(jié)合適當(dāng)?shù)墓ぞ摺iT開發(fā)的知識庫和可定制的解決方案,ADI的精密技術(shù)信號鏈能夠輕松采用。相關(guān)鏈接:

精密技術(shù)信號鏈允許在各種設(shè)計權(quán)衡之間輕松變換,以為應(yīng)用創(chuàng)建優(yōu)質(zhì)的終端解決方案。利用ADI公司完整的精密技術(shù)信號鏈加速技術(shù)選擇和實(shí)施,這些信號鏈匯集了50多年的洞察力和專業(yè)知識。結(jié)合適當(dāng)?shù)墓ぞ摺iT開發(fā)的知識庫和可定制的解決方案,ADI的精密技術(shù)信號鏈能夠輕松采用。相關(guān)鏈接:

精密信號鏈平臺相關(guān)解決方案

?

關(guān)鍵詞:電機(jī)驅(qū)動與運(yùn)動控制

?

運(yùn)動控制是智能制造的核心構(gòu)建模塊,可實(shí)現(xiàn)高度靈活的高效制造。智能運(yùn)動控制融合了精確反饋、先進(jìn)感知、高性能控制和無縫連接技術(shù),可提供確定性運(yùn)動解決方案。ADI專注于為電機(jī)驅(qū)動與運(yùn)動控制提供新技術(shù)和解決方案,幫助客戶實(shí)現(xiàn)下一代先進(jìn)和可持續(xù)的電機(jī)驅(qū)動與運(yùn)動控制。

相關(guān)鏈接:

電機(jī)驅(qū)動與運(yùn)動控制相關(guān)解決方案

各位小伙伴,這些關(guān)鍵詞你是否也搜索過呢?

快來回顧一下,分享你在今年搜索最多的關(guān)鍵詞!以及它們是否成為了你的助力,為你的設(shè)計再添一份創(chuàng)新呢?

各位小伙伴,這些關(guān)鍵詞你是否也搜索過呢?

快來回顧一下,分享你在今年搜索最多的關(guān)鍵詞!以及它們是否成為了你的助力,為你的設(shè)計再添一份創(chuàng)新呢?

原文標(biāo)題:ADI年度關(guān)鍵詞曝光,這些你肯定搜索過!

文章出處:【微信公眾號:亞德諾半導(dǎo)體】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

聲明:本文內(nèi)容及配圖由入駐作者撰寫或者入駐合作網(wǎng)站授權(quán)轉(zhuǎn)載。文章觀點(diǎn)僅代表作者本人,不代表電子發(fā)燒友網(wǎng)立場。文章及其配圖僅供工程師學(xué)習(xí)之用,如有內(nèi)容侵權(quán)或者其他違規(guī)問題,請聯(lián)系本站處理。

舉報投訴

原文標(biāo)題:ADI年度關(guān)鍵詞曝光,這些你肯定搜索過!

文章出處:【微信號:analog_devices,微信公眾號:analog_devices】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

相關(guān)推薦

RISC-V(Reduced Instruction Set Computing – V)無疑正是當(dāng)下芯片產(chǎn)業(yè)的熱門關(guān)鍵詞!使用最開放開源協(xié)議之一的BSD,只用十年就達(dá)到出貨量100億顆(ARM 指令集芯片達(dá)到相同出貨量用了近 30 年)的RISC-V,大有與x86和Arm兩大指令集三分天下的潛力。

![的頭像]() 發(fā)表于

發(fā)表于 09-19 13:01

?467次閱讀

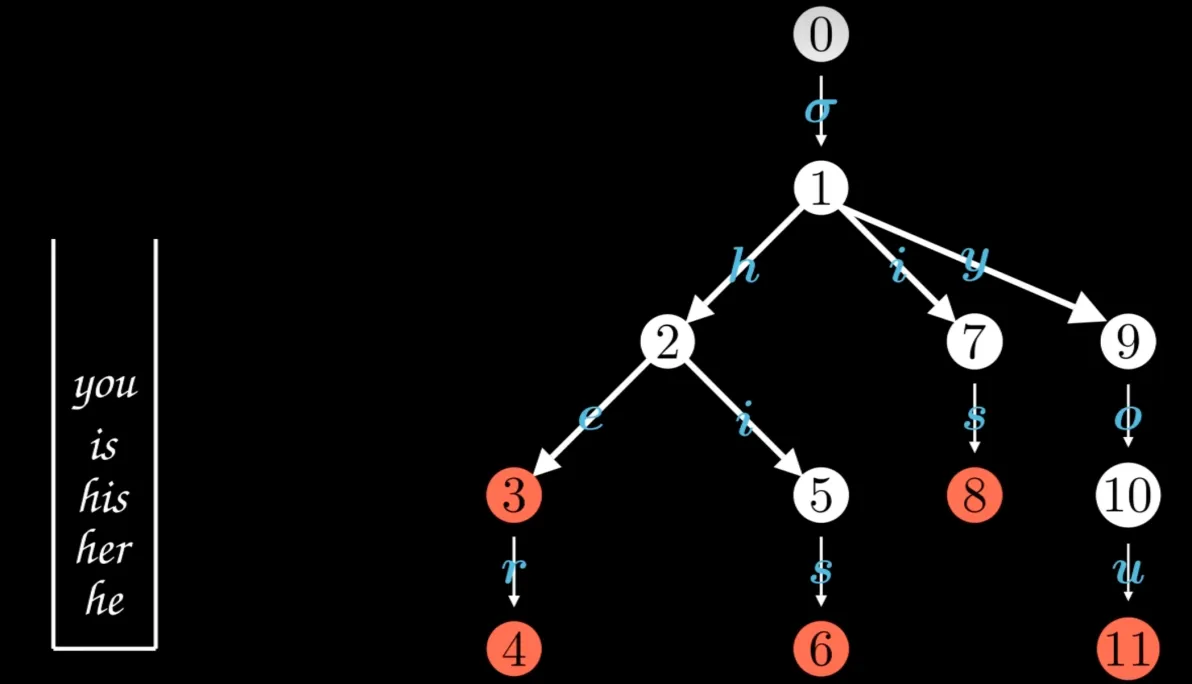

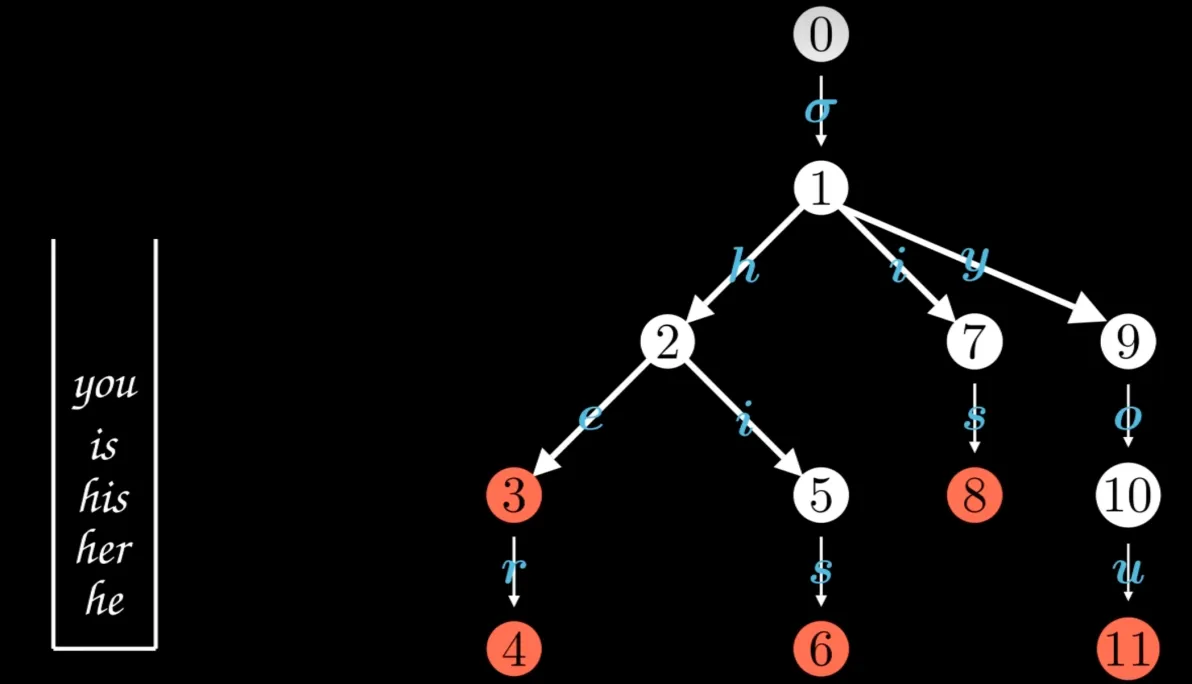

引言 目前,大多數(shù)自由文本搜索技術(shù)采用類似于Lucene的策略,通過解析搜索文本為各個組成部分來定位關(guān)鍵詞。這種方法在處理少量關(guān)鍵詞時表現(xiàn)良好。但當(dāng)

![的頭像]() 發(fā)表于

發(fā)表于 08-26 15:55

?815次閱讀

7月23日,由中國通信標(biāo)準(zhǔn)化協(xié)會主辦,中國信息通信研究院(簡稱“中國信通院”)承辦的“2024可信云大會”在京召開。大會上,中國信通院正式發(fā)布“2024云計算十大關(guān)鍵詞”,中國信通院云計算與大數(shù)

![的頭像]() 發(fā)表于

發(fā)表于 08-02 08:28

?554次閱讀

植保機(jī)在田野上空“起舞”,無人機(jī)在夜空中排列組合成驚艷的“巨龍”圖案。你點(diǎn)了一份外賣,而送餐的“小哥”卻是一架無人機(jī)。這些都是低空經(jīng)濟(jì)的冰山一角。作為近期的全網(wǎng)熱詞,在全國兩會期間也被多次提及

![的頭像]() 發(fā)表于

發(fā)表于 05-01 08:23

?286次閱讀

近日,工信部發(fā)布了《關(guān)于開展2024年度5G輕量化(RedCap)貫通行動的通知》,從標(biāo)準(zhǔn)、網(wǎng)絡(luò)、芯片模組、終端、應(yīng)用、安全、保障7大方面采取具體措施,并給出明確目標(biāo),在政策層面對5GRedCap

![的頭像]() 發(fā)表于

發(fā)表于 04-23 08:04

?396次閱讀

當(dāng)前,微軟已邀請部分Canary頻道Edge使用者參與試用,并在Edge瀏覽器中打開PDF后,右上角將出現(xiàn)新品圖標(biāo)(A之上加放大鏡),用以自動分析及歸納文檔內(nèi)容的關(guān)鍵詞。

![的頭像]() 發(fā)表于

發(fā)表于 03-28 10:05

?451次閱讀

據(jù)稱,搜索廣告能使自然結(jié)果的展示次數(shù)翻倍,收益最大的便是小型開發(fā)團(tuán)隊。他們發(fā)現(xiàn),搜索結(jié)果中的推廣應(yīng)用轉(zhuǎn)化率高達(dá)60%,主要?dú)w因于精準(zhǔn)定位的關(guān)鍵詞和用戶需求分析。

![的頭像]() 發(fā)表于

發(fā)表于 02-23 14:00

?590次閱讀

的一筆共同奏響中國基礎(chǔ)軟件的光輝歲月作為OpenHarmony生態(tài)的領(lǐng)軍企業(yè)深開鴻通過三個關(guān)鍵詞帶你讀懂《2023OpenHarmony年度運(yùn)營報告》01繁榮202

![的頭像]() 發(fā)表于

發(fā)表于 02-02 17:00

?531次閱讀

谷歌搜索引擎是最受歡迎和廣泛使用的搜索引擎之一,為了使你的網(wǎng)站在谷歌上更好地排名并提高曝光度,你可以采取一些谷歌

![的頭像]() 發(fā)表于

發(fā)表于 01-25 10:29

?837次閱讀

總結(jié)為以下四個關(guān)鍵詞。 聚焦 —? 曙光算力服務(wù)緊跟市場趨勢,積極參與信通院新一代算力網(wǎng)技術(shù)創(chuàng)新聯(lián)盟、首批可信算力云服務(wù)-智能平臺和“算力星圖”計劃。通過深度參與行業(yè)標(biāo)準(zhǔn)和技術(shù)創(chuàng)新,曙光智算成功通過首批“可信算力服務(wù)-智

![的頭像]() 發(fā)表于

發(fā)表于 01-04 10:34

?573次閱讀

原文標(biāo)題:測測這10個AI關(guān)鍵詞你清楚幾個?第4個今年最火 文章出處:【微信公眾號:微軟科技】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

![的頭像]() 發(fā)表于

發(fā)表于 12-21 08:15

?526次閱讀

自己平時一直在寫的狀態(tài)機(jī)格式,同事昨天說我寫的是一段式的最多算是偽二段式的,說的看了不少文章我也有點(diǎn)疑惑了,所給大家貼出來一起看看,我這邊寫法和野火的一直這次就貼出野火FPGA的code,供大家參考對比。

module complex_fsm

(

input wire sys_clk , //系統(tǒng)時鐘 50MHz

input wire sys_rst_n , //全局復(fù)位

input wire pi_money_one , //投幣 1 元

input wire pi_money_half , //投幣 0.5 元

output reg po_money , //po_money 為 1 時表示找零

//po_money 為 0 時表示不找零

output reg po_cola //po_cola 為 1 時出可樂

//po_cola 為 0 時不出可樂

);

//********************************************************************//

//****************** Parameter and Internal Signal *******************//

//********************************************************************//

//parameter define

//只有五種狀態(tài),使用獨(dú)熱碼

parameter IDLE = 5\'b00001;

parameter HALF = 5\'b00010;

parameter ONE = 5\'b00100;

parameter ONE_HALF = 5\'b01000;

parameter TWO = 5\'b10000;

//reg define

reg [4:0] state;

//wire define

wire [1:0] pi_money;

//********************************************************************//

//***************************** Main Code ****************************//

//********************************************************************//

//pi_money:為了減少變量的個數(shù),我們用位拼接把輸入的兩個 1bit 信號拼接成 1 個 2bit 信號

//投幣方式可以為:不投幣(00)、投 0.5 元(01)、投 1 元(10),每次只投一個幣

assign pi_money = {pi_money_one, pi_money_half};

//第一段狀態(tài)機(jī),描述當(dāng)前狀態(tài) state 如何根據(jù)輸入跳轉(zhuǎn)到下一狀態(tài)

always@(posedge sys_clk or negedge sys_rst_n)

if(sys_rst_n == 1\'b0)

state <= IDLE; //任何情況下只要按復(fù)位就回到初始狀態(tài)

else case(state)

IDLE : if(pi_money == 2\'b01) //判斷一種輸入情況

state <= HALF;

else if(pi_money == 2\'b10)//判斷另一種輸入情況

state <= ONE;

else

state <= IDLE;

HALF : if(pi_money == 2\'b01)

state <= ONE;

else if(pi_money == 2\'b10)

state <= ONE_HALF;

else

state <= HALF;

ONE : if(pi_money == 2\'b01)

state <= ONE_HALF;

else if(pi_money == 2\'b10)

state <= TWO;

else

state <= ONE;

ONE_HALF: if(pi_money == 2\'b01)

state <= TWO;

else if(pi_money == 2\'b10)

state <= IDLE;

else

state <= ONE_HALF;

TWO : if((pi_money == 2\'b01) || (pi_money == 2\'b10))

state <= IDLE;

else

state <= TWO;

//如果狀態(tài)機(jī)跳轉(zhuǎn)到編碼的狀態(tài)之外也回到初始狀態(tài)

default : state <= IDLE;

endcase

//第二段狀態(tài)機(jī),描述當(dāng)前狀態(tài) state 和輸入 pi_money 如何影響 po_cola 輸出

always@(posedge sys_clk or negedge sys_rst_n)

if(sys_rst_n == 1\'b0)

po_cola <= 1\'b0;

else if((state == TWO && pi_money == 2\'b01) || (state == TWO &&pi_money == 2\'b10) || (state == ONE_HALF && pi_money == 2\'b10))

po_cola <= 1\'b1;

else

po_cola <= 1\'b0;

//第二段狀態(tài)機(jī),描述當(dāng)前狀態(tài) state 和輸入 pi_money 如何影響 po_money 輸出

always@(posedge sys_clk or negedge sys_rst_n)

if(sys_rst_n == 1\'b0)

po_money <= 1\'b0;

else if((state == TWO) && (pi_money == 2\'b10))

po_money <= 1\'b1;

else

po_money <= 1\'b0;

endmodule

發(fā)表于 12-16 09:38

之前的因為一些問題發(fā)的code有點(diǎn)問題,這次把更新之后code發(fā)了出來,雖然也不是很完善但是初步還是可以用的;

對應(yīng)的code如下:

`timescale 1ns / 1ps

modulecreat_PWM

(

inputwireclk,//系統(tǒng)時鐘為100MHz

inputwirerst,//系統(tǒng)復(fù)位

inputwirekey_flag1,//占空比上調(diào)

inputwirekey_flag2,//占空比下調(diào)

inputwirekey_flag3,//頻率上調(diào)

inputwirekey_flag4,//頻率下調(diào)

output regPWM

);

//PWM波形頻率選擇

reg [1:0] Frequency_seting;

always @(posedge clk or negedge rst)

if( rst == 1\'b0 )

Frequency_seting <= 2\'b00;

else if( (Frequency_seting == 2\'b11) && (key_flag3==1\'b1) )

Frequency_seting <= 2\'b00;

else if( (Frequency_seting == 2\'b00) && (key_flag4==1\'b1) )

Frequency_seting <= 2\'b11;

else if( key_flag3==1\'b1 )

Frequency_seting <= Frequency_seting + 1\'b1;

else if( key_flag4==1\'b1 )

Frequency_seting <= Frequency_seting - 1\'b1;

else

Frequency_seting <= Frequency_seting;

//PWM波形的頻率設(shè)定

reg [23:0] Frequency_CNT_MAX;

always @(posedge clk or negedge rst)

if( rst == 1\'b0 )

Frequency_CNT_MAX <= 24\'d9_999;

else case( Frequency_seting )

2\'b00 : Frequency_CNT_MAX <= 24\'d9_999;

2\'b01 : Frequency_CNT_MAX <= 24\'d99_999;

2\'b10 : Frequency_CNT_MAX <= 24\'d999_999;

2\'b11 : Frequency_CNT_MAX <= 24\'d9_999_999;

default : Frequency_CNT_MAX <= 24\'d9_999;

endcase

//PWM頻率生成計數(shù)器模塊

reg [23:0] counter;

always @(posedge clk or negedge rst)

if( rst == 1\'b0 )

counter <= 0;

else if( counter == Frequency_CNT_MAX)

counter <= 0;

else

counter <= counter + 1\'b1;

//占空比調(diào)節(jié)模塊,步進(jìn)為10%

reg [23:0] duty_counter;

always @(posedge clk or negedge rst)

if( rst == 1\'b0 )

duty_counter <= Frequency_CNT_MAX/2;

else if( key_flag1 == 1\'b1 )

duty_counter <= duty_counter + (Frequency_CNT_MAX/10);

else if( key_flag2 == 1\'b1 )

duty_counter <= duty_counter - (Frequency_CNT_MAX/10);

else

duty_counter <= duty_counter;

//生成PWM

always @(posedge clk or negedge rst)

if( rst == 1\'b0 )

PWM <= 1\'b0;

else if( duty_counter <= counter )

PWM <= 1\'b1;

else

PWM <= 1\'b0;

endmodule

對應(yīng)的測試用的testbench如下:

`timescale 1ns/1ns

module tb_creat_PWM();

//****************** Parameter and Internal Signal *******************//

//wire define

wirePWM;

//reg define

reg clk;

reg rst;

reg key_flag1;

reg key_flag2;

reg key_flag3;

reg key_flag4;

//***************************** Main Code ****************************//

initial begin

clk = 1\'b1;

rst <= 1\'b0;

key_flag1 <= 1\'b0;

key_flag2 <= 1\'b0;

key_flag3 <= 1\'b0;

key_flag4 <= 1\'b0;

#201;

rst <= 1\'b1;

#200;

key_flag1 <= 1\'b1;

#100;

key_flag1 <= 1\'b0;

#20000000;

key_flag1 <= 1\'b1;

#100;

key_flag1 <= 1\'b0;

#20000000;

#20000000;

$stop;

end

// creator clk

always #10 clk <= ~clk;

//*************************** Instantiation **************************//

creat_PWMcreat_PWM_inst

(

.clk ( clk),

.rst ( rst),

.key_flag1 ( key_flag1 ),

.key_flag2 ( key_flag2 ),

.key_flag3 ( key_flag3 ),

.key_flag4 ( key_flag4 ),

.PWM ( PWM)

);

endmodule

對應(yīng)的原始code中的參數(shù)如果修改一下是可以大幅縮短仿真時間,但是一時沒有想起對應(yīng)的修改模塊內(nèi)部變量的方法,后面找到后再進(jìn)行補(bǔ)充。

寫的還是感覺比較差勁,只能說說慢慢進(jìn)步吧,自己也是自學(xué)不久。

發(fā)表于 12-12 10:47

由于今天連續(xù)多次無法發(fā)布該文章,心態(tài)真的是崩了,由于基礎(chǔ)的PWM比較簡單,此次先給大家展示個半成品,完整狀態(tài)對應(yīng)的PWM頻率、占空比均可調(diào)節(jié),對應(yīng)的模塊結(jié)構(gòu)圖如下:

對應(yīng)的基本code如下:

modulecreat_PWM

(

inputwireclk, //系統(tǒng)時鐘為50MHz

inputwirerst,

inputwirekey_flag1,

inputwirekey_flag2,

output regPWM

);

parameter Frequency_CNT_MAX = 16\'d49_999; //輸出PWM為1KHz,1ms=5000*20ns

//PWM頻率生成計數(shù)器模塊

reg [15:0] couter;

always @(posedge clk or negedge rst)

if( rst == 1\'b0 )

couter <= 0;

else if( couter == Frequency_CNT_MAX )

couter <= 0;

else

couter <= couter + 1\'b1;

//占空比調(diào)節(jié)模塊

reg [15:0] duty_counter;

always @(posedge clk or negedge rst)

if( rst == 1\'b0 )

duty_counter <= 16\'d24_999;

else if( key_flag1 == 1\'b1 )

duty_counter <= duty_counter + 16\'d49;

else if( key_flag2 == 1\'b1 )

duty_counter <= duty_counter - 16\'d49;

else

duty_counter <= duty_counter;

//生成PWM

always @(posedge clk or negedge rst)

if( rst == 1\'b0 )

PWM <= 1\'b0;

else if( duty_counter <= Frequency_CNT_MAX )

PWM <= 1\'b1;

else

PWM <= 1\'b0;

endmodule

由于是第一次在電子發(fā)燒友上發(fā)文章,體驗感覺真的不太友好,希望能夠把文章的自動保存功能給加上,否則沒有備份真的讓人不開心

發(fā)表于 12-06 21:56

FPGA 年度關(guān)鍵詞,我的想法是“標(biāo)準(zhǔn)化”;今年的工作中遇到了不少同事的issues,本身都是小問題或者很細(xì)節(jié)的東西但是卻反復(fù)出現(xiàn)問題,目前想到的最好的辦法是做好設(shè)計規(guī)則的標(biāo)準(zhǔn)化才能避免,不知道大家有沒有更好的建議?

發(fā)表于 12-06 20:31

“楊老師模擬課”是西安交通大學(xué)電氣工程學(xué)院教授、博士生導(dǎo)師、工學(xué)博士楊建國在多年的執(zhí)教與科研時間中,積累的問題與詳細(xì)解答,并從中精選了最具代表性的10個問題,做出了10堂視頻課,結(jié)合PPT,細(xì)致逐步講解。

“楊老師模擬課”是西安交通大學(xué)電氣工程學(xué)院教授、博士生導(dǎo)師、工學(xué)博士楊建國在多年的執(zhí)教與科研時間中,積累的問題與詳細(xì)解答,并從中精選了最具代表性的10個問題,做出了10堂視頻課,結(jié)合PPT,細(xì)致逐步講解。

放大器是一種有源器件,需要供電才能工作,電源的不同選擇和設(shè)置也會對放大器參數(shù)性能產(chǎn)生影響,因此,不管您是已入職場的設(shè)計人員,還是在正在學(xué)習(xí)電路設(shè)計的學(xué)生,都應(yīng)該對放大器電源有更多的了解。《放大器電源的那些事兒》由ADI放大器應(yīng)用工程師錄制,合計22小節(jié)內(nèi)容,主要介紹放大器的電源應(yīng)用的相關(guān)注意事項。

放大器是一種有源器件,需要供電才能工作,電源的不同選擇和設(shè)置也會對放大器參數(shù)性能產(chǎn)生影響,因此,不管您是已入職場的設(shè)計人員,還是在正在學(xué)習(xí)電路設(shè)計的學(xué)生,都應(yīng)該對放大器電源有更多的了解。《放大器電源的那些事兒》由ADI放大器應(yīng)用工程師錄制,合計22小節(jié)內(nèi)容,主要介紹放大器的電源應(yīng)用的相關(guān)注意事項。

?

?

?

?

?

? ?

? ?

?

?

? ?

?

?

?

?

? ?

? ?

?

?

?

精密技術(shù)信號鏈允許在各種設(shè)計權(quán)衡之間輕松變換,以為應(yīng)用創(chuàng)建優(yōu)質(zhì)的終端解決方案。利用ADI公司完整的精密技術(shù)信號鏈加速技術(shù)選擇和實(shí)施,這些信號鏈匯集了50多年的洞察力和專業(yè)知識。結(jié)合適當(dāng)?shù)墓ぞ摺iT開發(fā)的知識庫和可定制的解決方案,ADI的精密技術(shù)信號鏈能夠輕松采用。相關(guān)鏈接:

精密技術(shù)信號鏈允許在各種設(shè)計權(quán)衡之間輕松變換,以為應(yīng)用創(chuàng)建優(yōu)質(zhì)的終端解決方案。利用ADI公司完整的精密技術(shù)信號鏈加速技術(shù)選擇和實(shí)施,這些信號鏈匯集了50多年的洞察力和專業(yè)知識。結(jié)合適當(dāng)?shù)墓ぞ摺iT開發(fā)的知識庫和可定制的解決方案,ADI的精密技術(shù)信號鏈能夠輕松采用。相關(guān)鏈接:

?

? ?

?

各位小伙伴,這些關(guān)鍵詞你是否也搜索過呢?

快來回顧一下,分享你在今年搜索最多的關(guān)鍵詞!以及它們是否成為了你的助力,為你的設(shè)計再添一份創(chuàng)新呢?

各位小伙伴,這些關(guān)鍵詞你是否也搜索過呢?

快來回顧一下,分享你在今年搜索最多的關(guān)鍵詞!以及它們是否成為了你的助力,為你的設(shè)計再添一份創(chuàng)新呢?

ADI年度關(guān)鍵詞曝光,這些你肯定搜索過!

ADI年度關(guān)鍵詞曝光,這些你肯定搜索過!

評論