Matlab操作ZedBoard+AD9361產(chǎn)生信號(hào)

之前我們基于matlab板級(jí)支持包在matlab的控制下,利用ZedBoard+AD9361的硬件板卡套裝產(chǎn)生了點(diǎn)頻信號(hào)。

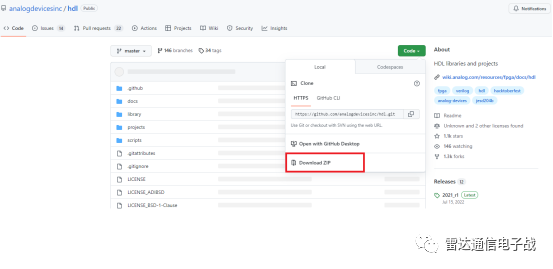

今天我們使用ADI在github上提供的HDL源碼來(lái)構(gòu)建zedboard+AD9361的vivado工程。

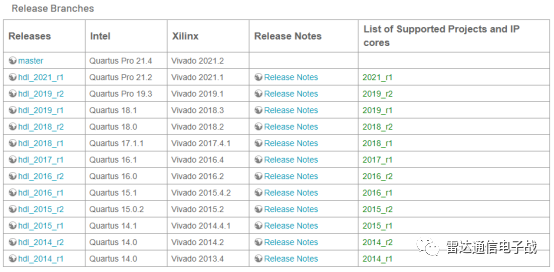

根據(jù)你vivado的版本選擇對(duì)應(yīng)的內(nèi)容下載,我們使用的是vivado2021.2,直接下載master即可。

?

?

解壓所下載的文件,使用“.../hdl-master/projects/fmcomms2/zed”文件路徑下的system_project.tcl文件來(lái)構(gòu)建工程。

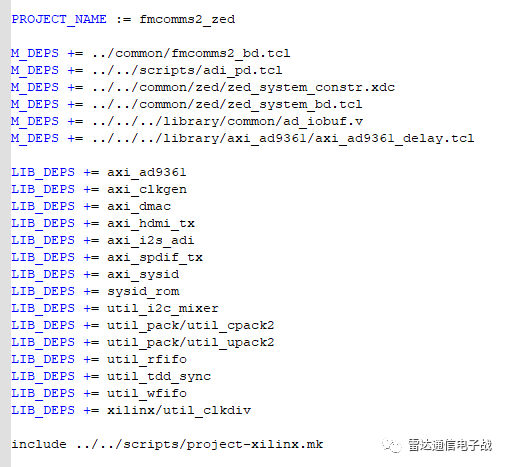

但是在構(gòu)建工程之前,需要先編譯庫(kù)文件,具體需要編譯哪些庫(kù)可以通過(guò)打開該路徑下的Makefile查看:

打開vivado,在tcl命令框內(nèi)輸入cd d:/hdl-master/library/axi_ad9361,然后再運(yùn)行 source ./axi_ad9361_ip.tcl,或者點(diǎn)擊“tools”->“run tcl script”找到axi_ad9361_ip.tcl進(jìn)行編譯庫(kù)文件,等待編譯完成。 接著繼續(xù)用同樣的方法編譯Makefile中列出的其他IP,所有IP編譯完成后執(zhí)行: cd d:/hdl-master/projects/fmcomms2/zed, 然后運(yùn)行source ./system_project.tcl開始編譯生成vivado工程。

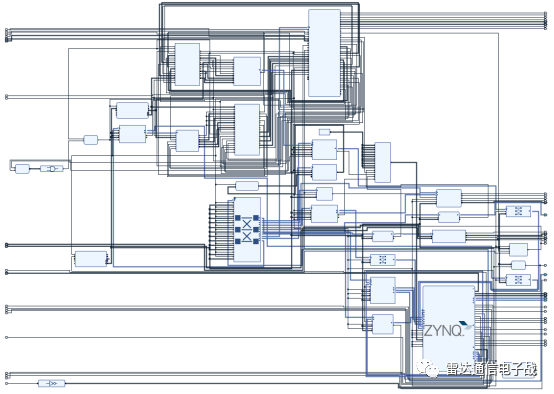

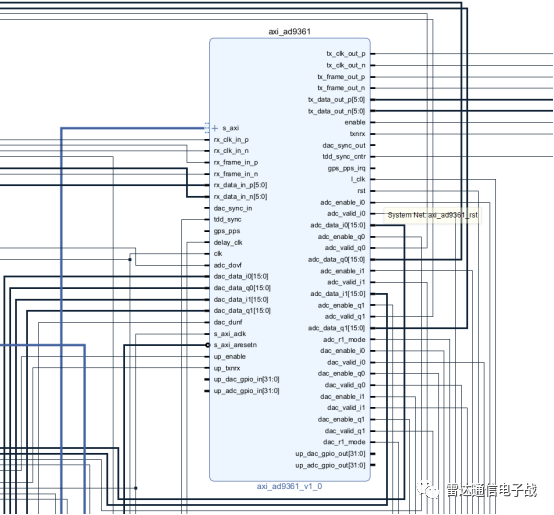

放大看一下AD9361核的連線:

在構(gòu)建工程的過(guò)程中需要注意的地方:

1,HDL源碼下載的版本需要與你安裝的vivado版本一致。

2,其中用到的路徑需要和你放文件的路徑一致,并且需要注意路徑中斜杠的方向,與電腦復(fù)制的路徑斜杠方向不一樣;

3,若在構(gòu)建時(shí)報(bào)錯(cuò),可以查看log看那里出錯(cuò),很大可能是還有哪些IP沒(méi)有編譯。

4,若你想生成更高版本的vivado工程,可以先構(gòu)建完成后再升版本。

審核編輯:劉清

-

HDL

+關(guān)注

關(guān)注

8文章

324瀏覽量

47230 -

TCL

+關(guān)注

關(guān)注

10文章

1699瀏覽量

88272 -

AD9361

+關(guān)注

關(guān)注

8文章

34瀏覽量

36964

原文標(biāo)題:使用源碼構(gòu)建ZedBoard+AD9361的vivado工程

文章出處:【微信號(hào):雷達(dá)通信電子戰(zhàn),微信公眾號(hào):雷達(dá)通信電子戰(zhàn)】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

proteus能產(chǎn)生雙頻信號(hào)或者多頻信號(hào)嗎?

[AD9361][Zedboard]如何透過(guò)matlab讀寫AD9361的Register Value?

AD9361發(fā)射單頻信號(hào)接收到的信號(hào)存在明顯的諧波

AD9361射頻FMC板卡

AD9361無(wú)發(fā)射信號(hào)

AD9910產(chǎn)生點(diǎn)頻信號(hào)鎖相環(huán)不能鎖定

怎么產(chǎn)生的高頻信號(hào)?

AD9361發(fā)送調(diào)試沒(méi)有找到1M正弦波的信號(hào)?

AD9361信號(hào)輸出的問(wèn)題

AD9361 BIST模式

利用定時(shí)/計(jì)數(shù)器產(chǎn)生音頻信號(hào)的方法

自動(dòng)產(chǎn)生點(diǎn)和劃的電碼練習(xí)振蕩器電路圖

如何利用ZedBoard+AD9361的硬件板卡套裝產(chǎn)生點(diǎn)頻信號(hào)呢

如何利用ZedBoard+AD9361的硬件板卡套裝產(chǎn)生點(diǎn)頻信號(hào)呢

評(píng)論