大家好,我是硬件花園,一名樂于分享的硬件工程師。關注我,了解更多精彩內容!

1 前言

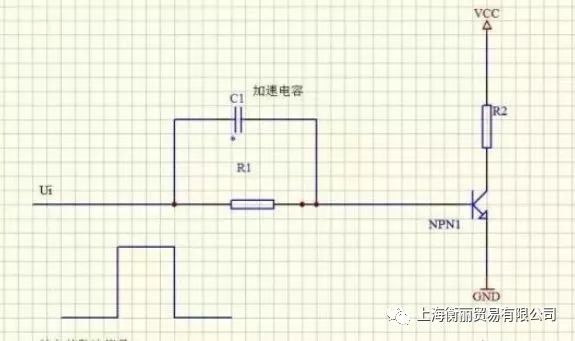

加速電容一般應用于高速場合,在相同容值的情況下優先使用高頻特性好的瓷片電容,如果驅動電路中要求加速電容承受負壓則必須選擇無極性電容如瓷片電容。下文主要從電容的大小來分析阻容負載驅動電路和晶體管驅動電路中加速電容的選型。

2 加速電容選型

2.1 阻容負載驅動電路加速電容大小選擇

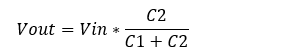

當階躍開始瞬間t=0時輸出電壓為:

當負載電容充電完成,階躍穩定t=∞時輸出電壓為:

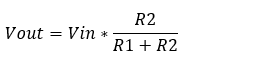

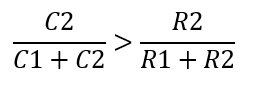

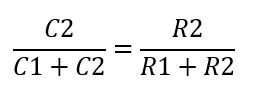

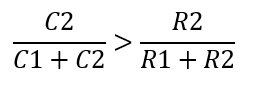

從上面的分析可以看出在整個階躍響應過程中輸出電壓分為兩個階段,電壓突變開始時輸出電壓值由電容分壓決定,當負載電容完成充電后輸出電壓值由電阻分壓決定。所以如果

,輸出電壓會有拐點。

當

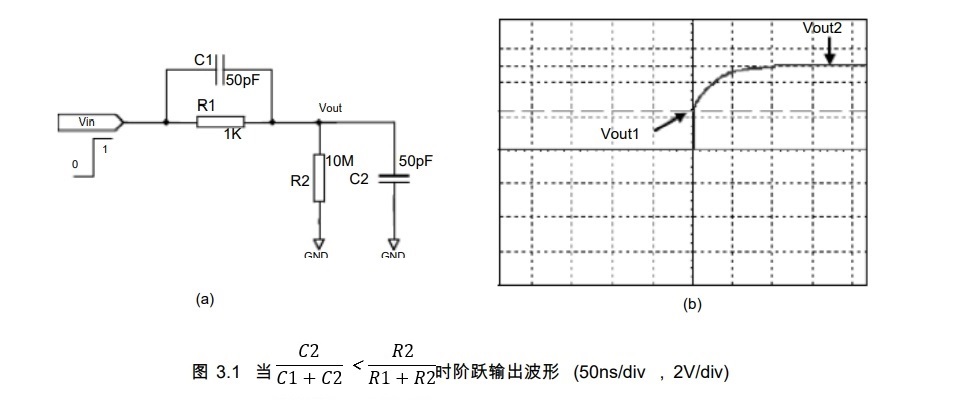

時,如圖3.1所示C1=50pF,C2=50pF,R1=1K,R2=10M,輸入5V階躍的輸出波形。

上圖中,Vout1=2.50V,Vout2=4.99V,輸出電壓首先迅速上升到Vout1再緩慢上升到Vout2,出現了明顯的上升拐點。 當

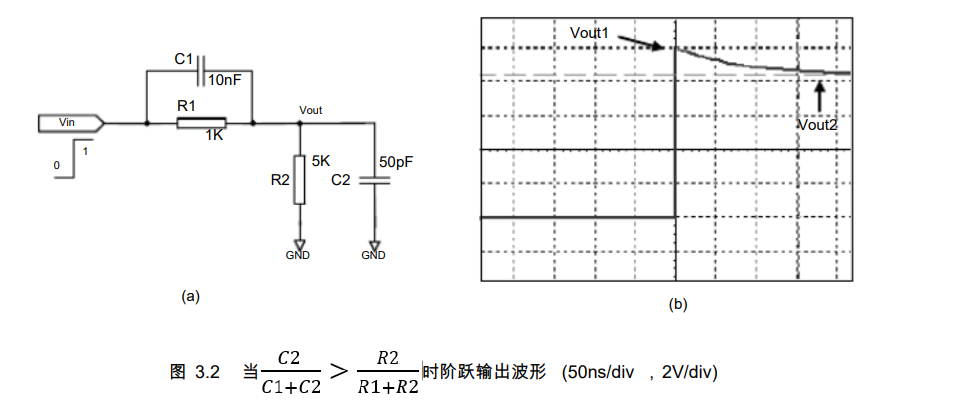

時,如圖3.2所示C1=10nF,C2=50pF,R1=1K,R2=5K。輸入5V階躍的輸出波形。

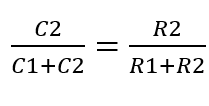

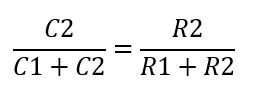

上圖中,Vout1=4.97V,Vout2=4.17V,輸出波形電壓首先迅速上升到Vout1再緩慢下降到Vou2出現明顯的過沖現象。 為了取得理想的輸出波形,加速電容C1應該滿足

比例關系,但是電容取值有限,很難做到。 實際應用中只要使得二者取值接近就可以了。 以圖3.2中的驅動電路為例,負載電阻R2=5K,負載電容C2=50pF,驅動電阻R1=1K,根據

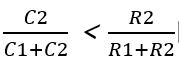

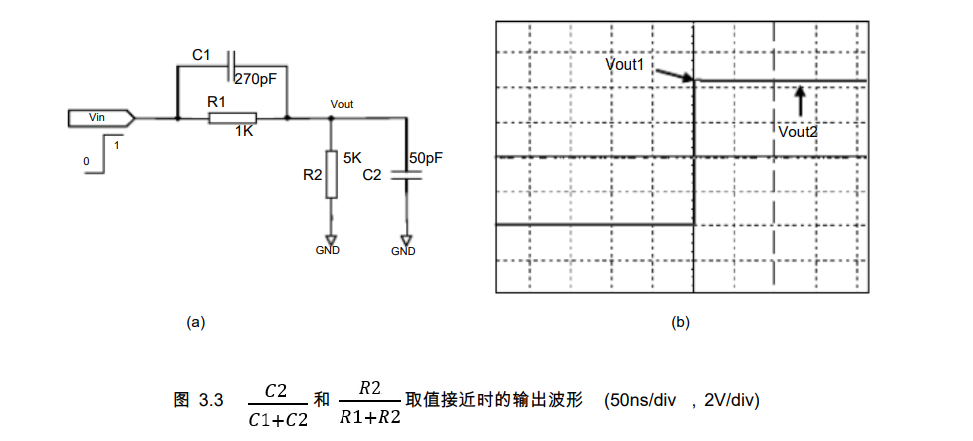

可以求得理想的加速電容值為250pF,但是250pF不是通用的電容取值,可以使用通用的270pF來代替,雖然

但是二者取值已經非常接近。可以滿足一般的應用要求。如圖3.3所示為加速電容C1=270pF時的輸出波形,Vout1=4.21V,Vout2=4.16V。

2.2 晶體管驅動電路加速電容大小選擇

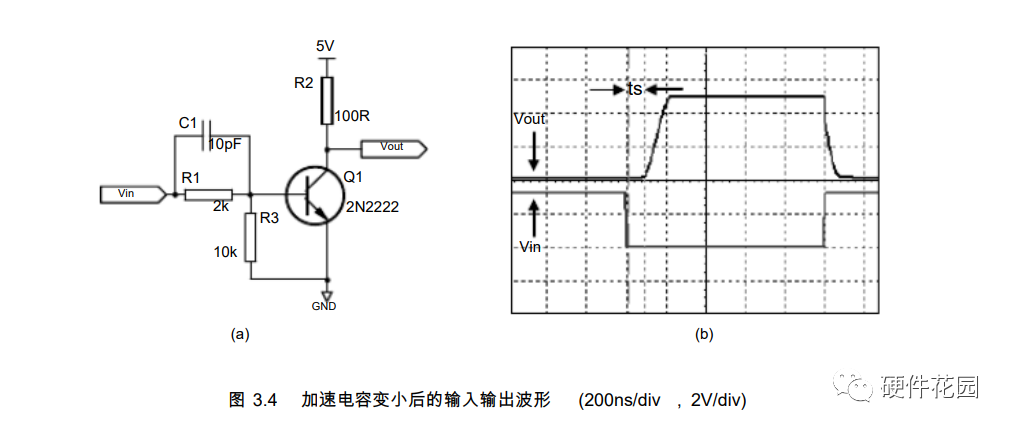

將在《加速電容在電路中的妙用》中提到的圖2.4電路中的加速電容從1nF換成10pF,在相同的測試條件下使用Multisim仿真輸入和輸出波形如圖3.4所示。

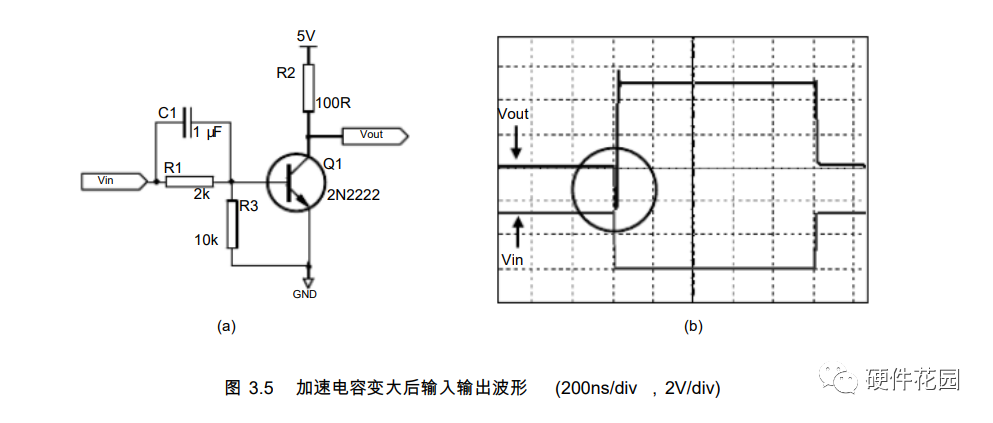

從上圖看出,輸入和輸出波形仍然會有存儲時間ts=90ns,加速電容變小后其存儲的電荷減少了,不能完全中和掉基區的過量電荷,剩余的電荷通過電阻緩慢釋放,所以輸入輸出仍然存在延遲。通過實際測試,加速電容越大存儲時間越小,但并不是電容越大越好。將圖2.4電路中的加速電容從1nF換成1uF,在相同的測試條件下使用Multisim仿真輸入和輸出波形如圖3.5所示。

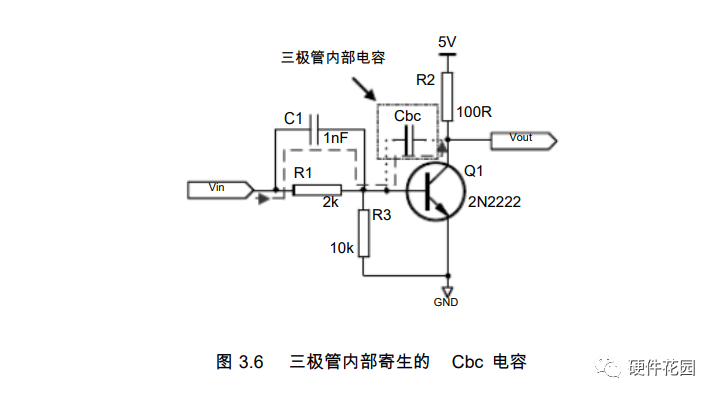

從上圖看出,電容加大后存儲時間基本消除了,但是輸出波形存在嚴重的下沖現象達到了-2.2V。三極管的集電極和基極之間存在一個寄生電容Cbc如圖3.6所示,不同的三極管Cbc大小存在差異,2N2222內部的Cbc為10pF,輸入高電平時加速電容充電,最終在C1兩端產生(Vin-0.7)V的電壓差,當從高電平降到低電平的瞬間,由于C1兩端電壓不能突變在基極產生一個放電電壓,同時Cbc電容兩端電壓也不能突變,基極的放電電壓會通過Cbc影響集電極的輸出電壓。

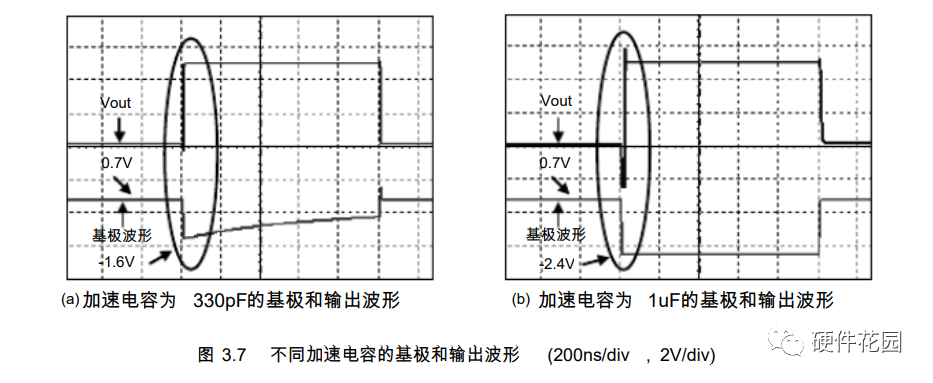

C1電容大小會影響基極的放電電壓。如圖3.7所示,C1電容變小時,其存儲的電荷減少了,在基極產生的放電電壓幅值變小,輸出電壓基本無過沖,C1電容變大后,存儲電荷增多了,在基極產生的放電電壓幅值變大,輸出電壓出現明顯過沖。

根據上述分析,在晶體管驅動電路中,加速電容如果選擇過小仍然會有延遲時間,如果過大則會造成輸出波形出現過沖,所以電容值應該通過實測具體電路的輸出波形來選擇。

審核編輯:湯梓紅

-

電容

+關注

關注

99文章

6001瀏覽量

150039 -

晶體管

+關注

關注

77文章

9641瀏覽量

137876 -

驅動電路

+關注

關注

152文章

1521瀏覽量

108386 -

加速電容

+關注

關注

0文章

15瀏覽量

2127

原文標題:加速電容在電路中如何選型?

文章出處:【微信號:硬件技術后花園,微信公眾號:硬件技術后花園】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

電容在電源電路中的作用 電容在交流電路中的使用

低壓電容器在冶金行業中的選型案例

晶振過驅的影響及其預防措施:電阻與電容在晶振電路中的應用

igbt尖峰吸收電容選型方法

無功補償電容容量下降如何優化

加速電容在電路中如何選型?

加速電容在電路中如何選型?

評論