作者:Joseph Spencer and Gabino Alonso

在LTspice中設計電路時,您可能希望評估元件容差的影響。例如,運算放大器電路中非理想電阻引入的增益誤差。本文介紹了一種方法,該方法可減少所需的模擬數量,從而加快獲得結果的時間。

改變參數

LTSpice 提供了幾種改變參數值的方法。其中一些是:

.步參數;用戶定義變量的參數掃描

高斯(X);來自高斯分布的隨機數,西格瑪為 x

平(x);介于 -x 和 x 之間的隨機數,分布均勻

MC(x,y);介于 x*(1+y) 和 x*(1-y) 之間的隨機數,分布均勻。

這些函數非常有用,特別是當我們想從分布的角度查看結果時。但是,如果我們只想查看最壞的情況,它們可能不是獲得結果的最快方法。例如,使用gauss(x),flat(x)和mc(x,y)將需要模擬運行統計上顯著的次數。從那里,可以查看分布,并根據標準差計算最壞情況值。但是,對于最壞情況分析,我們不希望使用分布方法,而是在計算中使用與每個分量標稱值的最大偏差。

運行最小模擬

假設我們想看看容差為1%的R1 = 22.5kΩ電阻的最壞情況影響。在這種情況下,我們實際上只想運行R1 = 22.5kΩ * (1 - 0.01)和22.5kΩ * (1 + 0.01)的仿真。使用理想的22.5kΩ電阻進行第三次運行也很方便。

.step param R1 列表 22.5k*(1-.01) 22.5k*(1+.01) 22.5k

如果我們只是改變一個電阻值,“.step 參數”方法將非常有效。但是,如果我們擁有更多呢?經典差動放大器有4個電阻。

圖1.差動放大器配置 (來自 LT1997-3 的產品手冊)

如果要設計分立差動放大器,每個差動放大器都有一定的容差(例如1%或5%)。

例如,讓我們以 LT1997-3 數據手冊中所示的首頁應用為例,并在 LTspice 中采用一個分立式 LT6015 運放和一些非理想電阻器來實現該應用。

圖2.LT1997-3 首頁應用示例

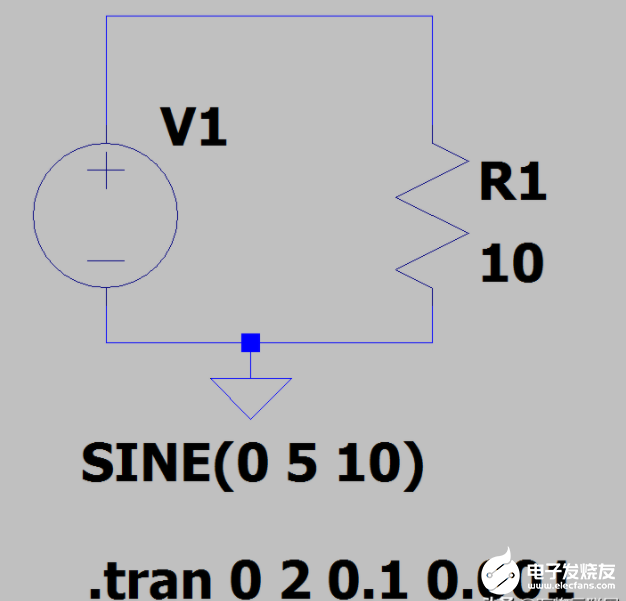

圖3.LT6015 具有非理想電阻器的差動放大器

請注意,電阻R1、R2、R3和R4的值被函數調用wc(標稱值、容差、指數)所取代,該函數在仿真中由 .函數聲明:

.func wc(nom,tol,index) if(run==numruns,nom,if(binary(run,index),nom*(1+tol),nom*(1-tol)))

此函數與下面的二進制(run,index)函數結合使用,在最大值和最小值之間改變每個組件的參數,并在最后一次運行中改變標稱值。

.func binary(run,index) floor(run/(2**index))-2*floor(run/(2**(index+1)))

二進制函數在模擬中切換每個索引組合,以便模擬 nom*(1+tol) 和 nom*(1-tol) 的所有可能組合。請注意,組件索引應以 0 開頭。下表突出顯示了 binary() 函數的操作以及每個索引和運行的結果,其中 1 表示 nom*(1+tol),0 表示 nom*(1-tol)。

| 跑 | 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14 | 15 |

| 索引 0 (R4) | 0 | 1 | 0 | 1 | 0 | 1 | 0 | 1 | 0 | 1 | 0 | 1 | 0 | 1 | 0 | 1 |

| 索引 1 (R1) | 0 | 0 | 1 | 1 | 0 | 0 | 1 | 1 | 0 | 0 | 1 | 1 | 0 | 0 | 1 | 1 |

| 索引 2 (R2) | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 |

| 索引 3 (R3) | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

運行次數確定買入2N+1,其中 N 等于索引組件的數量,以涵蓋器件的所有最大和最小組合加上標稱值。在我們的例子中,我們需要運行 17 個模擬,我們可以使用 .step 命令和 .param 語句來定義它:

.step param run 0 16 1

.param numruns=16

最后,我們需要通過 定義用于仿真的 tola 和 tob。參數語句:

.param tola=.01 .param tolb=.05

您可以在幫助 (F1) 和 . 參數部分詳細介紹了 if(x,y,z) 和 floor(x) 函數。

正在繪制 .分步結果

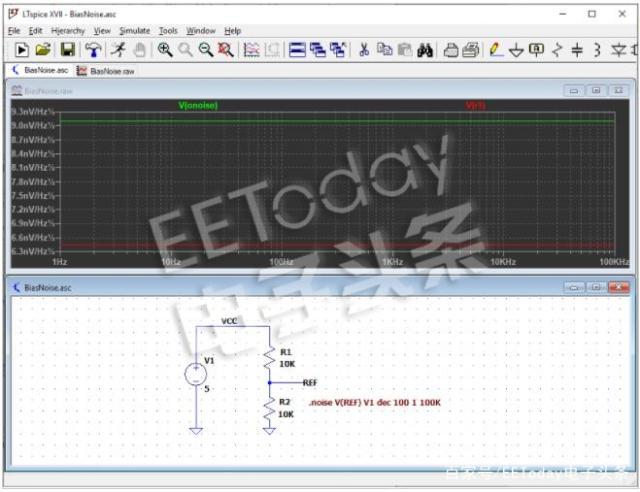

如果運行瞬態分析模擬,請參閱 WorstCase_LT6015.asc 文件,我們可以觀察我們的結果。對于250mA測試電流,我們預計Vout網絡將穩定至250mV。但是現在有了我們的wc()函數,我們得到了從235mV到265mV的擴展。

圖4.差動放大器瞬態分析

正在繪制 .踩踏 .測量聲明

此時,我們可以放大并查看峰值到峰值的傳播。但是,讓我們從另一個LTspice博客中吸取教訓:

繪制參數與時間以外的其他因素(例如電阻)

本博客介紹了如何多次運行模擬,以及如何針對時間以外的其他內容繪制參數。在本例中,我們要繪制 V(out) 與模擬運行指數。請參閱 WorstCase_LT6015_meas.asc 文件。

在此模擬中,我們添加了一個 .MEAS語句來計算輸出的平均電壓。

.meas VoutAvg avg v(out)

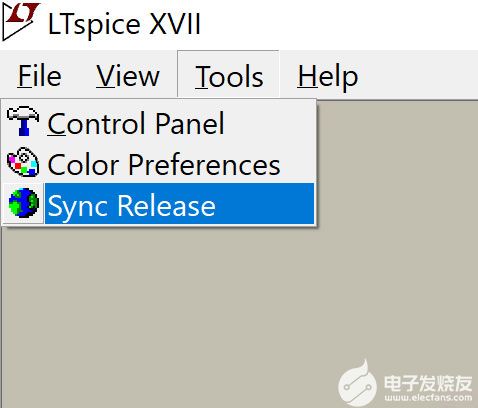

要繪制 V(out) 與運行參數,我們可以查看 SPICE 錯誤日志 (Ctrl-L),右鍵單擊并選擇繪制 .step'ed .meas 數據。

圖5.香料錯誤日志接口

我們的 .step'ed 的繪圖結果 .測量數據。

圖6.輸出電壓與仿真運行的關系

跟蹤告訴我們,結果從最大最差情況265mV(運行9)到最小最差情況235mV(運行6)或大約±6%誤差不等。這很直觀,因為在這個例子中,我們同時使用了1%和5%的電阻。最后一次運行(16)顯示了理想結果(250mV),這是理想的電阻。回想一下LTspice繪制的結果。MEAS 語句作為分段線性圖。

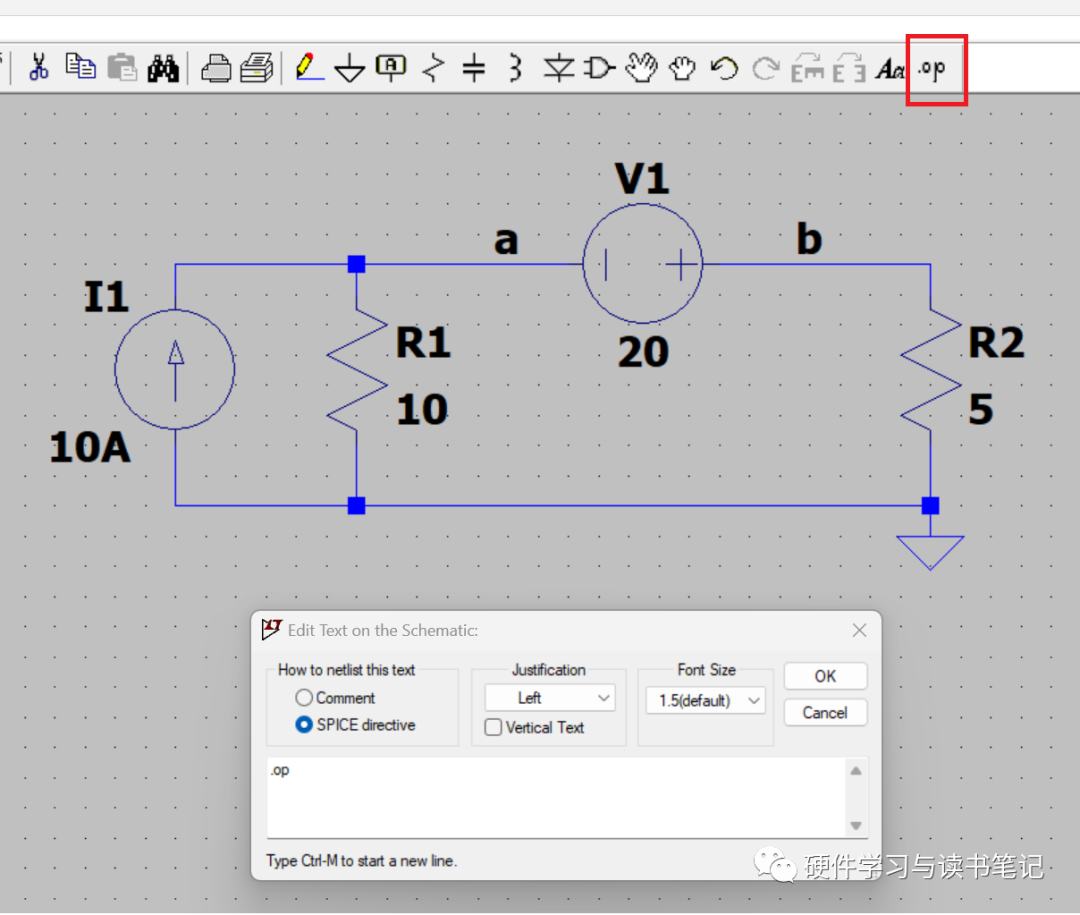

處理此特定電路的另一種更快方法是使用 .運算仿真(而不是 .trans)來執行直流工作點解決方案,該解決方案將繪制我們的步進結果。直接測量數據。

匹配電阻的值

在設計差動放大器時,不僅需要合適的運算放大器,而且電阻的匹配同樣重要。以下參考文獻很好地詳細解釋了這個主題(和相關數學):

LT5400 (四通道匹配電阻器網絡) 數據表

設計說明 DN1023

設計說明 DN502

但是,如果沒有適當匹配的電阻,則無法實現良好的共模抑制比(CMRR)或增益誤差。

凌力爾特現為ADI公司的一部分,擁有許多精密放大器產品,其中還包括匹配電阻。最近發布的一個示例是 LT1997-3 - 精準、寬電壓范圍增益可選放大器。兩個關鍵規格是:

91dB 最小直流共模抑制比(增益 = 1)

0.006% (60ppm) 最大增益誤差(增益 = 1)

這些規格確實非常出色。根據 DN1023,僅由 1% 電阻(使用理想運算放大器)引起的 CMRR 會將 CMRR 限制在 34dB。當然,增益誤差比LT1997-3所實現的誤差差幾個數量級。

總結

使用上述方法,可以在幾個參數的最小值/最大值下運行簡單的最壞情況分析。在本例中,我們研究了經典差動放大器中電阻容差的影響,并說明了LT1997-3中匹配電阻的值。

審核編輯:郭婷

-

放大器

+關注

關注

143文章

13434瀏覽量

212189 -

運算放大器

+關注

關注

213文章

4812瀏覽量

171734

發布評論請先 登錄

相關推薦

電子可靠性技術:最壞情況分析方法

使用LTspice仿真功能檢查電源啟動時的運作情況

LTSPICE運行仿真時報錯怎么解決?

在LTspice中導入模型時遇到相關問題

正確執行最壞情況電路分析所需的技能

LTspice中使用蒙特卡羅和高斯分布進行容差分析和最差情況分析的方法

如何用LTspice對EMC濾波器進行精確的仿真模擬

如何啟動并運行LTspice

爆款課程【LTspice在放大器電路仿真中的應用】進階版上線,火速碼!

LTspice:最壞情況電路分析,仿真運行最少

LTspice:最壞情況電路分析,仿真運行最少

評論