該芯片作為PHY和SERDES使用

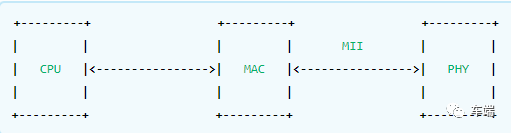

MII 是一個標準接口,用于連接 MAC 和 PHY。MII 是 IEEE-802.3 定義的以太網標準, MII 接口可以同時控制多個 PHY。

MII包含兩個接口:

1.一個數據接口,用戶 MAC 和 PHY 之間收發 Ethernet 數據 2.一個管理接口,這個管理接口通常稱為 MDIO,MIIM 或者 SMI。 這個接口用于 MAC 從 PHY 讀取相關管理寄存器的值,或者往 PHY 管理寄存器上寫入數據。

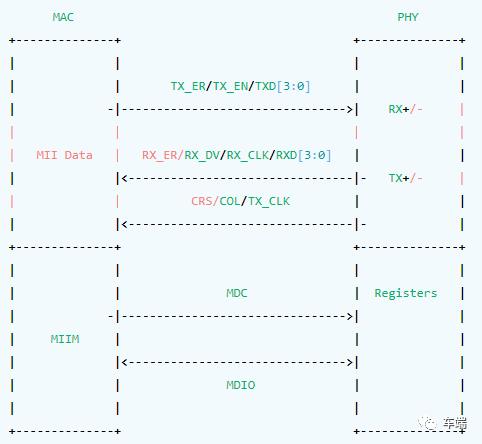

MDIO

MDIO 也被稱為 MIIM,或者SMI,它是 IEEE802.3 定義標準 MII 接口的一部分,用于 MAC 配置 PHY。MDIO 具有兩個信號線,分別如下:

1. MDC 時鐘線:MDIO 的時鐘信號,由 MAC 驅動 PHY 2. MDIO 數據線:雙向數據線,用于在 MAC 和 PHY 之間傳輸配置信息

MDIO 總線只支持 MAC 作為主設備,PHY 作為從設備。MIDO 支持兩種時序,分別為Clause 22和Clause 45.

MDIO接口最初是由IEEE RFC802.3中的22號條款定義的,在最初的定義中,一個單獨的MDIO接口可以訪問32個不同的PHY設備中的32個寄存器,這些寄存器提供狀態和控制信息,例如:連接狀態、傳輸速度能力、當前選擇的傳速、低壓消耗時的下電情況、全雙工還是半雙工、自動協商、錯誤提示以及反饋信息等等。

為了滿足10G以太網設備的普及發展,在IEEE 802.3ae 的45號條款中為MDIO接口提供了額外的規范:

1)能夠通過32個端口訪問32個不同設備的65536個寄存器;

2)為訪問10G以太網提供額外的OP碼和ST碼,從而可以直接訪問寄存器地址;

3)端到端的報錯信號;

4)環回模式控制;

5)低壓電氣標準。

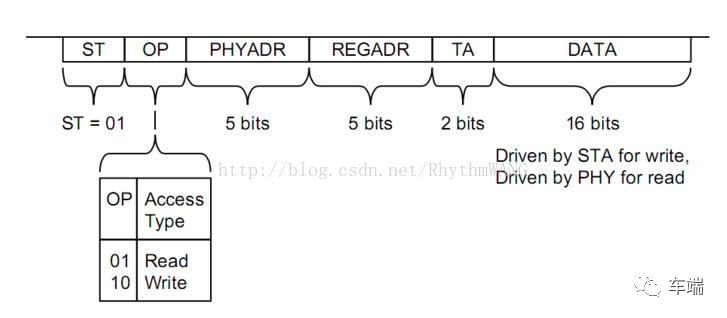

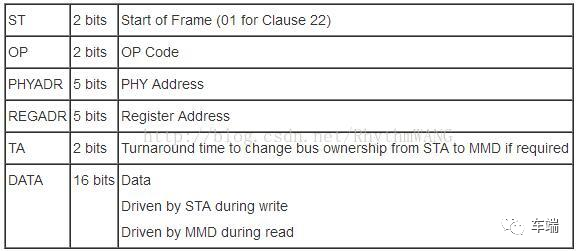

22號條款

22號條款的MDIO通信的幀格式定義如下:

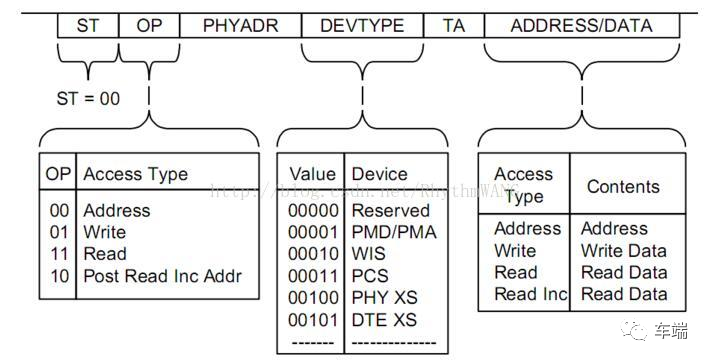

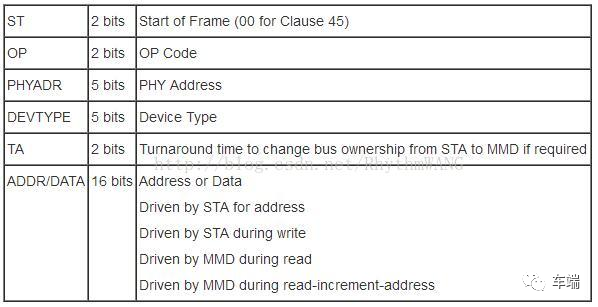

45號條款

為了彌補22號的條款中定義的缺陷,45號條款中增添了對低壓設備的支持,最低可到1.2V,同時擴充了幀格式,能夠訪問更多的設備和寄存器。

45號MDIO通信幀格式如下:

第45號條款的主要變化是如何訪問寄存器。在第22中,一個單獨的幀指定要讀或寫的地址和數據,同時完成了這些工作。45號中改變這種范式,第一個地址幀發送到指定的MMD和寄存器,然后發送第二幀來執行讀或寫。

工作模式

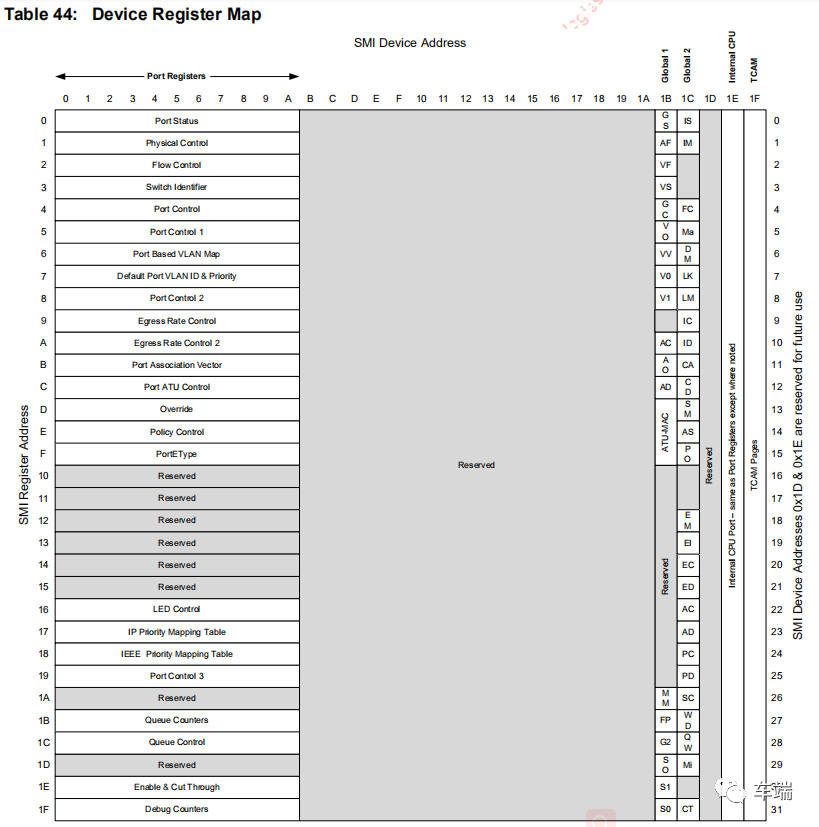

該芯片有兩種尋址模式:單芯片尋址和多芯片尋址。

多芯片尋址

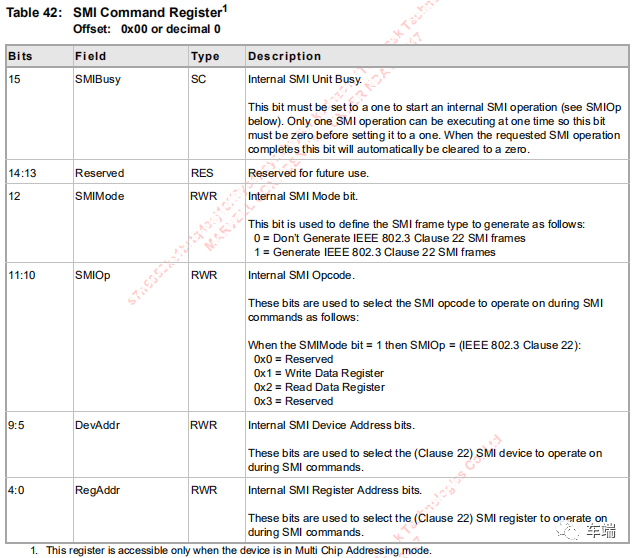

對于多芯片尋址,需要給芯片設置一個非零的SMI地址(ADDR[4:0]的反碼)。在多芯片尋址模式下,僅有兩個寄存器(0x00:SMI Command Register 0x01:SMI Data Register)能夠使用,內部各PORT的寄存器均由這兩個寄存器間接訪問。

通過向SMI Command Register的[9:5]寫入內部SMI設備地址,[4:0]寫入內部SMI寄存器地址來訪問各個Port的內部寄存器,[11:10]決定決前是寫入還是讀出操作。

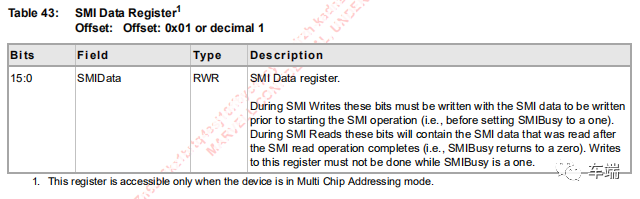

通過向SMI Data Register的[15:0]位寫入或讀取SMI Command Register設定的寄存器內容。

單芯片尋址

對于單芯片尋址,其SMI地址為0x00(針對整個芯片),即ADDR[4:0]=0x1F。

在單芯片尋址模式下,每個Port都有各自的SMI地址(針對內部每個Port),Port0-Port9對應的SMI地址分別為0x0-0x9(直接訪問),port10對應0xA。

若Port0、1、2等接有外部PHY,則必須使用以下SMI地址,0x00對應Port0,0x01對應Port1,這樣PPU才能自動的輪詢各個PHY獲取各自的連接狀況,速度,雙工情況,流控狀態等信息,這些外部PHY需要使用Global2 offset 0x18、0x19進行訪問。對于Port3a、Port4的內部PHY地址映射為0x03、0x04;Port9、Port10的內部SERDES映射為0x9、0xa,同樣的,也是需要使用Global2 offset 0x18、0x19進行訪問。

Global2 寄存器的 Offset24,25 寄存器

前文提到,兩個非常重要的寄存器,即Global2 offset 0x18、0x19寄存器,在單芯片尋址模式下PHY和SERDES寄存器的訪問都必須通過這兩個寄存器間接訪問。

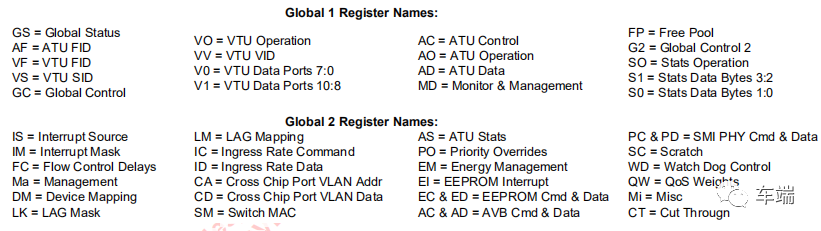

Global2 offset 0x18 (SMI PHY Command Register)寄存器

bit[12]指定了幀協議是22號時序還是45號時序。22號協議下,與多芯片存儲能夠訪問的Command Register寄存器一樣,[9:5]寫入SMI設備地址,[4:0]寫入SMI寄存器地址來訪問各個Port的內部寄存器,[11:10]決定當前是寫入還是讀出操作。45號協議,[9:5]指定port,[4:0]指定設備類別。

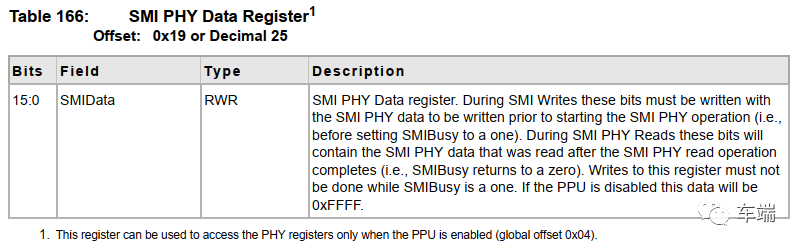

Global2 offset 0x19 (SMI PHY Data Register)寄存器

與SMI Data Register相同,通過[15:0]位寫入或讀取SMI Command Register設定的寄存器內容。

在45號協議下,第一個地址幀發送到指定的MMD和寄存器,我們要把PHY Command Reg中的[11:10]置為0x00=write Address register,即在第一個幀中的最后16位數據中,指定要操作的寄存器的地址。隨后在第二個數據幀中,要把PHY Command Reg中的[11:10]置為0x01=write data register,即第二個幀中的最后16位寫入的是數據。

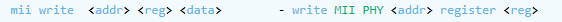

Uboot 中訪問 MDIO (SMI/MIIM)

項目開發中,經常要在 uboot 階段通過 MDIO 總線去配置 PHY 或者 SWITCH。

更多指令

示例:

6390xconfig **配置端口10** //0xa:P10 //0x34a: //bit[3:0]-0xa-接口配置模式-SGMII //bit[6]-0x1-EEE(EnergyEfficientEthernet)Enabled //bit[9:8]-0x3=10Gbor2500Mbps miiwrite0xa00x34a **配置端口5** //p5p177p355 //addr:0x1c //regi:0x19SMIDataregister //regi:0x18SMICommandregister //在45號條款中 //第一個地址幀發送到指定的MMD和寄存器,然后發送第二幀來執行讀或寫。 miiwrite0x1c0x190x2000//將數據0x2000寫到PHYdata寄存器0x19中 miiwrite0x1c0x180x82a4//將數據0x82a4寫到PHYCommand寄存器中 //0x82a4 //bit[15]:0x1——此位在首次操作SMI時,要置為1,并且在操作SMI完畢之后會自動清零 //bit[14:13]:0x0——內部訪問-用于訪問包含在這個設備中的內部PHYs和/或serde。 //bit[12]:0x0——SMIMODE——GenerateIEEE802.3Clause45SMIframes //bit[11:10]:0x0——WriteAddressRegister //bit[9:5]:寫入SMI設備地址-0x15——Port10Lane1=Port5&itsregistersareaccessedatSMIaddress0x15 //bit[4:0]:deviceclass(clause45) //第一個地址幀的后16位為Addr,即dataregister中的數據0x2000 miiwrite0x1c0x190x8140//將數據0x8140寫到PHYdata寄存器0x19中 miiwrite0x1c0x180x86a4//將數據0x86a4寫到PHYCommand寄存器中 ////bit[11:10]:0x01——WritedataRegister //第二個幀,后16位為要寫入的數據,即dataregister中的數據0x8140 編輯:黃飛

-

以太網

+關注

關注

40文章

5288瀏覽量

169679 -

Marvell

+關注

關注

10文章

352瀏覽量

123171 -

Mac

+關注

關注

0文章

1083瀏覽量

51142 -

交換芯片

+關注

關注

0文章

80瀏覽量

10943

原文標題:一文讀懂Marvell交換芯片

文章出處:【微信號:談思實驗室,微信公眾號:談思實驗室】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

以太網交換機芯片概述

Marvell交換芯片88E6097的電路設計原理

am3352的網口配置成mii模式網絡ping不通

具有單MII/RMII/Turbo MII支持LAN9303的以太網交換機

具有雙RMII或單MII / RMII / Turbo MII接口的全功能三端口以太網交換機

SDIO wifi Marvell8801是什么

自己實現SDIO wifi Marvell8801/Marvell88w8801驅動 介紹(一) ---- 芯片介紹 精選資料推薦

最近Marvell將 推出支持OpenFlow的交換機

MDIO接口的基礎知識詳解

STM32F103驅動SDIO wifi Marvell8801/Marvell88w8801 介紹(十) ---- 移植TCP/IP協議棧LWIP

交換芯片只適用在交換機上的?

以太網PHY芯片的MII接口和MDIO接口介紹

Marvell交換芯片介紹之MII、MDIO

Marvell交換芯片介紹之MII、MDIO

評論