實驗存儲系統設計實驗

本次實驗只有兩道題目,但其實具有一定難度,這兩題分別為漢字字庫存儲芯片擴展實驗和MIPS寄存器文件設計,這次實驗利用logisim進行設計,實驗報告分為兩個主要部分,在這兩個部分中依次對兩個實驗的方案設計,設計思路進行了介紹。

字庫存儲芯片擴展實驗

1.1設計要求

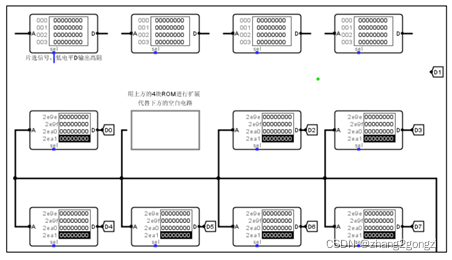

現有如下 ROM 組件,4片4K32位 ROM ,7片 16K32位 ROM,實驗中有一個 16*16 點陣字庫文件(存儲字庫的存儲系統),由 7 片 16K× 32 位 ROM 和一個空白器件構成。空白處表示缺少一個器件,請按照字擴展(容量擴展,地址線擴展)的方式利用圖中第一行所給出的 4 片 4K×32 位 ROM 的 存儲器完成最終字庫存儲器,并把字庫數據進行簡單的分割后,存入這 4 片 4K ×32 位的 ROM 中。

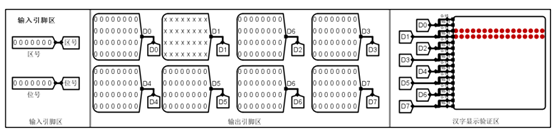

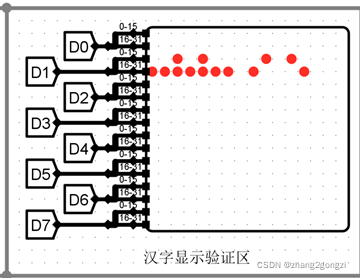

字庫電路輸入輸出引腳如圖所示,輸入引腳是 7 位的區號和位號;輸出 引腳是 32 位的 D7~D0,每一個輸出都是 32 位的漢字點陣信息,用于連接到漢 字點陣輸入端(拆分為高低 16 位)

1.2設計原理

1.2.1 字括展

由題目得,要求我們用4片4K×32 位ROM按照字擴展的括展方式實現16K×32位ROM,因此這邊給大家介紹一下字括展的原理

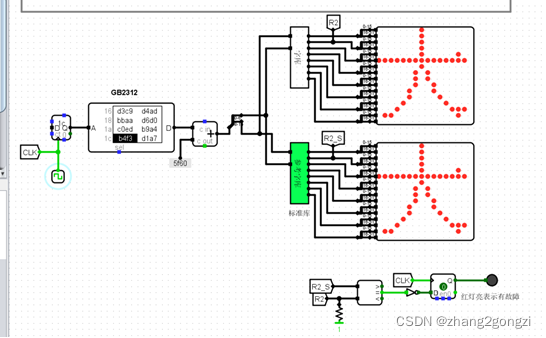

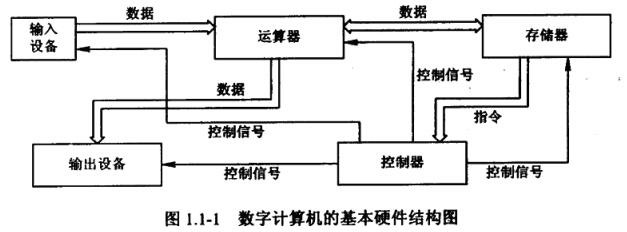

字括展也稱為容量括展或地址總線括展,當存儲芯片的存儲容量不能滿足存儲器對存儲容量的要求時,需要進行字括展的方式來括展,其中需要將所有存儲芯片的數據線,讀寫控制線各自并聯,同時分別與CPU的數據線和讀寫控制線連接,各存儲芯片的片選信號可以由CPU多余的地址線通過譯碼器譯碼產生,通過計算得出,為實現上圖電路,共需要16K/4K=4個ROM芯片實現

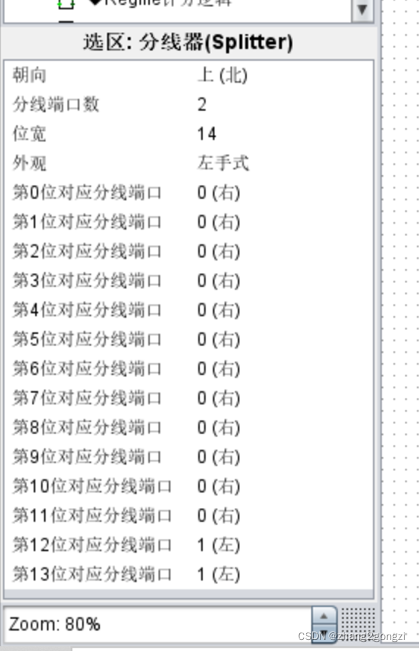

1.2.2 地址線連接

cpu分為地址線、數據線和控制線,地址線是用來傳輸地址信息用的,因為需要16K×32位的ROM系統,所以目標芯片中含有16K個地址,對應著14條地址線(2的14次方=16K),其中備用芯片12條地址線,高兩位(分線器分開)用作片選,可以接到2-4譯碼器的輸入端,在這邊的話,需要分線器進行工作,將14個地址分開,分為低12位和高兩位,對其進行編輯,將0-11設為0,其他位為1,高兩位地址用于芯片的選擇。

低 12 位地址直接連 4K×32b 的 ROM 芯片的地址線。4 個芯片的 32 位輸出直接連到 D1,因為同時只有一個芯片工作,因此不會沖突

1.2.3 數據線連接

題目告訴我們,數據為32位,但輸出LED矩陣位為16×16,所以說,該數據線應該有16位

每個16K×32b 的 ROM 的內部各自存儲 16K 個地址,每個地址里存放 4 個字節數據。地址范圍都一樣:0x0000~0x3FFF

4 個 4K×32b 的 ROM,地址范圍分別是也都一樣:0x000~0xFFF,每個共有 4K個地址,現在需要把 16K×32b 的 ROM 中的數據按照順序 每 4K 個為一組分為四組,分別放到 4 個 4K×32b 的 ROM 中去。HZK16_1 .txt 中的 1~4096 個數據放到 0 號 4K 的 ROM 中,4097~ 8192 個數據放到 1 號 4K 的 ROM 中,8193~12288 個數據放到 2 號 4K 的 ROM 中,12289~16384 個數據放到 3 號 4K 的 ROM 中

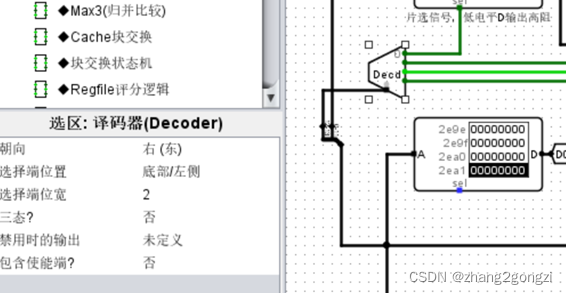

1.2.4 片選信號連接

在運行時,還需要對于片選信號線進行連接,將鼠標放置在上面,會得到相應的記錄,如得到信號是1,不工作。對于連接片選信號線,可以選擇譯碼器或是多路選擇器,我選擇的是譯碼器,連接原理為:將整個存儲系統地址線的高位用于譯碼器的輸入端,而譯碼器的輸出端用于連接四個芯片各自合適的片選信號線。

在頁面中增加一個譯碼器,數據位寬改為2,對于連發,需要進行討論,對應的16K數據放置芯片位置,需要對應其譯碼器的連接

1.3實驗步驟

1.理解題目,按照實驗要求對四個4×32位的芯片進行字括展,使其成為16K×32位的芯片

2.了解數據線,地址線,片選信號的連接方式,然后進行連接

3.地址線通過分線器來進行分離,其中還需要對其中的數據進行調整,分為高2位和低14位,高位為1,低位為0

4.之后對于片選信號進行連接,加入譯碼器,其中譯碼器位寬為2,可選為00,01,10,11四個信號

5.進行編譯測評,改正錯誤

1.4故障與調試

1.4.1 LED燈展示不正確

故障現象:LED無法正確明亮與熄滅

原因分析:結果檢查,線條的連接沒有問題,應該是只讀存儲器中,存儲的數據存在問題,

解決方案:四個4K×32位的ROM當中,數據并不是平分的,并且對于不同的連接方式,前4k的數據需要放在不同的芯片當中

1.5測試與分析

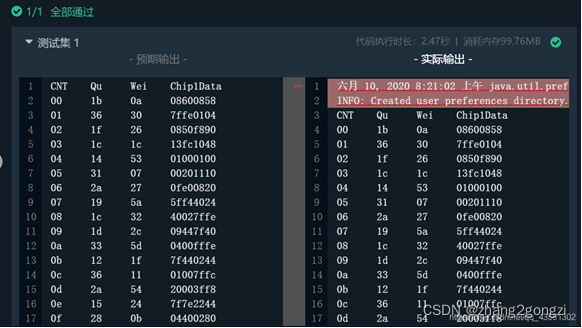

自行測試與頭歌網測試皆正確

1.6最終電路圖

MIPS寄存器文件設計

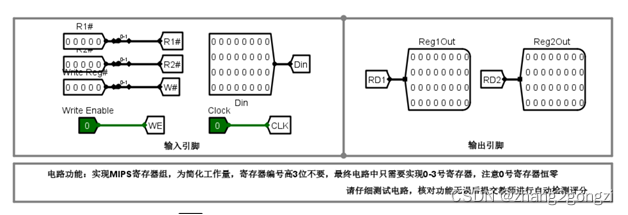

2.1設計要求

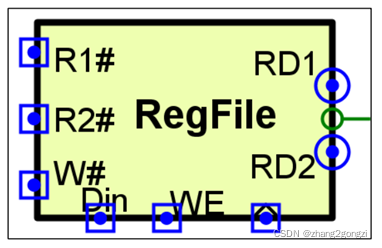

利用 Logisim平臺構建一個簡化的MIPS寄存器文件,內部包含 4個 32 位寄存器。通過 R1#、R2#給定兩個寄存器的地址編號,就可以從右側的 R1、R2 引腳 讀讀出對應寄存器的值。輸入引腳還包括寫入寄存器的編號 W#,數據寫入引腳 Din,當寫使能信號 WE 有效,時鐘的配合下將數據總線上的數據通過 Din 端寫入寄存器文件內部對 應的寄存器中具體引腳為下圖所示

2.2設計原理

2.2.1 封裝

首先需要看寄存器文件的封裝,由輸入引腳(R1,R2,W#,Din,WE,CLK時鐘信號)

2.2.2 讀控制電路設計

R1,R2分別為讀寄存器的編號,我們寄存器設計好之后,一次可以讀入兩個寄存器里面的值,那么指定哪兩個寄存器里面的值輸出呢,那就需要我們通過R1#,R2#這兩個信號,給出寄存器的編碼,然后RD1,RD2分別是寄存器一二的數據輸出引腳,它工作原理為,如果對寄存器文件進行讀的話,可以讀出寄存器中的值,寄存器由R1#,R2#的編號來指定是那兩個寄存器,值由RD1,RD2進行輸出。

由指令執行過程中,需要讀兩個寄存器的值,把他們送到目的寄存器中,所讀寄存器的編號,由電路設計決定,為源寄存器中的編碼決定的,由RD1,RD2進行輸出。

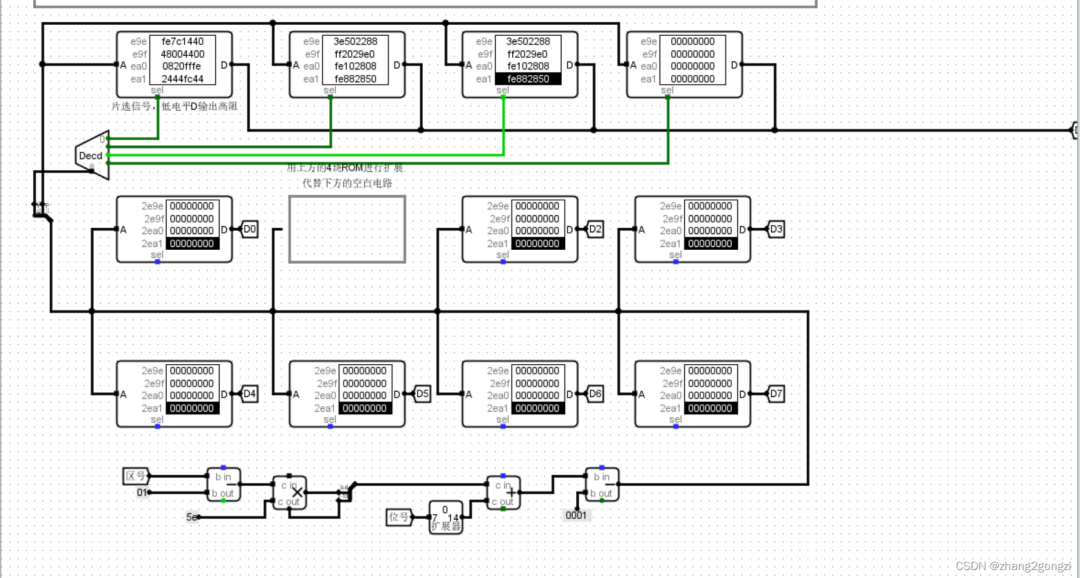

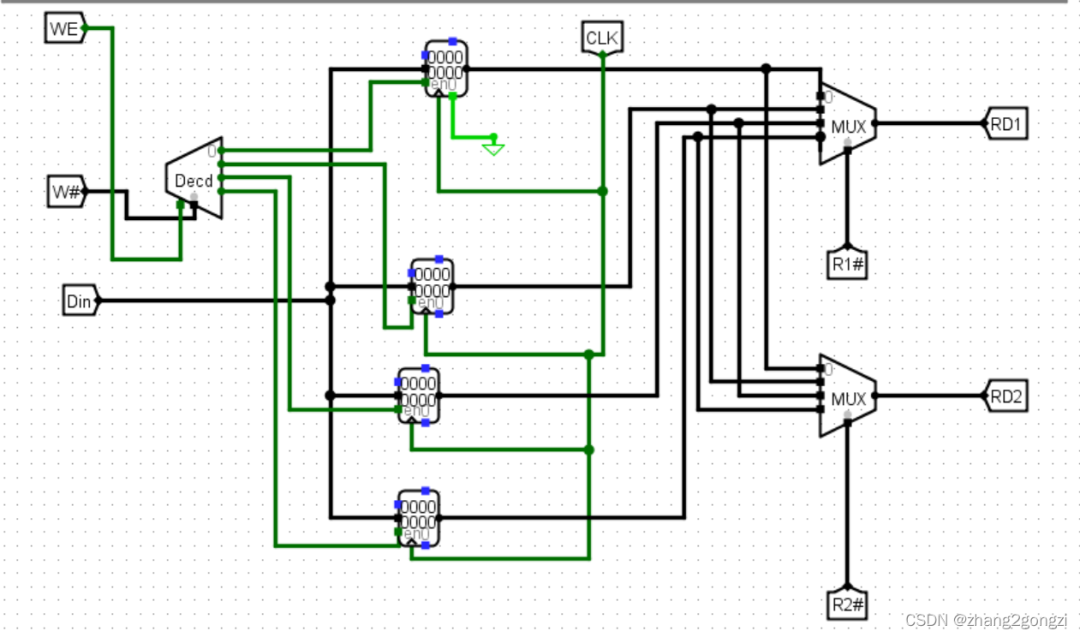

數據輸出可以根據 R1#、R2#的編碼控制多路選擇器進行選擇輸出。也可以采用譯碼器+三態門進行輸出控制。由于這里需要同時讀出兩個寄存器,所以相關邏輯必須有兩份。

2.2.3 寫控制電路設計

W#這個輸入引腳,是寫寄存器的時候用,寫寄存器時,要求WE,W#信號有效,然后數據從Din輸入引腳寫入數據,Din為32位,所有寄存器皆為32位。WE為寫使能信號,數據必須由W#指定寫入哪個寄存器,同時,WE有效,在時鐘脈沖下,將Din端數據寫到寄存器文件(由W#指定)中。

在指令執行時,通過分線器,將相應位提取出來,相應位代表著最終指令執行之后,想寫入的目的寄存器的編號,數據送到Din端,然后RegWrite也就是寫使能信號有效后,由CLK信號,把指定寄存器的數據,寫入。

寫入時根據 W#收到的寫入寄存器編號,利用譯碼器或多路選擇器選擇具體 寄存器(寫信號 WE 和譯碼信號同時有效時,令寄存器的使能端 en=1)

2.3實驗步驟

(1)理解題目,按照實驗要求進行電路連接

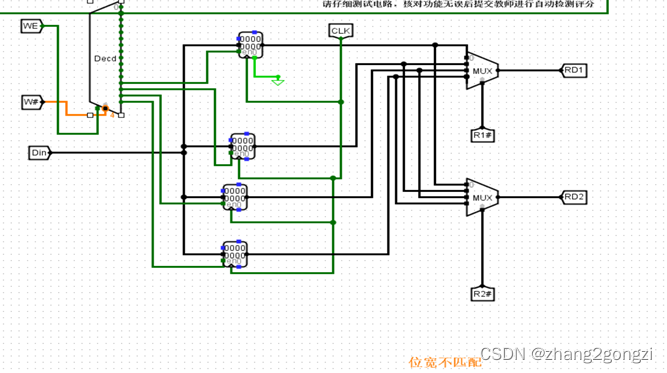

(2)W#為兩位,可能值為00,01,10,11。當值不同時,選擇不同寄存器,所以加入譯碼器,通過W#輸出信號,由輸出信號進行選擇

(3)寫信號還需要別的信號有效,才具備寫入條件,如何控制寫入寄存器,將WE和譯碼信號的值送入使能端,=1時,可以寫入

(4)查看寄存器片選信號,如為1有效,為0無效

(5)同步置1和清零可不連,可以將電源連到地線,一直無效

(6)寫入數據要把數據輸出引腳連在對應寄存器輸入引腳

(7)選擇與門,并更改與門位寬,W#需要譯碼器,改為兩位,W#連到譯碼器輸入端,然后譯碼器四個輸出引腳,WE是1時,W#如果也是1,與門相連

(8)按要求連接,進行測試

2.4故障與調試

2.4.1 位寬不匹配

故障現象:LED無法正確明亮與熄滅

原因分析:題目只給出四個寄存器,所以只需要兩個位寬就足夠

解決方案:將位寬改為2

2.5測試與分析

自行測試與頭歌網測試皆正確

2.6最終電路圖

審核編輯:湯梓紅

-

寄存器

+關注

關注

31文章

5253瀏覽量

119205 -

計算機

+關注

關注

19文章

7174瀏覽量

87157 -

mips

+關注

關注

1文章

237瀏覽量

47581 -

存儲系統

+關注

關注

2文章

396瀏覽量

40788 -

存儲芯片

+關注

關注

11文章

874瀏覽量

42873

原文標題:【實踐】頭歌計算機組成原理存儲系統設計實驗報告(字庫存儲芯片,MIPS寄存器文件設計)

文章出處:【微信號:feifeijiehaha,微信公眾號:電路和微電子考研】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

頭歌計算機組成原理存儲系統設計實驗報告(字庫存儲芯片,MIPS寄存器文件設計)

頭歌計算機組成原理存儲系統設計實驗報告(字庫存儲芯片,MIPS寄存器文件設計)

評論