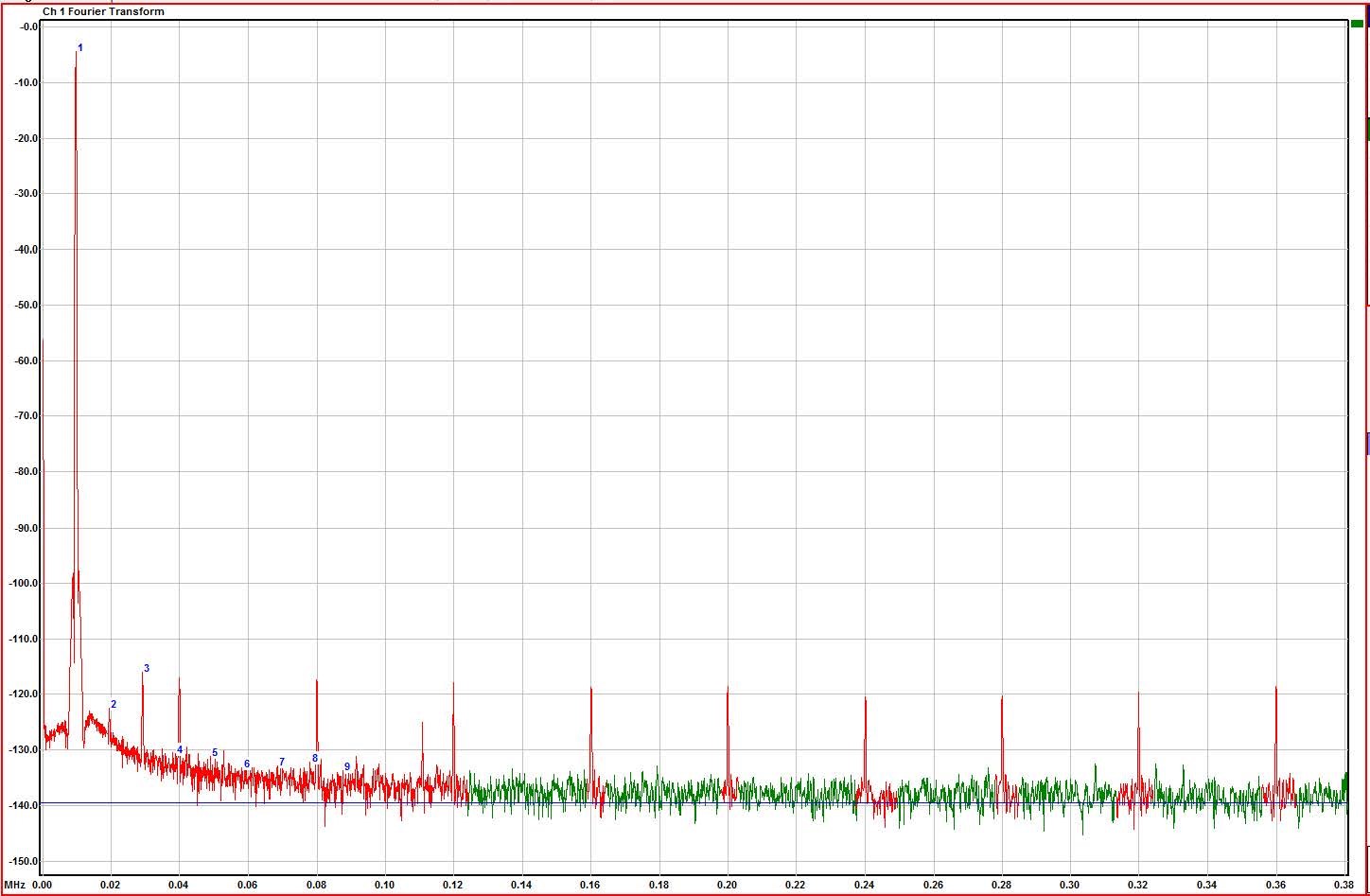

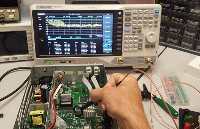

在第 1 部分中,我們設計并測試了一種低通 + 下采樣結構,該結構將 LTC2387-18 高速逐次逼近寄存器 SAR) ADC 的 DC2290A-A d 增強電路的頻譜分辨率從每箱 114Hz 提高到 0.596Hz。每個垃圾箱的平均噪音水平也降低了近12dB。

濾波器被實現為128字移位寄存器和加法器。隨后,下采樣器使用了FPGA中74%的可用邏輯門。這種方法允許用戶根據需要對不同的抽頭進行加權,但代價是復雜性。如果不需要對抽頭進行加權,例如添加時間窗口,那么有一種方法可以大大減少每個樣品的添加次數。

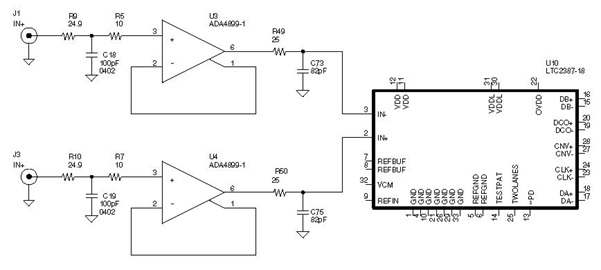

以下是指LTC2387-18,但適用于LTC2387系列(LTC2386和LTC2385)的所有成員以及DC2290A演示電路的其他變體,唯一的區別是采樣速率和位數。

更簡單的方法

實現此濾波器的一種更簡單的方法是一次加載一個樣本的 N 抽頭寄存器,然后形成所有抽頭的總和一次。當每個新樣本到達時,它被添加到總數中,最早的抽頭將從總數中減去。通過這種方式,我們避免了每次樣品進入移位寄存器時對所有抽頭求和。下面是 N = 128 的示例。

首先,FPGA對18位數據字進行反序列化。

該詞與運行頻率為15MHz的時鐘一起傳遞到模塊boxcar_128。

wire [17:0] dout, dout_f;

boxcar_128 box (

.clk(cic_clk),

.din(dout),

.dout(dout_f)

);

第一個變量是時鐘;此時鐘的上升沿出現在轉換的反序列化數據可用之后。接下來的兩個變量是 18 位數據字,第一個是濾波器輸入,第二個是輸出。下面是模塊本身的代碼。

module boxcar_128 (

clk,

din,

dout

);

input clk;

input din;

output dout;

wire [17:0] din;

reg [17:0] dout;

reg [2321:0] shift_reg;

reg [24:0] sum_reg;

initial

begin

shift_reg = 0;

sum_reg = 0;

end

//load the shift register & update sum

always @ (posedge clk)

begin

shift_reg = shift_reg << 18;

shift_reg[17:0] = din;

sum_reg = sum_reg + {{7{shift_reg[17]}},shift_reg[17:0]} - {{7{shift_reg[2321]}},shift_reg[2321:2304]};

end

//scale the output to 18 bits

always @ (negedge clk)

dout = {{7{sum_reg[24]}},sum_reg[24:7]};

終端模塊

模塊的核心仍然是shift_reg;這是一個可容納 128 x 18 位字的移位寄存器。就像在第一個版本中一樣,這些單詞是數據輸入 din,一個接一個地加載到移位寄存器中。在每個時鐘上升沿,最新的數據字被加載到寄存器中,而最舊的數據字被丟棄。寄存器中128個位置的總和是濾波器的輸出。然后將此輸出按比例縮小 7 位以適合 18 位字,并作為 dout 傳遞回主模塊。此時,這些樣本的頻譜只是ADC輸出的低通濾波副本。再次注意,在這種情況下,每個樣本只有一個加法和一個減法。在本博客的第 1 部分中,每個樣本執行了 128 次添加,這大大增加了所需的邏輯單元數量。

下一步是縮減采樣,這是通過將每 128 個過濾器樣本傳遞到數據收集板來完成的。

結果比較

這種結構產生的噪聲水平和分辨率與第1部分更復雜的規范實現相同,但僅使用FPGA中可用邏輯元件的3%。它要簡單得多,因為每個樣本時刻只執行一個加法和一個減法。此處描述的代碼的Verilog和編程文件都可以在右側面板上找到。

65K 點 FFT,9.76KHz 音調,每箱噪聲為 –151.3dBFS

-

FPGA

+關注

關注

1626文章

21667瀏覽量

601856 -

寄存器

+關注

關注

31文章

5317瀏覽量

120008 -

SAR

+關注

關注

3文章

414瀏覽量

45898

發布評論請先 登錄

相關推薦

高分辨率16位DS ADC LTC2439CGN-1

請問AD5522的分辨率如何提高?

影響頻譜分析儀頻率分辨率的因素

提高LTC2387-18在高速成像和儀器儀表應用中的光譜分辨率

LTC2387-18正弦信號驅動器的設計要求

LT6201/LTC6655 Demo Circuit - Single-Ended to Differential Amplifier for LTC2387-18

提高LTC2387-18演示板的頻譜分辨率

提高LTC2387-18演示板的頻譜分辨率

評論