數據傳輸是基于地址進行的。在分析和設計微架構時,除了地址域之外,如何選擇地址信號,我覺得也是值得注意的問題。

地址邊界

還記得剛開始工作時,被安排維護AXI總線重排序的公共模塊,當時有一個地址對齊的概念,如64Byte地址邊界、128Byte或者256Byte地址邊界,那會花了有一段時間才搞清楚,但也僅僅是搞清楚,也不清楚引入這一概念的原因,能解決哪些問題。

所謂地址邊界,若某地址能夠被一整數除凈,該地址就稱為整數對應的地址邊界。在系統內都是以0/1的二進制,這一整數一般指的是2的冪次方,如4、8、16、64、128等等。舉例來說,0x200, 0x240, 0x880等等都是64Byte地址邊界;0x200,0x880是128Byte地址邊界,但0x240不是128Byte地址邊界。再談談CacheLine的概念。為提升系統訪問內存的速度,通常會引入緩存Cache,也就是將Memory的內容先搬運到CPU附近。這一緩存是以塊為單位的,需要訪問時,則先將對應的緩存塊搬運到Cache內。這一緩存塊就稱為CacheLine,是緩存Cahe管理的最小單位,可基于系統需求選擇大小,如64Byte或128Byte,甚至是4KByte。每個CacheLine,除了存儲其本身的數據之外,還需要記錄其地址、是否修改等等額外信息。粒度越小,記錄額外信息的資源占比越大;粒度大了,又會對數據的利用率下降;具體大小則需基于需求來確定,如對于AI/GPU計算,可考慮使用4KByte的Caheline。

地址對齊

在考慮微架構設計和軟硬件接口時,訪問Memory盡可能按照整塊地址的訪問,地址邊界對齊,尤其是寫操作。在一般的CPU計算機系統,采用的地址邊界大小至少為64Byte,使用更大的區間,如128Byte/256Byt,在一些場景也是能夠帶來收益的。

數據總線利用率

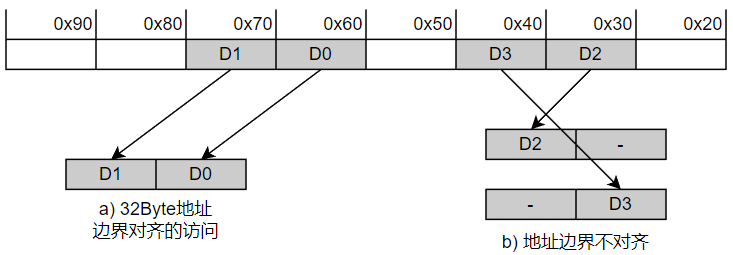

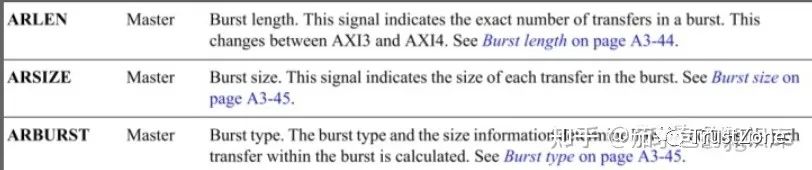

系統互聯總線的位寬較大,如128、256、512bit,甚至2048bit。但是,每一拍數據的地址并不是隨機,而必須基于一定規則排列,參考AXI協議,如256bits的數據位寬,其地址低位必須是0-31。傳輸32Byte數據,若起始地址為32Byte邊界對齊,1拍可以傳輸完成,利用率為100%,否則需要占用2拍,其利用率只有50%。

對于PCIe數據傳輸來說,其數據長度單位為DW,即4Byte,因此由于地址邊界不對齊帶來的影響比較小。

Full/Partial Write

系統存在CacheLine的定義,若訪問操作為整CacheLine的寫操作,則稱為Full Write,否則為Partial Write。舉例,CacheLine為64Byte,若訪問地址低6位為0,長度為64Byte,就是Full Write;低6位不為0,或長度不為64Byte整數倍,則存在Partial操作。非地址對齊的訪問操作,容易造成Partial Write,引入性能問題。

Read-modify-write

對于Cache、DDR,或者其余類似的Memory系統,存在最小操作粒度的概念。若寫訪問操作小于該最小操作粒度,則需要引入Read-modify-write。將對應地址的數據塊讀取出來,進行修改,再將數據寫入對應地址,需要占用讀通道的帶寬。對于地址對齊的整塊訪問,直接寫入即可。

DMA的地址選擇

Host與PCIe Device之間大量數據的傳輸,基本都是由DMA(Direct Memory Access)完成的。簡單來說,DMA就是從一個地址(源地址)讀取連續的數據,再寫入到另一個地址(目的地址)。硬件邏輯提供源地址、目的地址和搬運長度的軟件編程接口,再被軟件進行調用。復雜一些的硬件實現,還可以支持描述符、鏈表、搬運方式配置和其余系統屬性的配置等等特性,如支持完成中斷。

至于對數據搬運的地址選擇,則是由調用DMA的軟件進行控制的,但是也會受到上下游模塊的約束,如Device側的硬件引擎模塊等等。

在考慮DMA數據流時,需基于系統層面對各模塊的數據訪問需求進行設計,盡可能使得DMA在Host和Device之間的數據搬運是地址邊界對齊的。這一對齊包含兩個方面,一是訪問Device/Host的讀寫訪問是基于地址邊界對齊,二是源地址和目的地址的低位是相等的。兩者其實是類似的,沒有滿足后者,也會引入大量的非地址對齊的操作。至于后者的地址低位,則需基于硬件實現進行考慮,考慮點就是上面描述的幾點要素。

再來看看第二方面引入的邏輯復雜度,源地址和目的地址的低位相等。考慮源和目的方向使用了AMBA總線,數據位寬為512bit/64Byte,若需支持地址不對齊的場景,則需要512個64bit位寬的MUX;若僅需支持地址的低6bit相等,則完全不需要進行移位處理;若僅需支持地址的低2bit性能,硬件邏輯規模也減小為512個16bit位寬的MUX。大量的MUX邏輯也容易引入Congestion風險,需要做額外的優化處理。

結語

地址對齊的概念非常簡單,但容易被忽略。對于軟件人員來說,DMA就是應該支持任意地址到任意地址的數據搬運;但對硬件設計來說,可能需要付出很大的代價才能達成要求。可以考慮做一些折衷,軟件做一些簡單修改,使用地址對齊的數據搬運,硬件實現側對地址對齊的操作進行盡量的優化,而對非地址對齊的做一些簡化處理,不考慮性能但滿足功能,達到較優的PPA。

-

數據傳輸

+關注

關注

9文章

1838瀏覽量

64476 -

地址

+關注

關注

1文章

31瀏覽量

10748 -

微架構

+關注

關注

0文章

22瀏覽量

7033

發布評論請先 登錄

相關推薦

如何實現局部數組的地址對齊?

【工程源碼】NIOS II 自定義IP核的靜態地址對齊和動態地址對齊

探討一下地址邊界與地址對齊的概念及其選擇

IP地址,IP地址是什么意思

ATM地址,ATM地址是什么意思

基于ARM程序的字節對齊的分析

mac地址和ip地址是什么決定的

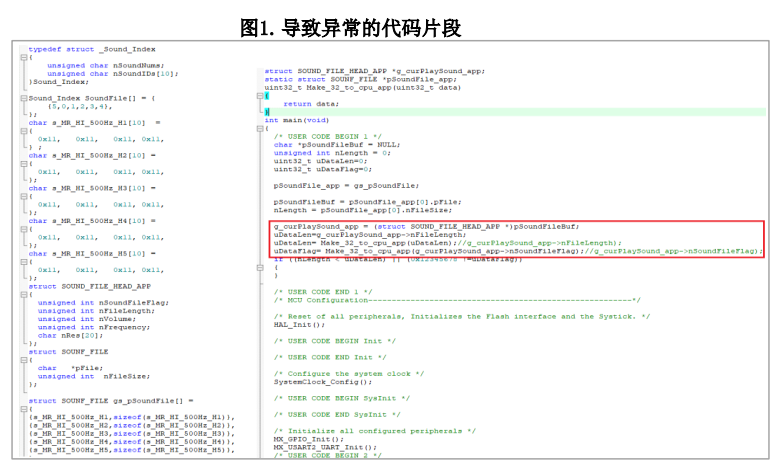

一個跟地址對齊有關的應用異常案例

IP地址是什么,IP地址的分類有哪些

工程師筆記|一個地址未對齊引起的 HardFault 異常

AXI總線:讀寫地址結構

地址邊界與地址對齊

地址邊界與地址對齊

評論