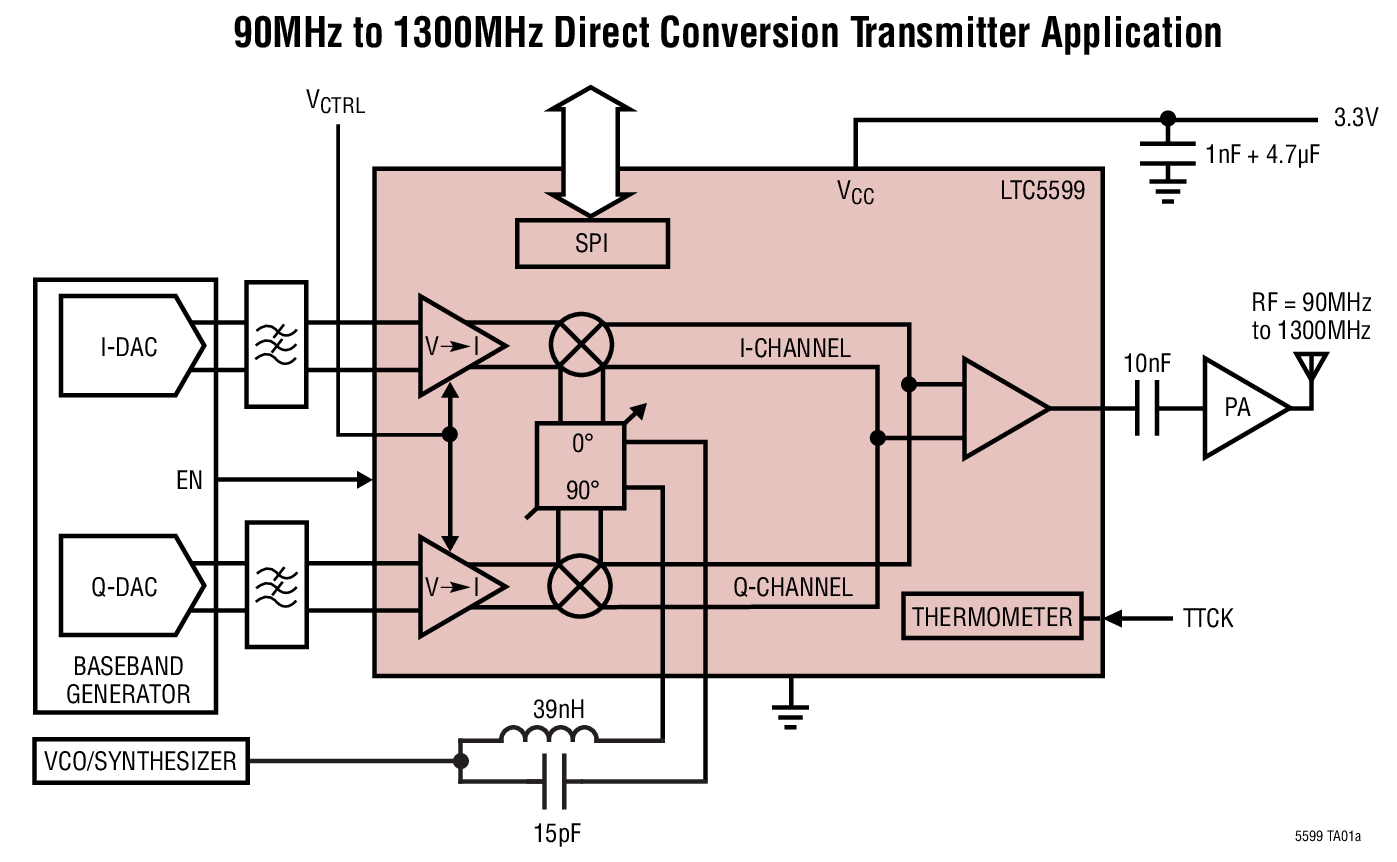

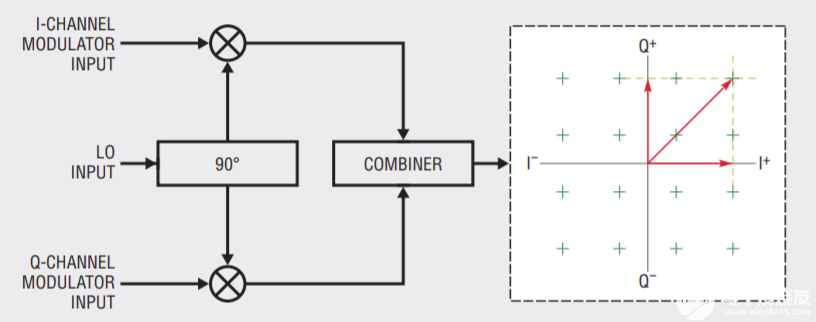

為了產生復雜的調制,需要兩個相同的通道(I和Q)。為簡單起見,此處僅顯示一個通道。

調制參數

在此示例設計中,系統規格如下:

符號速率 = 30 ksps

數字濾波器 alpha= 0.35

下一步是確定基帶濾波器要求:

總信號帶寬 = 30*1.35= 40.5 kHz,即每個 I 和 Q 通道為 20.25 kHz。這決定了濾波器通帶。

濾波器阻帶要求主要由DAC更新速率決定,在本例中為240 ksps,或每個符號8倍插值。

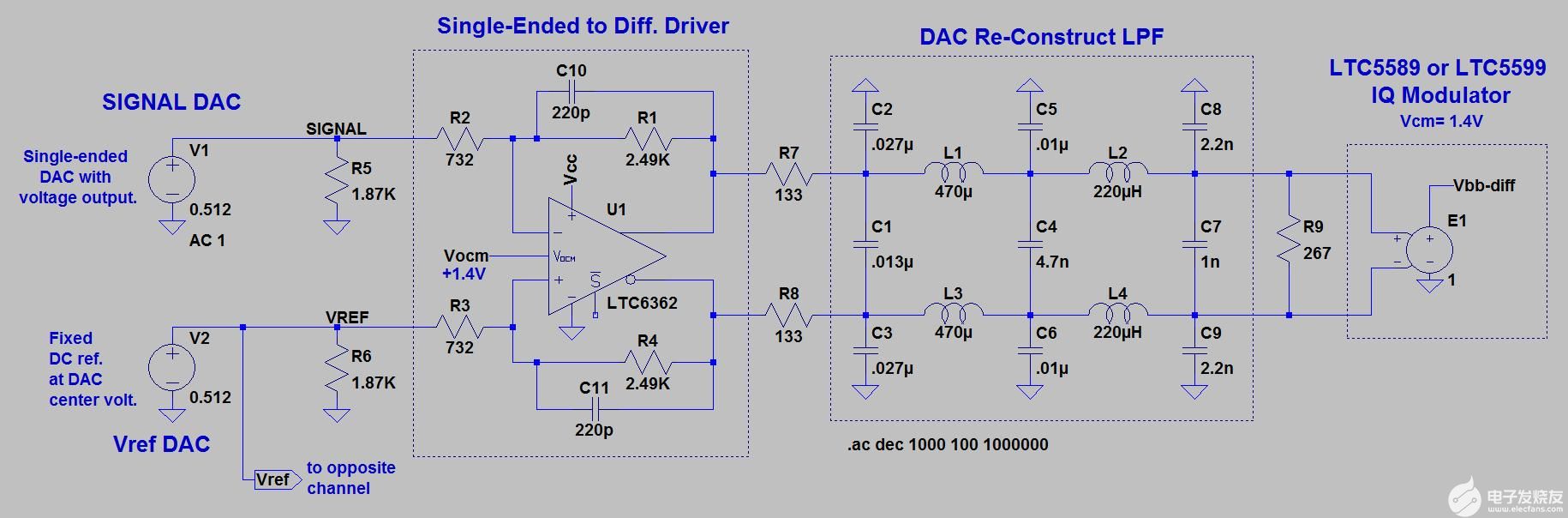

現在讓我們快進到完整的電路,然后是描述。請注意,為簡單起見,僅顯示兩個相同的I&Q通道之一:

圖1.基帶驅動電路將單端DAC轉換為差分。建議使用無源DAC重構濾波器以實現低噪聲。

DAC 輸入和參考

首選差分DAC輸出。但是,當使用單電源、單端DAC輸出時,則需要固定的Vref,該Vref可能來自第3個DAC或V。裁判的信號 DAC。Vref只是DAC的零基準電壓源,可以在I和Q通道之間共享,但要確保它是低源阻抗,以實現I和Q通道之間的最小串擾。緩沖液 V裁判必要時采用一個 LTC6246 電壓跟隨器。

在本例中,單端I和Q DAC配置為0至+1.024V輸出。請注意,DAC數字驅動器應縮放以使用所有可用的DAC位,但切勿觸及滿量程極限。

可選電阻R5和R6用于DAC的低平均直流電流。在本例中,輸入共模電壓被下拉至0.512V,以匹配DAC輸出電壓范圍的中心。

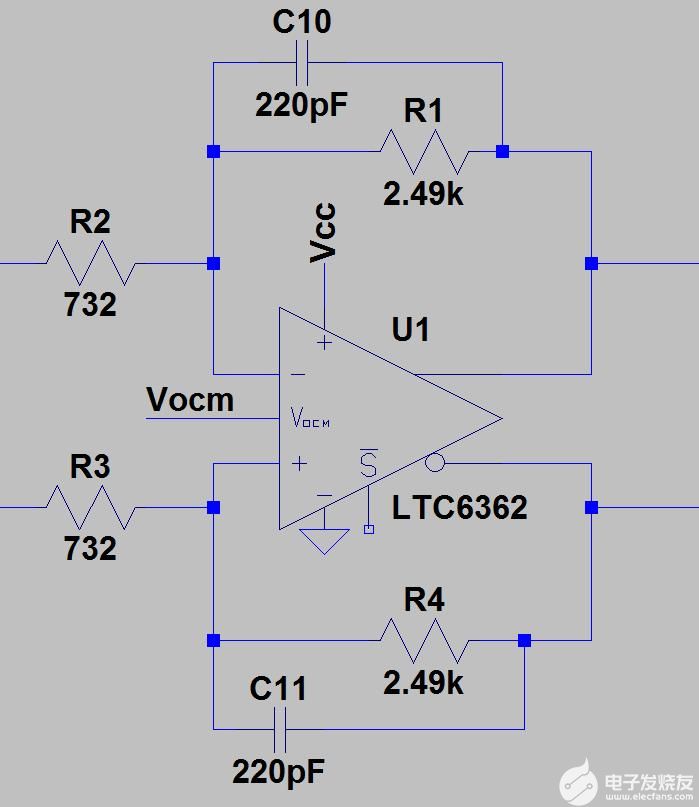

單端至差分驅動器

與單端基帶驅動相反,使用差分基帶信號驅動調制器是非常優選的。差分驅動提供高 6dB 的射頻輸出功率和最低的誤差矢量幅度 (EVM)。

選擇具有差分輸入和輸出的放大器還可以簡化設計,因為

設計對稱性降低了輸出直流失調誤差,從而減少了LO饋通(LOFT)并提高了調制精度。

輸出共模電壓(VOCM) 可以獨立更改以滿足調制器的要求,并且

增益可以獨立改變,而不影響VOCM.

圖2.差分驅動器通過提供增益和輸出共模電壓的獨立調整來簡化設計。

選擇LTC6362用于此應用,是因為它僅吸收1mA的電源電流,而且噪聲相當低。對于基帶信號源具有低近端噪聲密度的設計,低放大器噪聲非常重要,這意味著使用非常高階基帶數字濾波器以及高分辨率DAC。我們不希望放大器使這種接近信噪比變得更糟。

選擇電容C10和C11來降低HF噪聲,同時在最高基帶頻率下提供可忽略不計(<0.1 dB)幅度誤差貢獻。LTspice仿真對于此目的非常有用。

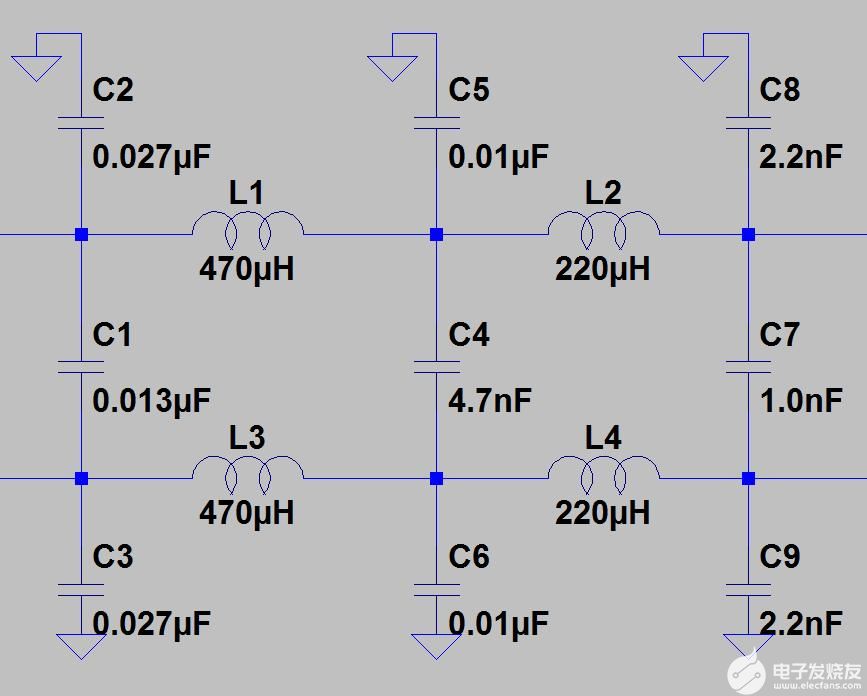

DAC LC 重構濾波器

DAC重建濾波器對于平滑DAC階梯輸出非常重要,它減少了高頻奈奎斯特鏡像。另一個重要功能是將調制器輸出端的寬帶本底噪聲降至最低。

圖3.LC重建濾波器。此設計適用于 266 歐姆源極和負載端接。

使用經典的濾波器設計CAD工具為您的設計合成這些LC元件值。為獲得最佳調制精度,請選擇貝塞爾LPF響應作為線性相位。在本例中,-3dB轉折放置在50 kHz,這適用于高達~30 ksps的符號速率。

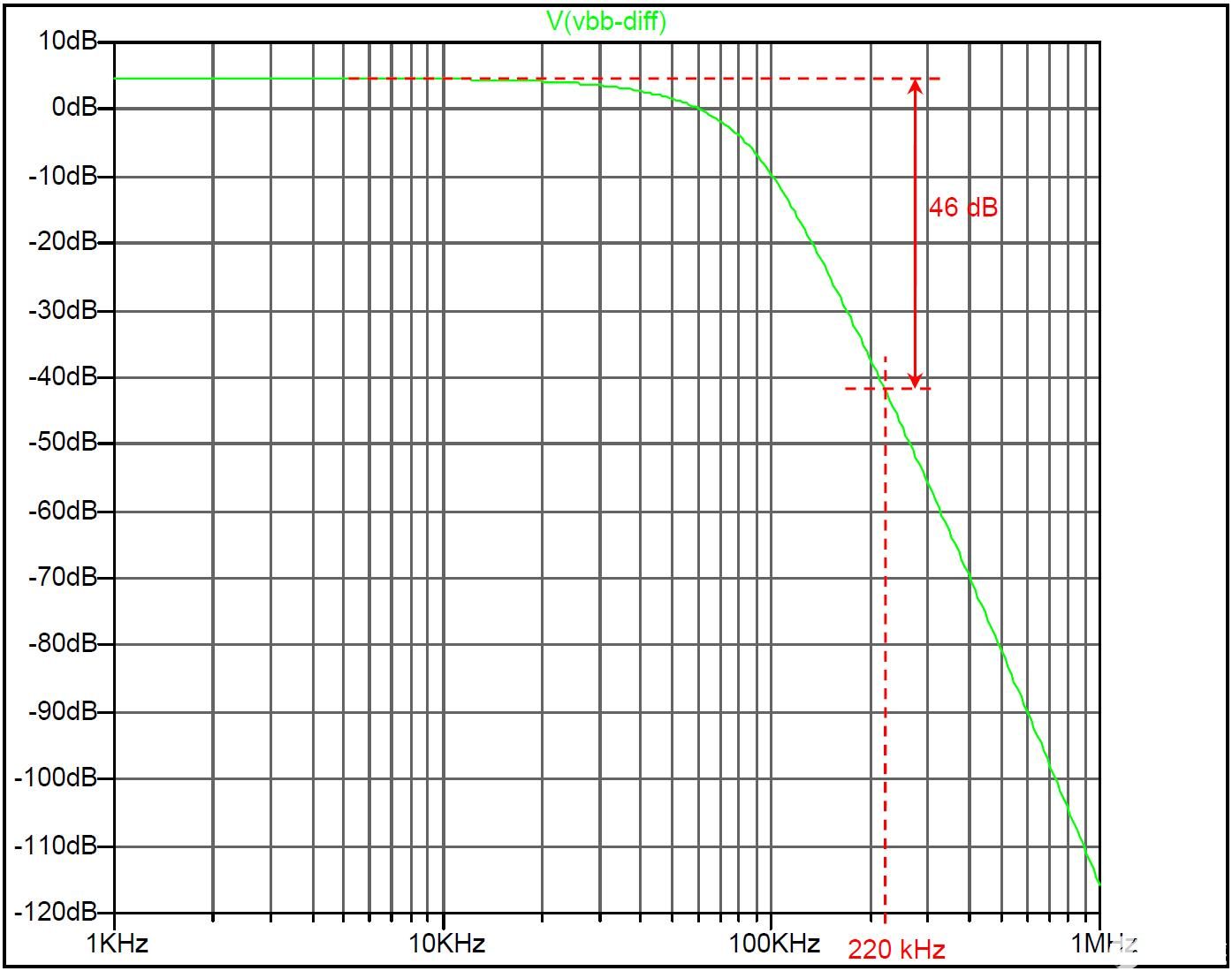

DAC鏡像雜散相對于所需信號的幅度可以通過SIN(x)/x估計,其中x = π f / f時鐘,對于此設計的頻率計劃,我們可以預期在220 kHz時具有25dB的圖像衰減。再加上DAC LC重建濾波器在220 kHz(45dB)處提供的衰減,以估計70dB的總奈奎斯特鏡像抑制。

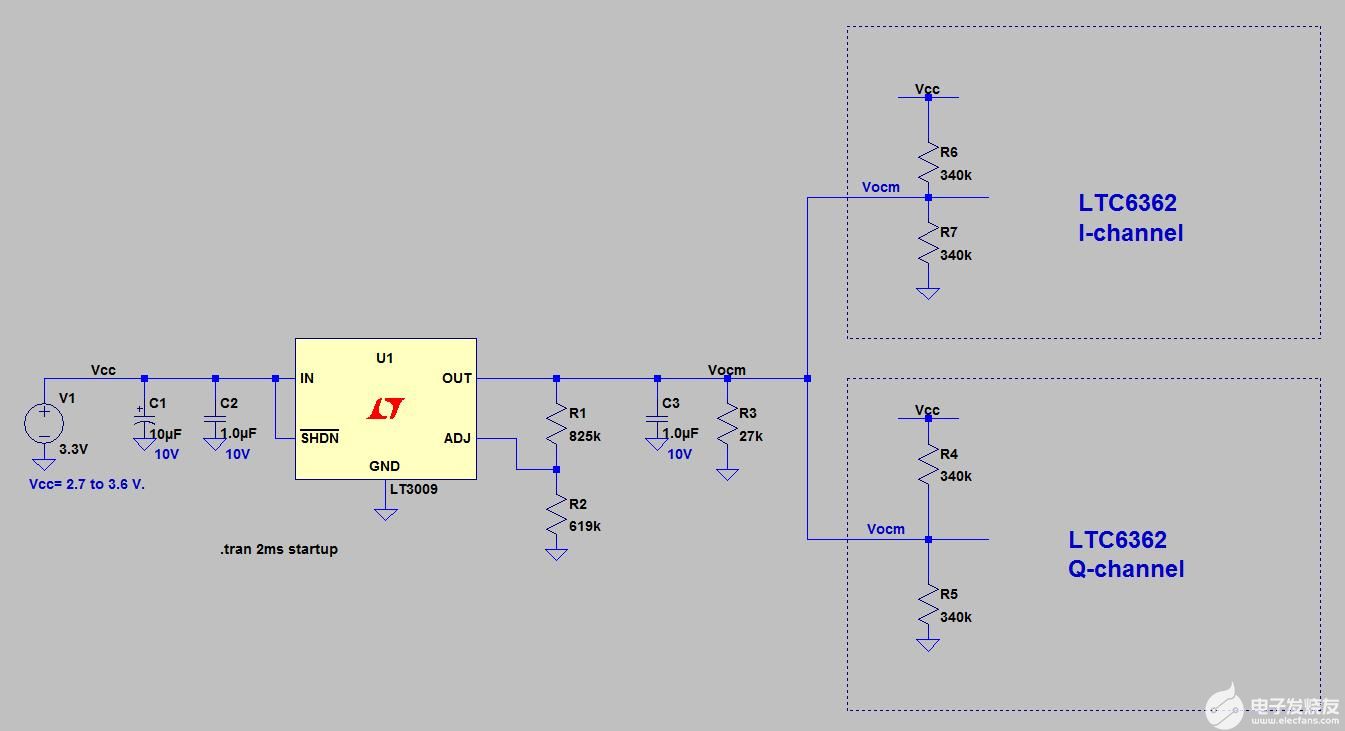

推導 VOCM源

當 V抄送監管良好,VOCM可以從簡單的Vcc電阻分壓器獲得。否則,VOCM由一個可調電壓穩壓器高效衍生而來,該穩壓器支持低至 1μA 的電阻分壓器電流。 適當的 VOCM電壓對于建立正確的IQ調制器工作點至關重要。

圖4.簡單的 LT3009 提供了調節良好的低噪聲 Vocm,同時將電流浪費降至最低。

請注意,LTC6362 具有一個內部 VOCMV 時的分壓器抄送/2,因此每當 Vcc 超過 2.8V 時,VOCM需要一些下拉才能保持在1.4V。這就是 R3 的目的。

增益縮放

通常,對于許多 LTC5589 和 LTC5599 應用,差分驅動電平約為 330mV有效值是一個很好的起點,在IQ調制器的I和Q輸入端進行差分測量。由于LC濾波器損耗,LC濾波器輸入端的驅動電壓通常略高,約為358mV有效值在每個差分放大器輸出端。應使用頻譜分析儀來確認是否達到了所需的調制器RF輸出頻譜純度。

以更高的V驅動IQ調制器有效值用于更高的輸出功率或更低的 V有效值用于降低 IMD 和提高調制精度。放大器反饋電阻可以為此目的進行調整。

仿真結果

濾波器合成應該已經正確。然而,由于濾波器設計必須從單端轉換為差分,因此存在一些設計誤差的蔓延空間。另一個誤差來源可能是放大器的延遲,這成為更高符號速率的一個因素。快速的LTspice仿真有助于驗證這兩個誤差源是否保持良性。

首先分別查看通帶和阻帶響應:

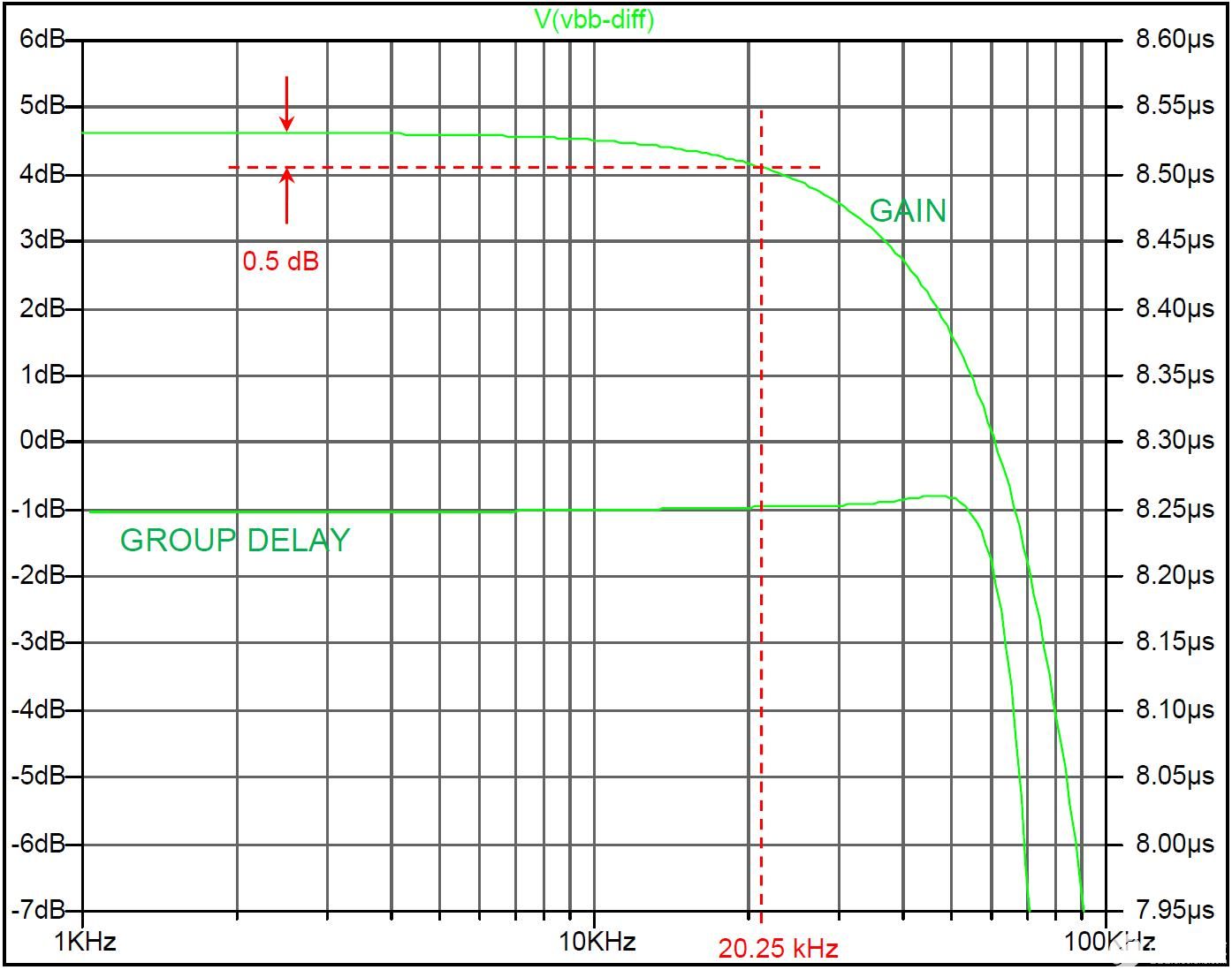

圖5.整體電路通帶響應。在這里,我們尋找最高信號頻率(本設計示例中為20.25 kHz)下的最小增益滾降和群延遲變化。

請注意,在20.25 kHz的最高信號頻率下,響應下降僅為0.5dB。低于1dB是一個很好的目標。群延遲非常平坦,您需要增量標記才能在上面的仿真圖上測量它。它只有3.7ns,與1/30k或33.3us的符號周期相比,可以忽略不計。少于符號周期的百分之幾是一個很好的目標。在這種情況下,群延遲變化非常好,這要歸功于貝塞爾濾波器。

圖6.整體電路阻帶響應。在這里,我們正在尋找奈奎斯特圖像頻率(本設計示例中為220kHz)下的足夠衰減。

在本例中,我們看到鏡像頻率處的衰減為46dB。結合 25dB sin(x) / x,即 71 dB。這里一個好的目標是大約 70dB 或更好。對于無線應用,監管機構的要求在這里發揮作用。

請注意,濾芯損耗可能不那么容易準確模擬。它們的效果將在下一個主題中很明顯:

測試結果

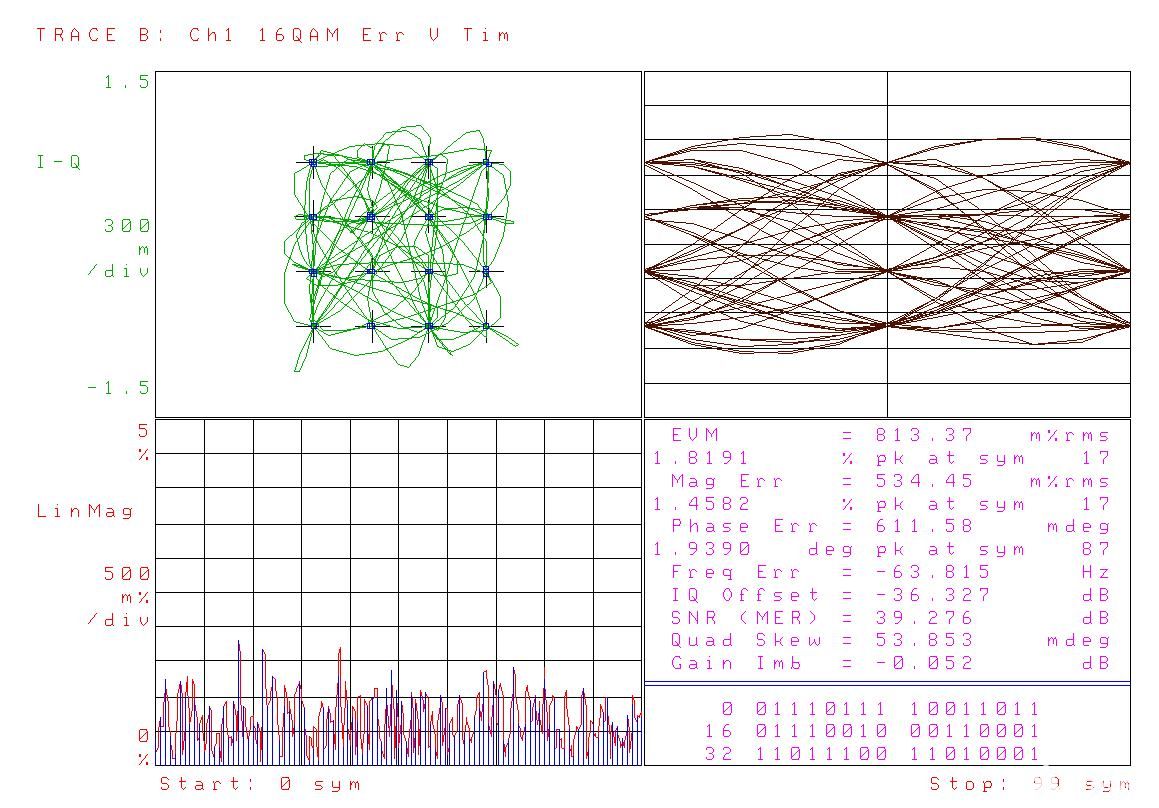

對于數字調制,調制器精度的最終測試是EVM。

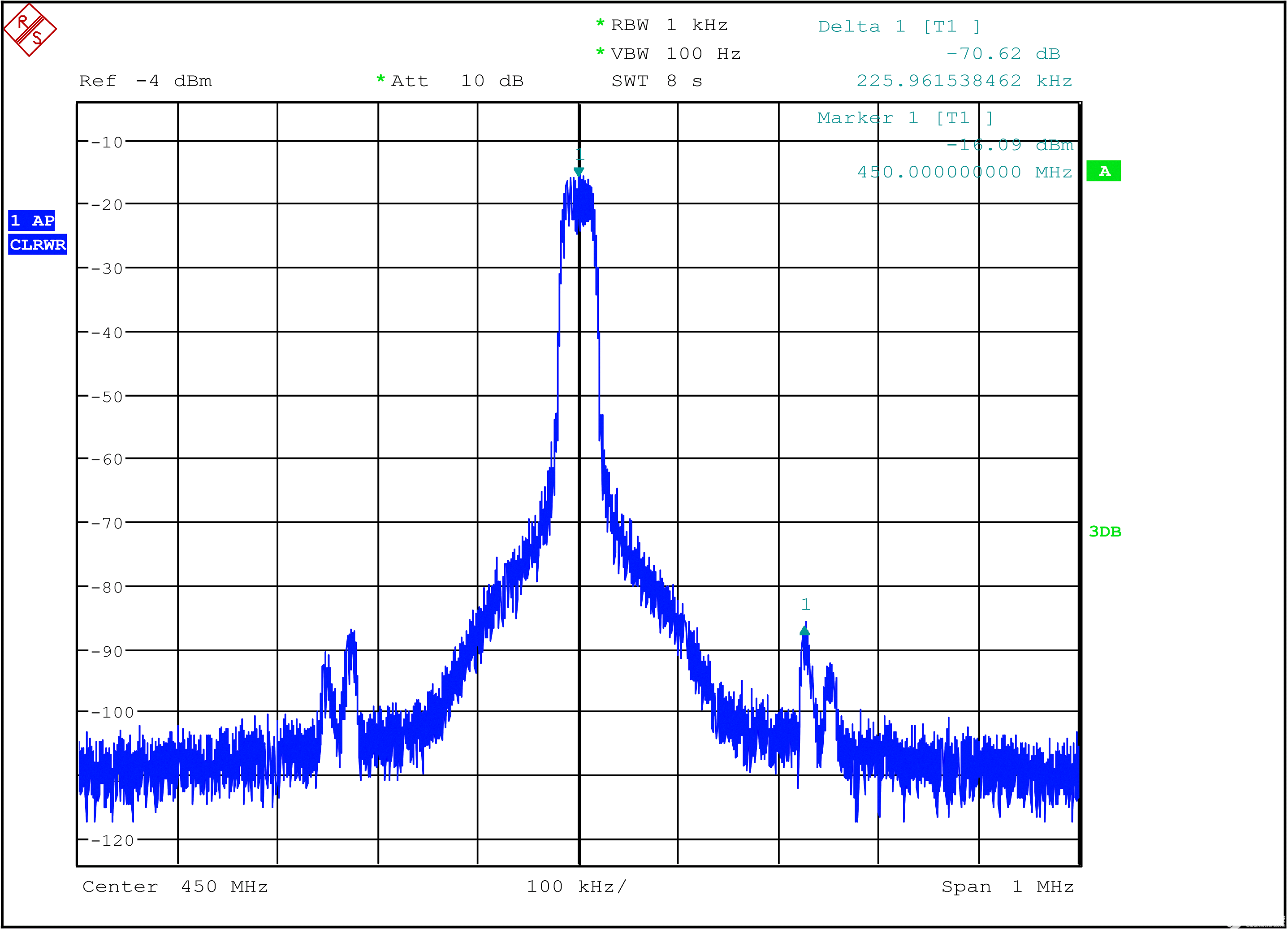

圖7.LTC5599 0.8% rms 的 EVM 測量值符合預期。除設置為450MHz的LO頻率外,所有SPI寄存器均采用默認值。

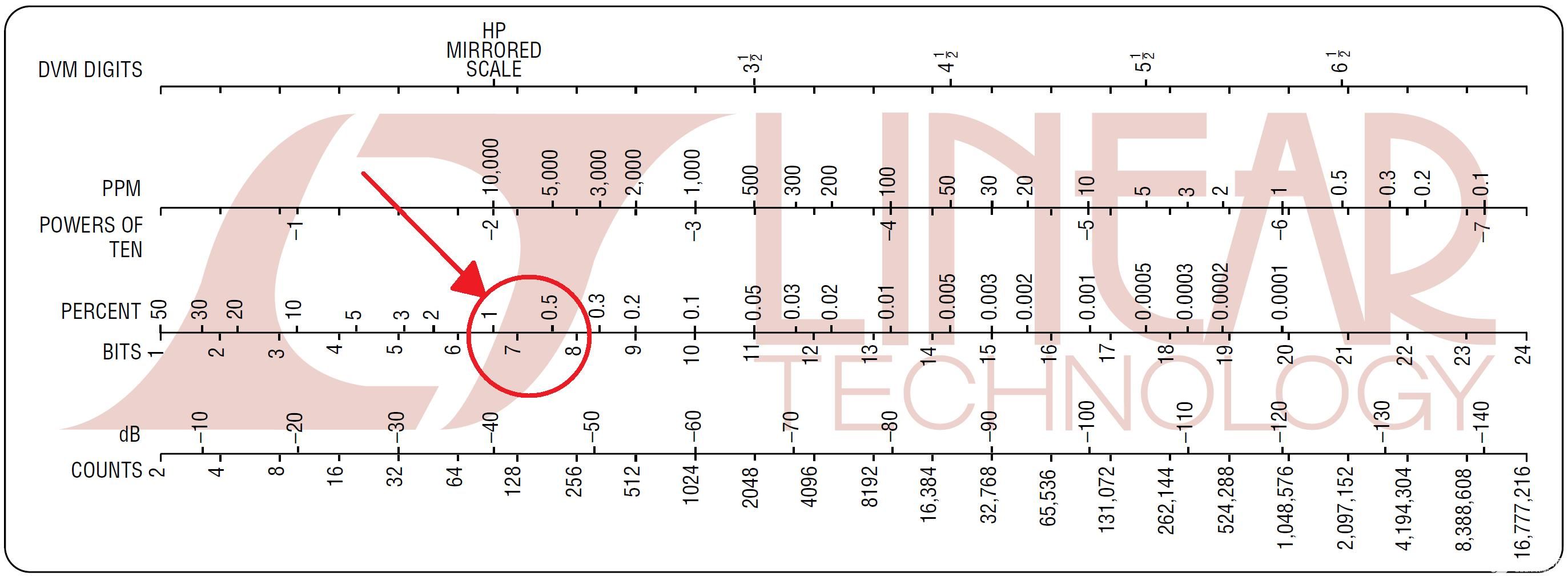

考慮到該系統使用的是 8 位 DAC,EVM 的測量值約為 0.8% 也就不足為奇了,因為考慮到 ENOB 將小于 8 位,從根本上說,這是可實現的最佳目標:

圖8.索取免費的線性技術精度轉換器!本例顯示了有效的DAC分辨率如何限制調制精度。

EVM 測試結果與之前公布的測量結果一致,對于大多數數字調制應用來說絕對足夠好。

進一步的EVM改進需要更多的FIR濾波器抽頭,更高分辨率的DAC,也許還需要一些數字濾波器補償,用于sin(x)/x滾降和DAC重建濾波器滾降。

圖9.-4dBm 輸出功率時的射頻輸出頻譜。請注意,最差的DAC鏡像約為-70dBc,足以滿足大多數應用的需求。

從輸出頻譜來看,近端噪聲頻譜密度由幾個因素決定:FIR濾波器階數、LO相位噪聲和調制器驅動電平。

結論

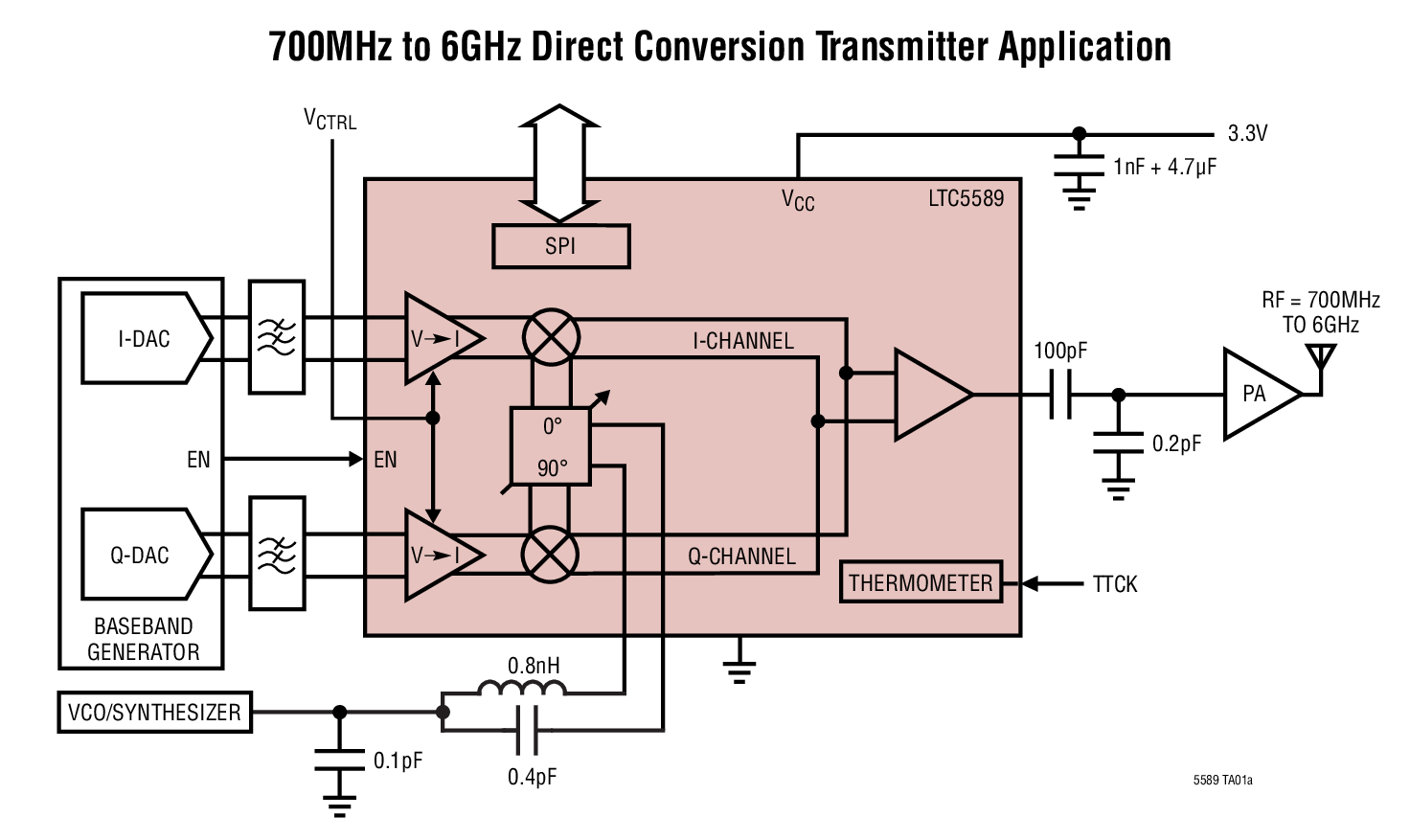

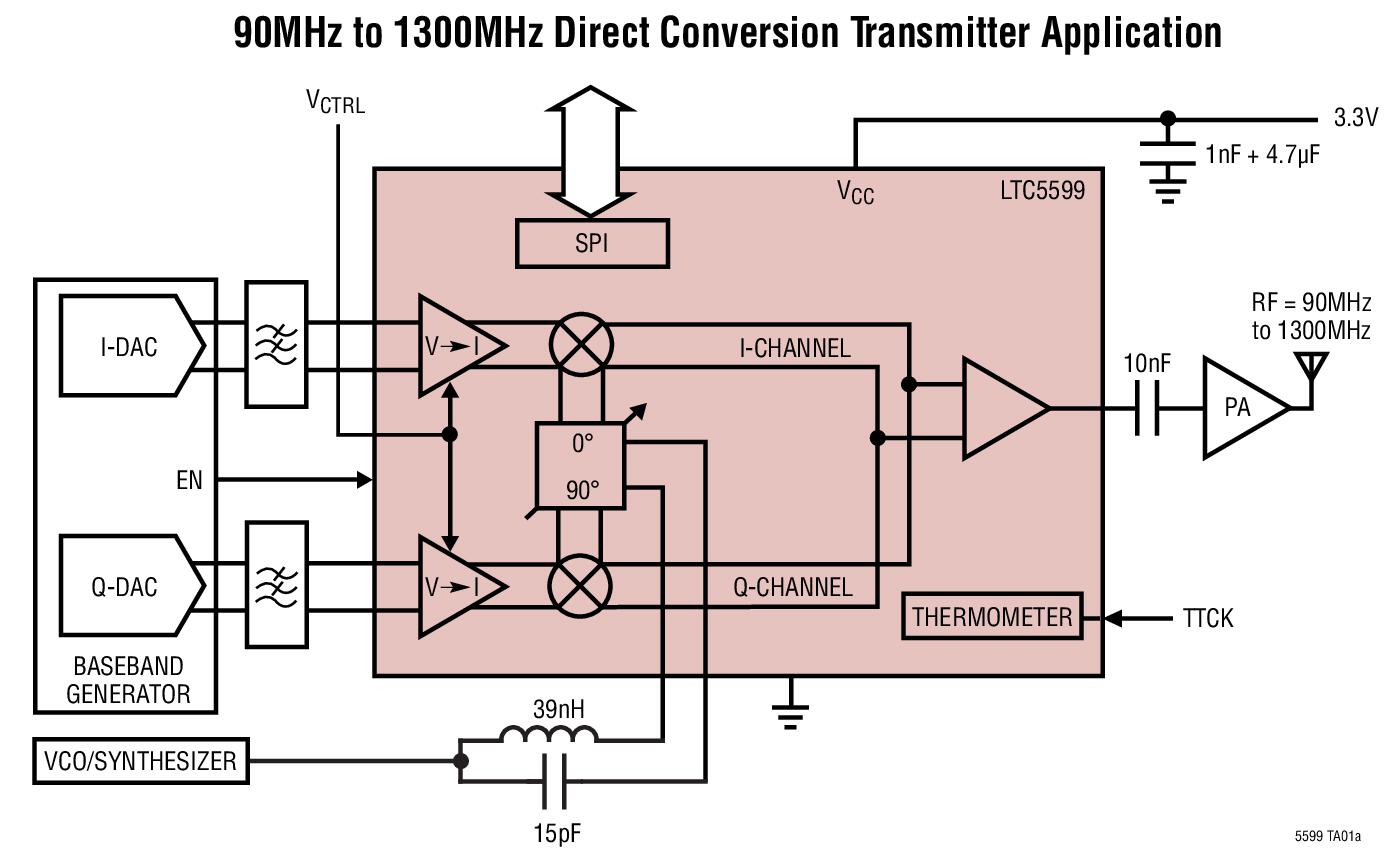

本博客闡述了利用低功率 IQ 調制器(如 LTC5599 和 LTC5589)的詳細設計技術。為實現最高調制精度、最低噪聲和最低直流功耗,設計人員必須仔細考慮每個電路模塊,如本文所示。

審核編輯:郭婷

-

濾波器

+關注

關注

160文章

7727瀏覽量

177670 -

dac

+關注

關注

43文章

2269瀏覽量

190833 -

調制器

+關注

關注

3文章

832瀏覽量

45106

發布評論請先 登錄

相關推薦

6GHz 低功率直接轉換 I/Q 調制器

一款非常低功率的高性能 I/Q 調制器

LTC5599:具有邊帶抑制和載波泄漏抑制性能

LTC5599 30MHz 至 1300MHz 低功率直接正交調制器

LTC5589 700MHz 至 6GHz 低功率直接正交調制器

LTC6362/LTC5599 Demo Circuit - Low-Power I/Q Modulator Driver (Baseband Design)

基于LTC5599_Typical Application調制器的參考設計

LTC5589/LTC5599低功率IQ調制器的基帶設計示例

LTC5589/LTC5599低功率IQ調制器的基帶設計示例

評論