作者:Altug Oz and Kazim Peker

從通信基礎設施到儀器儀表的各種應用中,對更高系統帶寬和分辨率的要求推動了以陣列形式連接多個數據轉換器的需求。設計人員必須找到低噪聲和高精度解決方案,以使用通用JESD204B串行數據轉換器接口對大量數據轉換器進行時鐘和同步。

包含抖動衰減功能、內部VCO以及大量輸出和許多同步管理功能的時鐘發生器件現已上市,以解決這一系統問題。然而,在許多實際應用中,數據轉換器陣列中所需的時鐘數量超過了從單個IC元件獲得的可行數量。設計人員經常求助于將多個時鐘生成和時鐘分配組件連接在一起,從而創建一個廣泛的時鐘樹。

本文提供了一個真實的案例研究,說明如何構建靈活且可重新編程的時鐘擴展網絡,該網絡不僅保持出色的相位噪聲/抖動性能,而且還通過確定性控制將所需的同步信息從時鐘樹的第一個器件傳遞到最后一個器件。

介紹

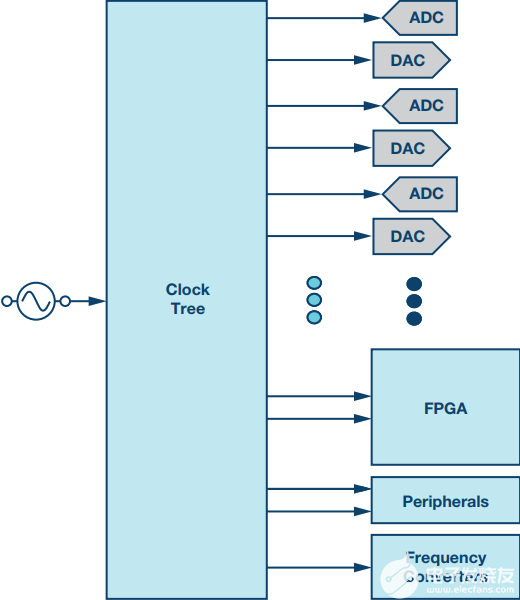

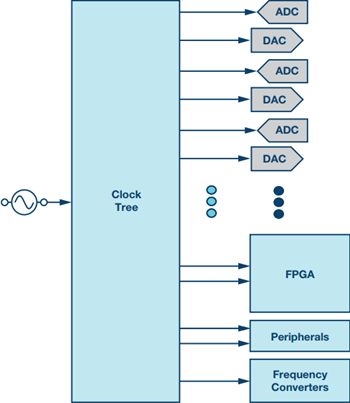

無線通信系統從3G到4G和LTE(以及5G,目前正在規范討論中)的演進一直是高速數據轉換和同步的關鍵技術驅動因素。推高蜂窩基站所需數據帶寬的因素多種多樣。主要因素是訂戶數量的增長,對更豐富的多媒體內容的需求以及使用全球蜂窩基礎設施的機器對機器通信的新應用。因此,設計人員正在尋找新的創新RF收發器架構,這些架構具有更高的通道數,采用有源天線設計、大規模MIMO和高級波束成形等技術。具有大量輸入和輸出的系統利用多條傳輸路徑,需要大量的ADC和DAC元件。考慮到數據轉換要求的規模,采樣時鐘生成和同步成為重大的設計挑戰。在復雜系統中,所需的時鐘信號數量很容易從幾個增加到數百個,如圖1所示。

圖1.帶有時鐘樹的數據轉換器系統。

JESD204B標準定義了串行數據接口,用于減少寬帶數據轉換器和其他系統IC之間的數據輸入/輸出數量。數據I/O量的減少解決了高速、高位數數據轉換器互連的問題。提供具有更少互連的寬帶數據轉換器的能力簡化了PCB布局,并允許在不影響整體系統性能的情況下實現更小的外形尺寸。這些改進對于解決大多數應用的系統尺寸和成本限制非常重要,包括無線基礎設施、便攜式儀器、軍事應用和醫療超聲設備。

系統級注意事項

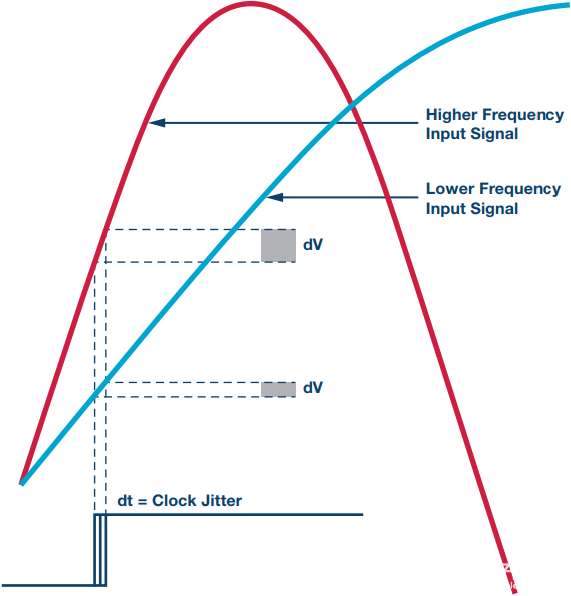

在具有大型數據轉換器陣列的復雜系統中,要處理的數據量不斷增加,需要從天線到處理單元的高SNR(信噪比)鏈路。從時鐘角度來看,SNR受采樣時鐘相位噪聲的限制。較差的相位噪聲性能可能會產生抖動并增加EVM(誤差矢量幅度)來降低系統性能,從而嚴重降低SNR。通常,時鐘信號質量以抖動為單位,抖動定義為相位噪聲在設定的目標帶寬上的積分。通常,相位噪聲積分限值為 10 kHz 至 10 MHz。然而,寬帶噪聲也很重要,因為高時鐘信號本底噪聲也會影響系統的SNR。較差的采樣時鐘也可能具有雜散信號成分,這會降低SFDR(無雜散動態范圍)。最后,在考慮占空比和上升/下降時間等參數時,采樣時鐘質量不僅應在頻域中定義,還應在時域中定義。

這些是采樣時鐘的基本系統要求。然而,在大型數據轉換器陣列中,當不同陣列的時鐘之間需要同步時,通道間偏斜成為關鍵要求。此類系統的性能依賴于同步的數據陣列,因此對不同數據轉換器之間的偏差很敏感。

功耗是另一個考慮因素。更高的功耗會降低系統效率,增加溫度和冷卻成本,并可能導致更高的故障率。從商業角度來看,元件數量和電路板空間也很重要,應該加以控制。

時鐘樹結構

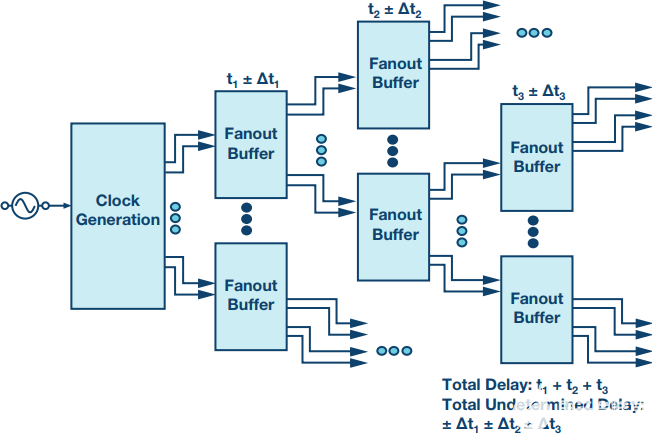

如前所述,在大規模系統中,單個時鐘IC可能沒有足夠的輸出來驅動所有分支。時鐘樹拓撲可以克服這個問題,并能夠同步多個部件、設備或多個系統。時鐘樹拓撲框圖如圖2所示。請注意,樹中的每個級別都引入了一個延遲組件,該組件由固定和未確定的部分組成。

圖2.時鐘樹框圖。

這些延遲可能會受到外部因素的影響,例如電壓和溫度變化以及特定于器件的工藝變化。這些不準確性加起來,導致ADC和DAC中可能出現無法忍受的時序變化,而ADC和DAC需要在高頻下同時計時。當今系統所需的高操作頻率決定了嚴格的設置和保持時間。雖然固定延遲可以通過額外的努力來補償,但無法在系統內補償不確定的延遲。因此,設計人員的目標是通過以某種方式控制未確定的延遲元素來最小化或消除它。

除了這些約束之外,樹結構應該是靈活的,以便能夠增加分支的數量并根據系統需要輕松控制它們。

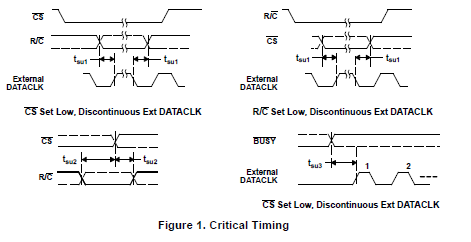

對齊時鐘和最小化通道偏斜的一個共同目標是確定性地執行此功能,即對所有器件和所有上電序列重復執行此功能。在JESD204B系統中,需要對本地多幀時鐘(LMFC)進行對齊以實現確定性延遲。該接口要求使用子類 1 (SYSREF) 或子類 2 (SYNC) 定義在發送和接收設備上重置和對齊 LMFC。整個系統中不確定的延遲使得LMFC的對齊更難在1個LFMC周期內實現。因此,前面提到的具有高精度對準的時鐘樹結構將有助于系統設計人員實現LMFC的對準。

此外,設計人員需要確保在每個數據轉換器輸入端,SYSREF信號相對于器件時鐘的建立和保持時間是可接受的。如果設計使用單個時鐘芯片,則滿足建立和保持時間是確保考慮適當時序裕量的簡單過程,而在基于簡單時鐘緩沖器的多器件時鐘樹結構中,控制建立和保持時間更具挑戰性。所提出的時鐘樹結構具有跨不同層的確定性同步,有助于滿足所有層之間所有SYSREF/設備時鐘對的建立/保持時序要求。這種時鐘樹結構可以滿足同步約束,并在不同層的每個數據轉換器上對高速器件時鐘進行相位對齊。

時鐘樹的設計

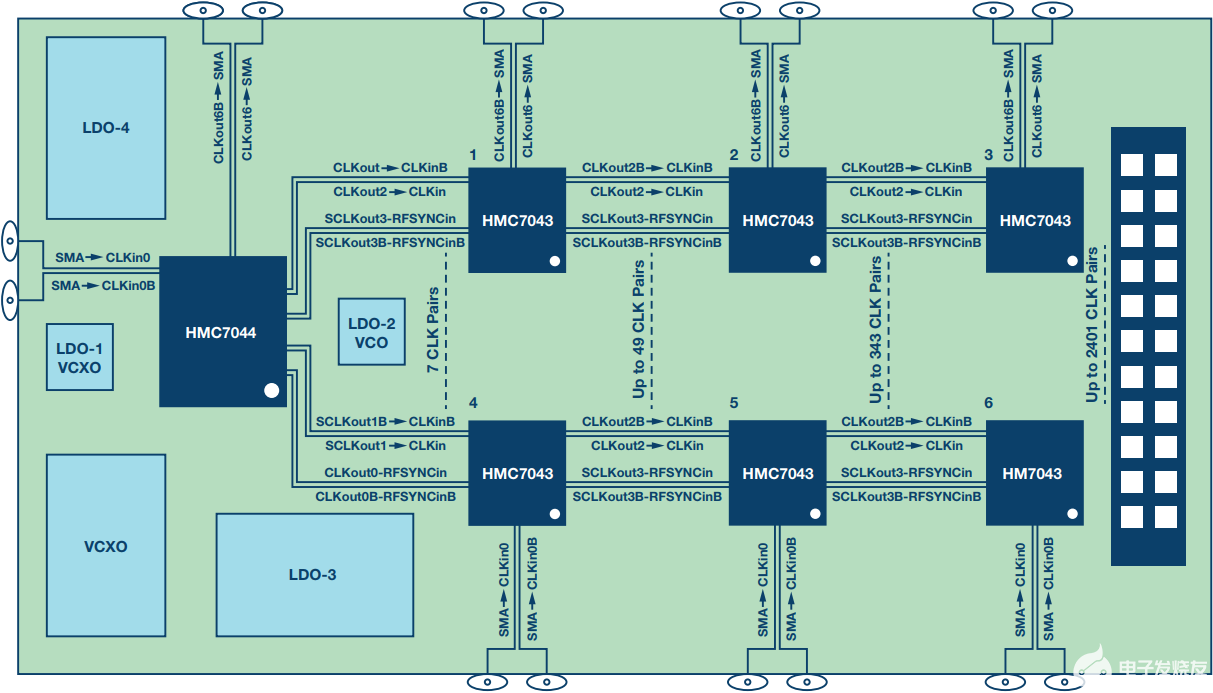

圖3顯示了一個四電平時鐘樹示例,其中使用一個主時鐘生成部分(HMC7044)和三級扇出緩沖器(HMC7043)為采樣板創建多個同步時鐘。

圖3.四級時鐘樹示例。

一個HMC7044用作時鐘樹的根;它是一款具有抖動衰減功能的14輸出時鐘發生器,支持JESD204B同步。HMC7043器件(14輸出扇出緩沖器)用于分支的每個級別。這些器件完全兼容,其編程功能非常相似,這使得匹配器件以及增加或減少時鐘分配水平變得非常容易,從而增加了系統的靈活性。

可以在時鐘樹的每一級的每個輸出之間完成同步。在該系統中,HMC7044的輸出可以通過SPI命令進行相位對齊,或者通過使用SYNC脈沖進行更精確的相位對齊。該命令將重置HMC7044的通用SYSREF定時器,該定時器控制所有時鐘的輸出分頻器。所有輸出時鐘分頻器同時由 SYSREF 定時器的命令對齊。從 SYNC 命令到 SYSREF 定時器的延遲以及開啟和關閉時間之間的延遲得到了很好的定義,這提供了輸出之間確定性延遲的同步。此外,任何輸出都可以編程以生成定義數量的脈沖,以用作系統中的SYSREF脈沖。

時鐘分配部分HMC7043還包括一個非常相似的SYSREF定時器結構。該器件利用射頻同步信號進行對準。RFSYNC脈沖將啟動與HMC7044的SYNC信號相同的過程,所有輸出將以高精度同步。同樣,輸出可以設置為脈沖模式,用作SYSREF脈沖。

所提出的時鐘樹結構基本上使用SYSREF信號作為下一級HMC7043的RFSYNC信號,并在每級的輸出端保持相位對齊。通過精心的架構設計,所有這些時序信號都是確定性的,提供嚴格的偏斜控制。此外,每個器件都包括一個模擬延遲結構,因此輸出之間的任何偏斜差或任何線路長度不等式都可以在源頭上得到補償。

對于RF系統中使用的復雜數據轉換器陣列,由于ADC、DAC、FPGA、本振和混頻器可以以不同的頻率計時,因此可能需要不同的頻率。HMC7044和HMC7043均具有內置分頻器,可生成多個頻率。此外,HMC7044具有雙PLL結構和集成VCO,無需額外元件即可生成高頻時鐘。

常見通信系統的另一個復雜性是,大多數RF前端單元依賴于傳輸/接收模塊的串行接口,這要求數據和時鐘由數字處理器或FPGA嵌入/解嵌。此過程通常會產生不需要的參考時鐘抖動,并要求大型RF時鐘生成和分配器件(如HMC7044)中包含抖動衰減能力。

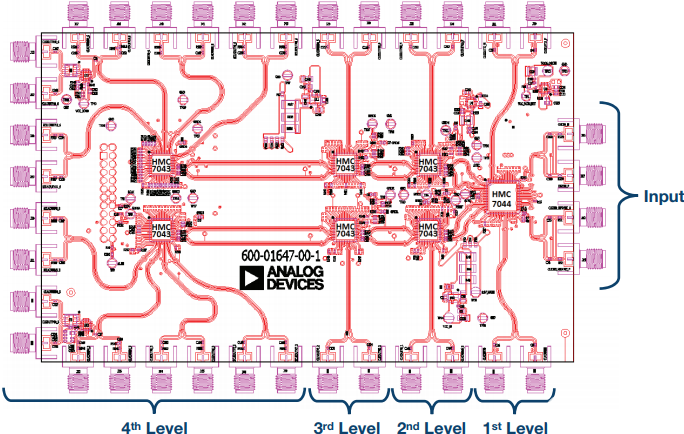

可用于數據轉換器陣列的緊湊型解決方案如圖4所示。

圖4.四電平時鐘樹的緊湊型解決方案。

測試結果

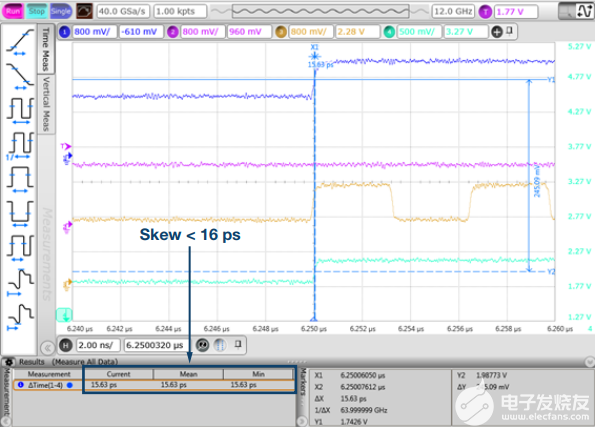

圖5顯示了所有輸出之間的偏斜。黃色和青色線信號是脈沖 SYSREF 和連續時鐘信號,用于 4千電平輸出,無需額外的延遲調整即可同步。藍線信號是來自HMC7044的連續SYSREF信號,通過使用模擬延遲功能,它與4千電平輸出。在本例中,獲得的總偏斜小于 16 ps。

圖5.四電平輸出的時域響應。

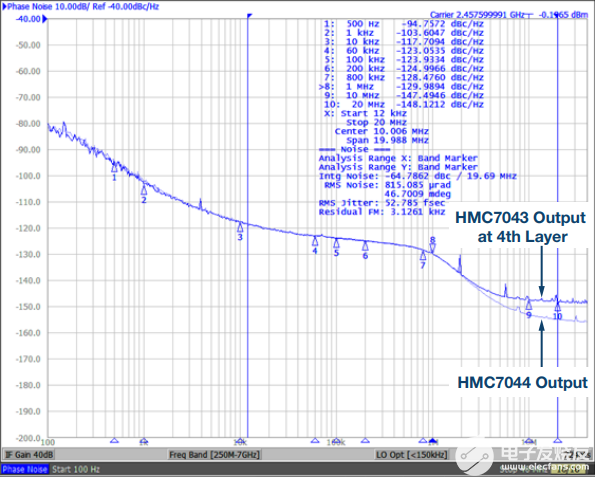

四電平時鐘樹的相位噪聲性能如圖6所示。時鐘發生器的相位噪聲也用淺藍色線表示。總相位噪聲在高達2 MHz的偏移下不會下降。考慮到每個電平的加性噪聲(附加抖動),本底噪聲的下降是不可避免的,在圖中可以觀察到本節噪聲增加6 dB的情況。HMC7044和HMC7043具有相同的輸出本底噪聲(約–154 dBc/Hz),所有四個器件的噪聲均降至–148 dBc/Hz,對于大多數系統來說,這仍然是可接受的水平。

圖6.四電平輸出的頻域響應。

2457.6 MHz時12 kHz至20 MHz的積分噪聲計算得出的抖動均方根為52.7 fs,相對于HMC7044的輸出而言,僅降低了幾fs rms。在幾乎所有實際系統中,這種性能下降是可以容忍的,但是,如果不能容忍,則最后一級可以用HMC7044代替HMC7043,從而衰減時鐘樹本身的任何累積抖動。

如前所述,在使用大量數據轉換器的系統中,功耗成為最關鍵的問題之一。影響這種時鐘樹功耗的一個關鍵因素是所使用的信令類型。HMC7044和HMC7043的輸出信號模式可以通過彼此獨立的軟件控制來改變,從而可以在功耗和驅動強度與頻率之間進行權衡。一般準則是,在低頻下,LVDS可以以低功耗使用,而在高頻下,LVPECL和CML可提供最佳性能。

結論

本文中的討論適用于許多不同的系統,這些系統利用分布式大型數據轉換器陣列,從無線基礎設施到軍用雷達,再到測試和測量系統。最近的5G通信系統中提出的更高頻率和更高帶寬的調制方案建立在多個RF輸入/輸出接口的當前趨勢之上,這需要增加數據轉換路徑的數量。此外,在最近的一些5G架構提案中,相控陣天線被廣泛討論為節省功耗和增加輸出容量的一種手段。

相控陣技術廣泛應用于軍事通信系統,不僅需要大量的時鐘,而且還需要這些時鐘的精確同步。

大型數據轉換器陣列的另一個重要用例是測試和測量系統,其中需要以高采樣率捕獲大量數據,盡可能減少噪聲,并同時進行處理。這些系統還需要大量的同步時鐘。同樣,對于先進的醫學成像系統,數據處理吞吐量很高,并且需要并行數據采集路徑的同步操作。

審核編輯:郭婷

-

轉換器

+關注

關注

27文章

8639瀏覽量

146892 -

天線

+關注

關注

68文章

3184瀏覽量

140712 -

adc

+關注

關注

98文章

6452瀏覽量

544144

發布評論請先 登錄

相關推薦

兩個轉換器同步方法和整合多個轉換器

RF采樣:全新的采樣速率數據轉換器

12位250kSPS串行CMOS采樣模數轉換器ADS8508的詳細資料概述

采用同步數據轉換器陣列如何構建時鐘擴展網絡

AN-1221: 使用ADF4002 PLL產生高速模數轉換器所需的極低抖動編碼(采樣)時鐘

ADI-同步數據轉換器陣列的采樣時鐘

同步數據轉換器陣列的采樣時鐘

同步數據轉換器陣列的采樣時鐘

評論