半導體屆“小紅人”——碳化硅肖特基,讓你的電源溫度低過冰墩墩,授權方案設計代理商KOYUELEC光與電子

第三代半導體碳化硅是目前半導體領域最熱門的話題。提到碳化硅(SiC),人們的第一反應是其性能優勢,如更低損耗、更高電壓、更高頻率、更小尺寸和更高結溫,非常適合制造大功率電子器件;如果說到應用,大多數人都會說它成本太高,推廣起來需假以時日,等等。事實上,在一些有性能、效率、體積、散熱,甚至系統成本有要求的應用中,典型代表行業如電源,碳化硅器件與硅器件的成本差距正在收窄。

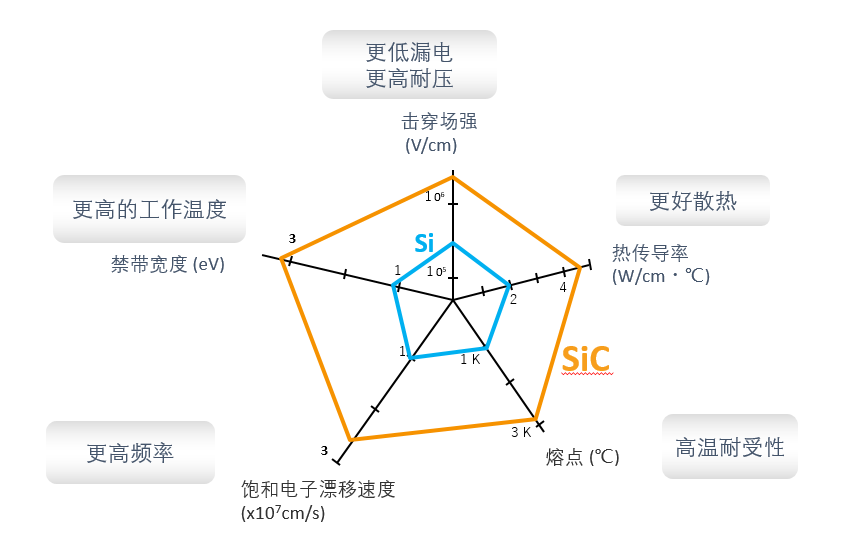

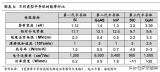

圖1 硅材料和碳化硅材料參數對比

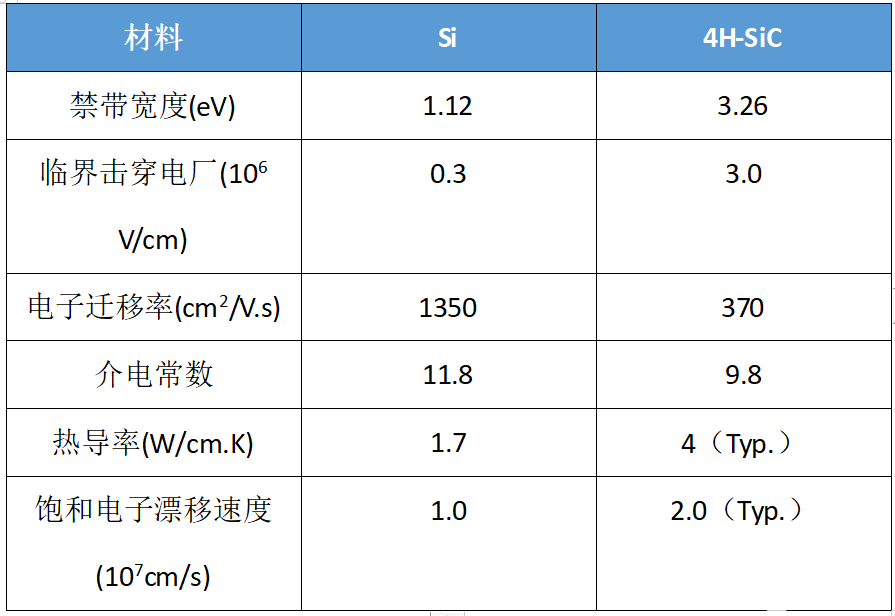

表1 硅材料和碳化硅材料參數對比

那么,基于如此明顯的優勢的碳化硅材料制成的碳化硅肖特基器件能帶來哪些優勢呢?

1、器件自身優勢

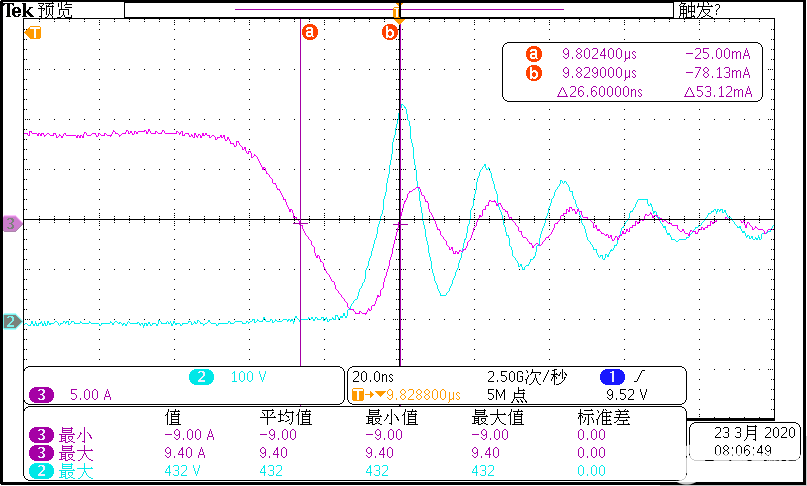

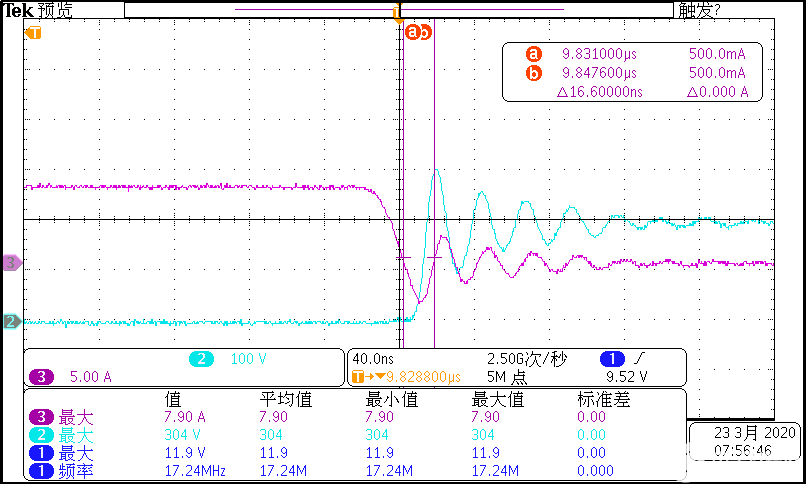

擊穿電壓高(常用電壓有650V/1200V)、可靠性高(結溫175℃ )、開關損耗小和導通損耗小、器件反向恢復時間幾乎為0,且恢復電壓應力較小(參考下圖),有利于降低系統噪聲,提高EMI裕量。

圖2 Si FRD 反向恢復波形

圖3 SiC SBD 反向恢復波形

2、應用優勢

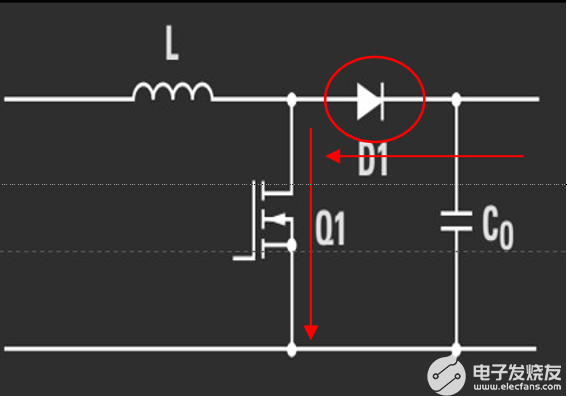

在CCM PFC電路中,碳化硅肖特基零反向恢復電流可以降低主功率MOSFET開啟瞬間的電流應力,從而使它能夠以較少的熱損失轉換電能,硅半導體必須大得多才能實現相同的性能。這體現在產品上,即碳化硅肖特基在降低電源溫度提高轉換效率的同時還能顯著減小電源的尺寸,這將為制造商帶來巨大的效益。

圖4 CCM PFC 電路圖

功率半導體作為電力系統的組成部分,是提升能源效率的決定性因素之一。在肖特基發展歷程中,追求更低損耗是行業一直以來的共同目標,肖特基器件損耗主要由導通損耗和開關損耗導致,且無用功損耗會以發熱的行式釋放,使電源溫度升高。

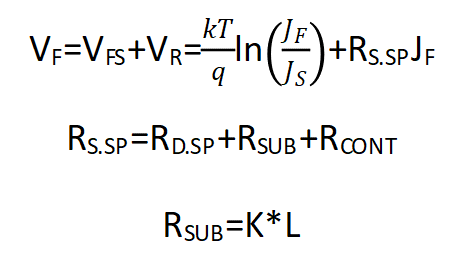

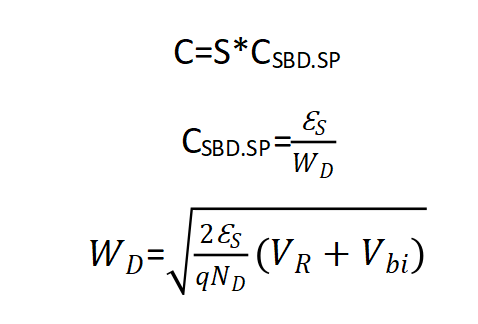

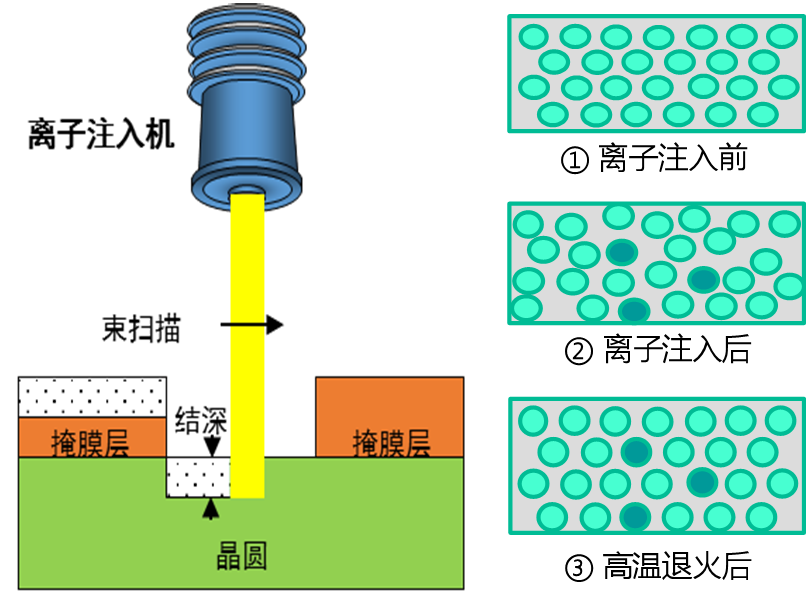

導通損耗和正向壓降正相關,我們根據VF正向壓降公式以及公式分解可以得到,降低芯片厚度可以有效降低VF。從而降低導通損耗。

而開關損耗和電容值正相關。根據推導公式可得,減小結面積可以有效降低電容值,從而降低開關損耗。

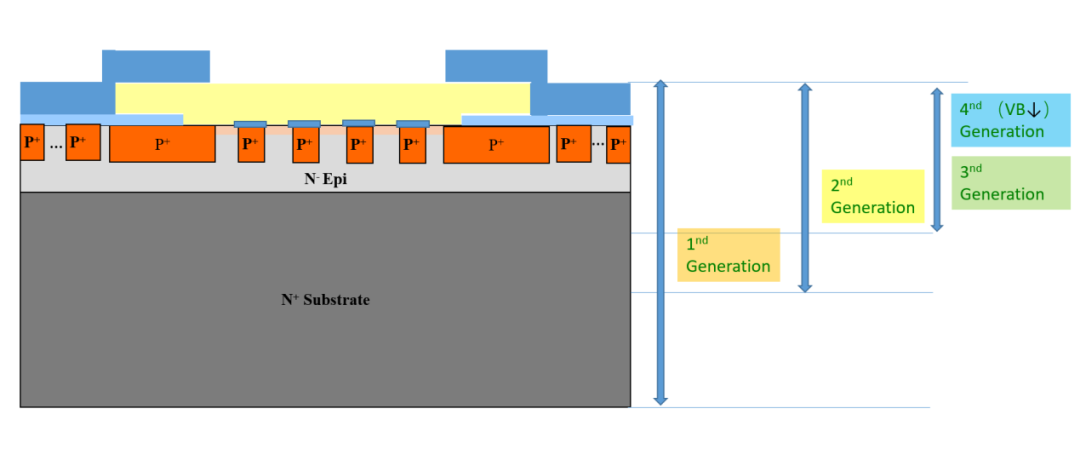

從設計人員的角度來看,正向壓降與電容二者之間的平衡至關重要,而使用新工藝可以帶來更優的綜合性能。目前碳化硅肖特基產品工藝節點大致可以分為4個:

第一代產品芯片厚度以300μm以上為工藝節點,常見厚度為300μm、350μm、390μm厚度。此工藝制造的芯片厚度較厚,對加工過程中減劃、金屬化等等工藝要求較低,但是缺點也是顯而易見的,由于芯片較厚故很難在正向壓降和電容之間得到一個較優的綜合性能,目前國內少部分廠家還沿用此工藝。

第二代產品以芯片厚度為250μm為代表。目前國內廠家量產產品大多采用此節點工藝,維安第一代產品也是基于此節點工藝進行開發(目前已經更新到第三代),但是此工藝較國際一線大廠還有一定差距。

第三代產品以芯片厚度150μm為代表。這個工藝節點也是國內大多數廠家在21年底到22年初推出的新工藝平臺,大部分廠家目前還正在處于研發階段,部分國際一線大廠量產產品采用150μm工藝節點,例如CREE C6系列在此節點工藝進行開發,但此工藝具國際最優水平還有一定差距。

第四代產品以100μm厚度為代表。此工藝水平為目前國際最優量產水平,國際上英飛凌C6等產品采用此節點工藝進行開發,得到VF和電容性能的綜合優勢,維安目前量產主推工藝也是采用此節點,工藝水平領先國內主流1代~1.5代水平。

3年的潛心研發,加之在開發過程中不斷自我優化迭代,維安碳化硅肖特基產品歷經250μm、150μm、100μm三次更新,目前量產產品全部采用100μm節點(維安第三代)薄片工藝,通過降低芯片厚度降低導通損耗和使用縮小有效結面積的方法降低電容,使器件電流密度,導通損耗和開關損耗等器件參數性能優于同行業水平。

圖5 維安碳化硅肖特基結構迭代示意圖

手機等消費類電源、太陽能逆變電源、新能源電動汽車及充電樁、工業控制特種電源……作為一個重要的快速發展的應用領域,電源行業的發展受益于功率器件技術進步,反過來又推動了功率器件的研發制造活動。在電源模塊中使用碳化硅肖特基器件,具有以下優勢:

開關損耗極低;

較高的開關頻率;

結溫高,從而降低了冷卻要求和散熱要求;

更小封裝,適合更緊湊的方案。

政府產業鼓勵政策固然重要,但是,真正的市場需求,更好的用戶體驗,以及產品優勢,才是引爆市場的關鍵。

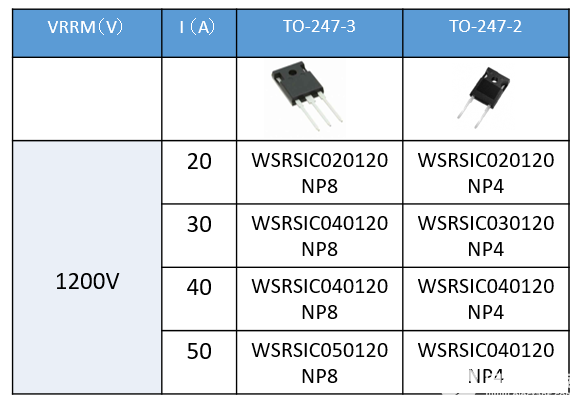

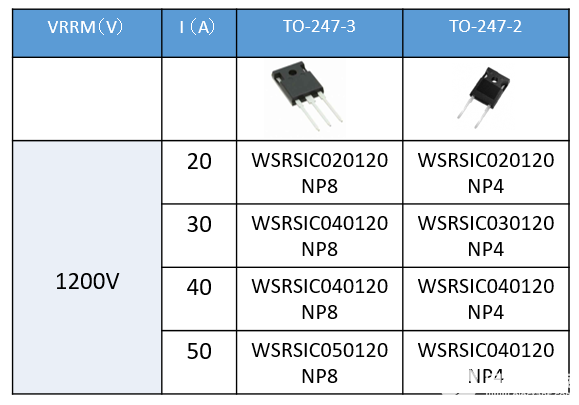

維安碳化硅肖特基推出以下系列產品:

表2 維安650V系列碳化硅肖特基二極管

表3 維安1200V系列碳化硅肖特基二極管

維安產品仍在不斷自我優化,正在開發第四代產品,持續推出損耗更小,開關速度更高的碳化硅肖特基器件。

審核編輯黃昊宇

-

二極管

+關注

關注

147文章

9575瀏覽量

165913 -

半導體

+關注

關注

334文章

27026瀏覽量

216357 -

SiC

+關注

關注

29文章

2768瀏覽量

62458

發布評論請先 登錄

相關推薦

碳化硅SiC制造工藝詳解 碳化硅SiC與傳統半導體對比

碳化硅器件的類型及應用

碳化硅壓敏電阻 - 氧化鋅 MOV

半導體碳化硅(SiC)行業研究

碳化硅特色工藝模塊簡介

碳化硅相對傳統硅半導體有什么有缺點

碳化硅逆變器是什么 功能介紹

碳化硅功率器件簡介、優勢和應用

碳化硅肖特基二極管的優勢和應用領域

氮化鎵半導體和碳化硅半導體的區別

碳化硅在溫度傳感器中的應用

碳化硅是如何制造的?碳化硅的優點和應用

基本半導體:功率半導體的碳化硅時代

半導體屆“小紅人”—WAYON維安碳化硅肖特基,讓你的電源溫度低過冰墩墩

半導體屆“小紅人”—WAYON維安碳化硅肖特基,讓你的電源溫度低過冰墩墩

評論