對于FPGA工程師的核心競爭力,其實FPGA工程師在真正工業(yè)界還是有細分的,大致可以分為兩部分,做IC原型驗證的(包括design和verification),用FPGA開發(fā)產(chǎn)品的。

做IC原型驗證大多不需要了解算法,只是根據(jù)設計人員的設計框圖實現(xiàn)邏輯(大公司);做產(chǎn)品開發(fā)的可能離具體的應用和算法更近一些,相當于將特定應用和算法做硬件實現(xiàn)。我這里講的更加側重的是做FPGA實現(xiàn)這類的工程師(包括IC原型驗證的design和產(chǎn)品設計的design)。我將更細致的給出一些我認為重要的能力。

1、 RTL設計實現(xiàn)能力。

關于FPGA工程師的核心競爭力,很多人會提到算法實現(xiàn)能力,我將這歸結為RTL設計實現(xiàn)能力的一部分,RTL實現(xiàn)是FPGA工程師或者說HDL開發(fā)人員的入門首先接觸到的東西,我將其總結為如下幾點:

a、硬件的實現(xiàn)思路

HDL設計實現(xiàn)和軟件實現(xiàn)的思路不同,HDL作為一種描述語言,側重的是對硬件的映射和連接關系的描述,當然也有邏輯、處理的實現(xiàn),但歸根揭底所有的邏輯都是在硬件上實現(xiàn)的,最終都會映射為加法器,乘法器,狀態(tài)機,計數(shù)器,編碼器(優(yōu)先),解碼器等等一些列硬件資源,對于邏輯拆解和抽象能力將直接關系到最終編碼的效率。

簡單的來說,好的HDL編碼人員編寫的代碼更容易被編譯器綜合,對于初學者來講,編譯器的綜合(包括后續(xù)Map布局布線)時間以及warning數(shù)量以及最后綜合出來資源和你預先設計的吻合程度可以做為考量HDL代碼好壞的一種方式。

b、資源和時序的優(yōu)化能力

資源和時序的優(yōu)化能力是作為FPGA(ASIC)開發(fā)人員進階的能力,這里就需要大量的經(jīng)驗和反復的迭代,不斷對硬件(FPGA底層結構)深入理解才能夠達到。

對于FPGA來講和ASIC設計有所不同,ASIC的硬件實現(xiàn)很多是由綜合器決定的(比如用什么樣的乘法器),但是對于FPGA來講,資源全部是固定的,F(xiàn)PGA資源可以分為三塊,運算邏輯(LUT DSP carry chain等),存儲單元(REG SRL BRAM DRAM),IO(各種高速低速接口),相同的算法應用可以用不同的資源,不同資源的組合方式來實現(xiàn)。

那么如何用更少的資源,更快的主頻實現(xiàn)某一算法,這就需要有很強的資源和時序優(yōu)化能力,通常這種優(yōu)化是經(jīng)過多次迭代的,當然通常頂層的設計人員會對系統(tǒng)層次的資源和時序有著較為準確的把握,也會給出各個模塊的設計指標和邊界,但是不同開發(fā)人員水平和能力最終設計的結果是不一樣的,好的資源和時序優(yōu)化能力是FPGA工程師的重要競爭力。

再反過頭來說軟件開發(fā),其實從優(yōu)化上來講和RTL設計或者說HDL開發(fā)沒什么不同,好的軟件設計人員更了解計算機底層,對于資源(時間,空間)的使用,對于算法的效率的分析也更加深刻,因此也能寫出更好的軟件代碼,我覺得在這一層面上無論軟件還是硬件開發(fā)都是對于邏輯的抽象能力(當然術有所不同)。

2、 硬件調(diào)試能力。

調(diào)試能力,也是作為FPGA開發(fā)人員和所有從事硬件開發(fā)人員都一直認可的能力或者說核心競爭力。

舉個例子,在找工作的時候如果你能向別人展示出你無與倫比的調(diào)試能力,別人沒有理由不要你。調(diào)試能力需要大量的現(xiàn)場經(jīng)驗作為積累,同時也需要人的邏輯分析能力,當然還需要耐心,細致等等人的高尚品質 ,這里我也做一個小小的總結。

a、 FPGA本身調(diào)試工具的使用

我想這里又可以分為兩個階段,仿真和上板調(diào)試,仿真我想作為FPGA工程師都不陌生,大型的開發(fā),通常有多個不同層次的模型,基本算法原理的模型,硬件仿真模型(通過C或matlab做定點仿真),然后再試HDL仿真模型(通過modelsim仿真最后的實現(xiàn)),仿真是一門很大的學問,現(xiàn)在都有專門的verification人員做。

但是對于普通FPGA開發(fā)人員來京,如何利用仿真這個工具來高效率的調(diào)試是一個值得思考的問題,一些異步的輸入情況如何用仿真來排除問題,上板調(diào)試發(fā)現(xiàn)問題,根據(jù)問題輸入情況仿真排除問題,這些都是利用FPGA仿真工具來調(diào)試的手段。

對于上板調(diào)試,主要就是利用chipsocpe添加調(diào)試信號,這里又涉及到如何利用有限資源(chipsocpe信號數(shù)量和深度)來排除問題,通常在上板調(diào)試發(fā)現(xiàn)問題后,仿真又無法定位解決(仿真是有和硬件不一致的情況的,比如一些RAM沖突的問題)。

經(jīng)過分析加入合適的調(diào)試信號,設置合適的觸發(fā)條件,然后定位排除問題。這些說起來容易,實際還是需要大量的上板經(jīng)驗,特別是大型系統(tǒng)的調(diào)試經(jīng)歷不斷磨練提升。

此外還有一些應用需要配合外部儀器來獲取更多信息幫助定位問題,包括示波器,譜分析儀,網(wǎng)絡分析儀等常用實驗室儀器。

b、問題定位分析能力

上面講的是都是利用工具來進行調(diào)試,但是硬件比軟件難得地方就在于其調(diào)試的復雜性,很多時候無法利用工具進行問題的定位,比如現(xiàn)象無法復現(xiàn),輸入條件隨機或者過于復雜,涉及模塊邏輯很多等等情況,這時候去定位問題大多靠想,就是邏輯分析來排出問題。我認為這是FPGA工程師真正的核心競爭力,因為這不僅僅需要經(jīng)驗的積累,同時還需要很好的邏輯思維和分析能力。

c、系統(tǒng)調(diào)試能力

系統(tǒng)調(diào)試能力是更加難得一項能力,通常做到系統(tǒng)層次的人員不會再具體的寫代碼或者上手調(diào)了,當然對于小團隊小公司還是得自己上手。系統(tǒng)層面的調(diào)試能力一方面是對FPGA頂層的調(diào)試能力,各個模塊構成的片上系統(tǒng)的問題分析定位能力。

通常各個模塊在系統(tǒng)聯(lián)調(diào)之前都是經(jīng)過驗證的,但是在聯(lián)調(diào)的時候還是會出現(xiàn)各種各樣的問題,這時候的問題反饋的信息更加少,設計的邏輯模塊更加多,如何一步步抽絲撥繭定位到問題所在,并且采用什么樣的方式去解決(這時候通常不是單獨解決一個內(nèi)部模塊就行的),都需要很深厚的功力。

另外一方面是整個硬件軟件系統(tǒng)層次的調(diào)試能力,要看得懂原理圖PCB,懂硬件,了解軟件接口,現(xiàn)在FPGA越來越講究Hardware Software Co-design,軟件硬件這個系統(tǒng)層次的調(diào)試能力對人的要求更加高,當然這通常已經(jīng)遠離了通常FPGA工程師的職責,但是我認為這是作為FPGA工程師上升通道中的重要能力。

3、更加高層次的

更加高層次的東西,我個人的理解,還是系統(tǒng)層次的東西,算法和架構。

怎樣將一系列數(shù)學公式,轉換為算法,再最終形成系統(tǒng)硬件的實現(xiàn);整個系統(tǒng)采用什么樣的架構,純FPGA,arm FPGA,DSP FPGA,SOC FPGA;FPGA頂層采用什么架構,通用總線還是自定義總線,如何考慮通用性和可擴展性等等。

再大至什么樣的應用適合用FPGA實現(xiàn),什么樣的問題適合軟件實現(xiàn),怎樣的組合能更加低成本高效率的解決問題,這一些列問題涉及的東西就很多了,我講的都是以FPGA為核心做開發(fā)要面臨的問題,其實其他平臺的硬件、軟件產(chǎn)品都是類似,系統(tǒng)層面的問題都是復雜的問題,同時我也認為,從系統(tǒng)層面去優(yōu)化,解決問題才是最高效率的方式。

歸根結底,一個FPGA工程師的核心競爭力來源于深厚的技術功底,但是技術功底也并非通過一天練成的,最重要的是時間的積累,不斷的鉆研以及真正的興趣。

歡迎加入至芯科技FPGA微信學習交流群,這里有一群優(yōu)秀的FPGA工程師、學生、老師、這里FPGA技術交流學習氛圍濃厚、相互分享、相互幫助、叫上小伙伴一起加入吧!

點個在看你最好看

原文標題:FPGA到底是什么?,F(xiàn)PGA工程師核心競爭力是什么?

文章出處:【微信公眾號:FPGA設計論壇】歡迎添加關注!文章轉載請注明出處。

-

FPGA

+關注

關注

1626文章

21678瀏覽量

602006

原文標題:FPGA到底是什么?,F(xiàn)PGA工程師核心競爭力是什么?

文章出處:【微信號:gh_9d70b445f494,微信公眾號:FPGA設計論壇】歡迎添加關注!文章轉載請注明出處。

發(fā)布評論請先 登錄

相關推薦

Keysight助力提升工程師的測試測量知識水平

FPGA算法工程師、邏輯工程師、原型驗證工程師有什么區(qū)別?

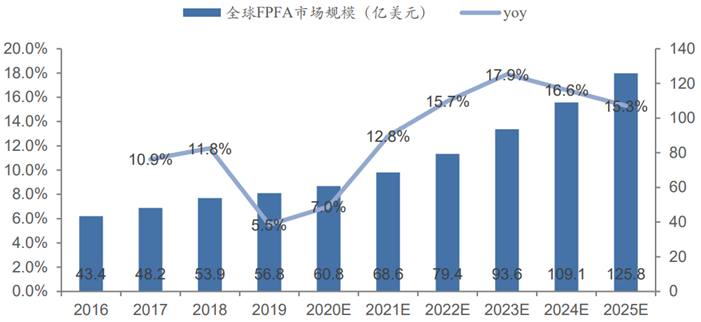

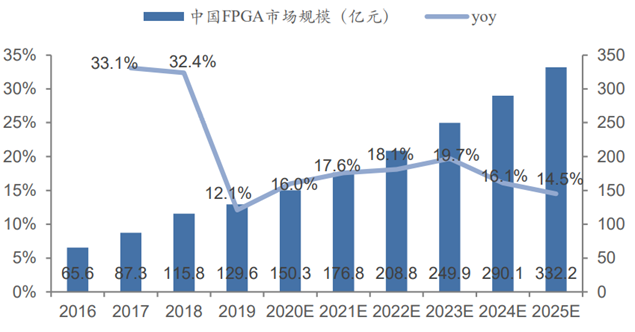

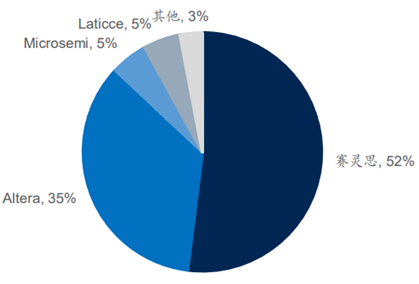

國產(chǎn)FPGA的發(fā)展前景是什么?

硬件工程師業(yè)余時間變現(xiàn),應該從何處入手?

一個更適合工程師和研究僧的FPGA提升課程

fpga 工程師應該掌握的

數(shù)據(jù)中臺:如何構建企業(yè)核心競爭力

fpga開發(fā)板是什么?fpga開發(fā)板有哪些?

fpga工程師前景如何

fpga工程師就業(yè)趨勢

到底什么是ASIC和FPGA?

【2023電子工程師大會】國產(chǎn)FPGA技術及國內(nèi)FPGA發(fā)展pp

FPGA到底是什么?,F(xiàn)PGA工程師核心競爭力是什么?

FPGA到底是什么?,F(xiàn)PGA工程師核心競爭力是什么?

評論