數據轉換器是通信系統中的關鍵元件 在光纖等模擬傳輸介質之間形成橋梁 光學、微波、射頻和數字處理模塊,如 FPGA。 和 DSP。 系統設計人員通常專注于選擇最 適合應用的數據轉換器,而數據轉換器要少得多 可以考慮時鐘代的選擇 提供數據轉換器的設備。種類繁多的時鐘發生器 提供具有廣泛不同的性能屬性。 但是,如果不仔細考慮時鐘發生器,相位 噪聲和抖動性能特征,數據轉換器, 動態范圍和線性度性能會受到嚴重影響。 本文討論了時鐘發生器的影響、相位噪聲、 以及數據轉換器動態范圍和線性度的抖動 (ADC 和 DAC)詳細介紹。時鐘抖動的理論分析 給出了轉換器信噪比并提供仿真結果 使用ADI公司的高性能時鐘發生器。

ADI公司開發了獨特的高性能時鐘系列 支持系統設計人員的配電和時鐘生成產品 以最大限度地提高數據轉換器的性能。The HMC1032LP6GE HMC1034LP6GE是SMT封裝時鐘發生器,它們是 適用于各種高性能蜂窩/4G 基礎設施、光纖 光學和網絡應用,并提供一流的抖動和 業界領先的相位本底噪聲。HMC987LP5E 1:9扇出緩沖器 非常適合作為關鍵應用中的時鐘驅動器,具有超低噪聲 ?166 dBc/Hz 的底線。這些器件的主要規格如 表 1 和 2.

| 部件號 | 最大頻率(兆赫) | 功能 | 典型相位抖動(fs rms) | 本底相位噪聲 (dBc/Hz) | 最大參考頻率(兆赫) | 典型功耗 (W) | 品質因數 (壓裂/整數) (dBc/Hz) |

| HMC1032LP6GE | 350 | 具有小數N分頻PLL和VCO的高性能時鐘發生器 | 75 | –165 | 350 | 0.86 | –227/–230 |

| HMC1034LP6GE | 3000 | 具有小數N分頻PLL和VCO的高性能時鐘發生器 | 78 | –165 | 350 | 0.86 | –227/–230 |

| 部件號 | 最大時鐘速率 (千兆赫) | 功能 | 輸入 | 輸出 | 相位抖動(12 kHz 至 20 MHz) | 上升/下降時間(ps) | 通道偏斜(ps) | 通道禁用模式 | 電源(V) |

| HMC987LP5E | 8 | 1:9 扇出緩沖器 | LVPECL, LVDS, CML, CMOS | 綠佩克利 | 8 fs 有效值 | 65 | 3.1 | 是的 | 3.3 |

系統注意事項

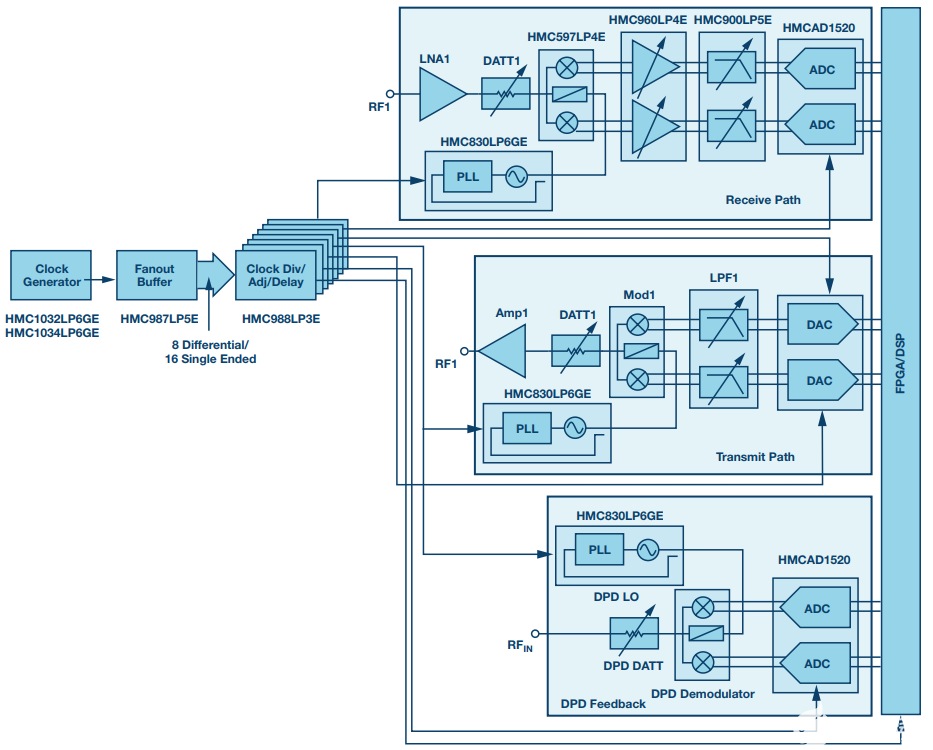

利用MIMO(多輸入)的典型LTE(長期演進)基站 多輸出)架構如圖 1 所示。該架構包括 多個發射器、接收器和DPD(數字預失真)反饋路徑。 各種發射器/接收器組件,例如數據轉換器(ADC/ DAC)和本振(LO)需要低抖動參考時鐘來改善 性能。其他基帶組件也需要各種時鐘源 頻率。

圖1.采用 MIMO 架構的典型 LTE 基站的時鐘定時解決方案。

用于實現基站間同步的時鐘源通常 來自GPS(全球定位系統)或CPRI(普通公共無線電) 接口)鏈接。這種源通常具有出色的長期頻率穩定性; 但是,它需要頻率轉換為所需的本地參考 頻率具有出色的短期穩定性或抖動。高性能時鐘 發生器,如HMC1032LP6GE,執行頻率轉換 并提供低抖動時鐘信號,然后可以將其分配給各種 基站組件。選擇最佳時鐘發生器至關重要 因為次優參考時鐘會導致較高的LO相位噪聲, 導致更高的發射/接收EVM(誤差矢量幅度)和系統 信噪比(信噪比)。高時鐘抖動和本底噪聲也會影響數據 轉換器通過降低系統信噪比,并引入雜散數據轉換器 輻射,從而進一步降低數據轉換器SFDR(無雜散) 動態范圍)。因此,最終需要低性能時鐘源 降低系統容量和吞吐量。

時鐘發生器規格

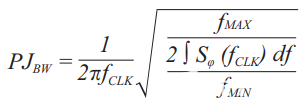

雖然時鐘抖動有多種定義,但最適用的定義 在數據轉換器應用中是相位抖動,以時域指定 PS RMS 或 FS RMS 的單位。相位抖動 (PJBW) 是由 在特定偏移范圍內對時鐘信號的相位噪聲進行積分 從載波,由以下等式給出:

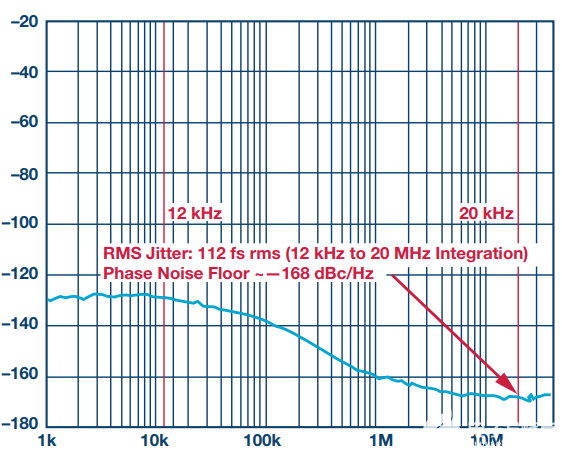

f時鐘是操作的頻率;f最低/f.MAX指示感興趣的帶寬, 和 S(f時鐘) 表示 SSB 相位噪聲。的上限和下限 積分帶寬 (f最低/f.MAX) 對于每個應用程序都是唯一的,并且由 設計將敏感的相關光譜內容。設計師的 目標是選擇集成噪聲最低的時鐘發生器, 或所需帶寬中的相位抖動。傳統上,時鐘發生器是 特點是積分超過 12 kHz 至 20 MHz,這是指定的 對光通信接口(如 SONET)的要求。雖然這 可能適用于某些數據轉換器應用,范圍更廣 通常需要集成,特別是擴展到 20 MHz 以上才能捕獲 高速數據轉換器采樣時鐘的相關噪聲曲線。 測量相位噪聲時,噪聲偏移遠離載波頻率。 例如,用于數據轉換器采樣的實際時鐘頻率為 通常稱為遠離載波相位噪聲。這種噪聲的極限是 通常稱為相位本底噪聲,如圖2所示。這個數字 顯示了ADI公司HMC1032LP6GE時鐘發生器的實際測量曲線。 相位本底噪聲在數據轉換器中顯得尤為重要 由于轉換器SNR對寬帶的敏感性的應用 時鐘輸入端的噪聲。當設計人員評估時鐘發生器選項時, 必須將相位本底噪聲性能視為關鍵基準。

圖2.HMC1032LP6GE的相位噪聲和抖動性能

圖2顯示了12 kHz范圍內~112 fs rms的積分相位抖動 至 20 MHz 積分帶寬,相位噪底為 ~–168 dBc/Hz 工作頻率為 ~160 MHz 時。這里值得注意的是,當 考慮最適合數據轉換器的時鐘發生器, 設計人員不僅應參考 頻域,還可以進行時鐘信號質量測量,如占空比 時域中的周期和上升/下降時間。

數據轉換器性能

為了描述時鐘噪聲對數據轉換器的性能影響, 轉換器可以被認為是數字混音器,但有細微的區別。 在混頻器中,LO的相位噪聲被添加到被混合的信號中。在 一個數據轉換器 時鐘的相位噪聲施加在轉換 輸出,但被信號與時鐘頻率的比值抑制。這 時鐘抖動會導致采樣時間錯誤,表現為 信噪比降低。

時間抖動,T抖動,只是采樣時間內的均方根誤差,表示 在幾秒鐘內。

在某些應用中,可以使用時鐘濾波器來減少時鐘的抖動 信號,但這種方法有明顯的缺點:

濾波器可以消除時鐘信號的寬帶噪聲,但窄帶噪聲仍然存在。

濾波器的輸出通常是正弦波輸出,壓擺率較慢,這會影響時鐘信號對時鐘路徑中內部噪聲的敏感性。

濾波器消除了改變時鐘頻率以實現多種采樣速度架構的靈活性。

更實用的方法是使用具有快速轉換的低噪聲時鐘驅動器 速率和高輸出驅動能力,以最大限度地提高時鐘信號的斜率。 此方法優化性能的原因如下:

消除時鐘濾波器可降低設計復雜性和元件數量。

快速上升時間可抑制ADC時鐘路徑內部的噪聲。

窄帶和寬帶噪聲都可以通過選擇最佳時鐘源來優化

可編程時鐘發生器可實現不同的采樣率,這使得該解決方案更能適應不同的應用。

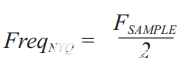

極低的時鐘本底噪聲至關重要。時鐘抖動噪聲遠離載波 在ADC中采樣,并折疊到ADC數字輸出頻率中 樂隊。該頻段受奈奎斯特頻率的限制,奈奎斯特頻率的定義如下:

時鐘抖動通常由 模數轉換器時鐘信號。雖然ADC的SNR性能取決于各種 因素,時鐘信號的寬帶抖動的影響由下式給出 以下等式:

如圖所示,與混頻器不同,時鐘抖動的SNR貢獻是直接的 與模擬輸入頻率成正比,f在,到ADC。

驅動ADC時,時鐘噪聲受時鐘帶寬的限制 驅動器路徑,通常由ADC時鐘輸入電容主導。 寬帶時鐘噪聲將調制大輸入信號,并將折疊成 模數轉換器輸出頻譜。時鐘路徑的相位噪聲會降低 輸出SNR與輸入信號的幅度和頻率成正比。 最壞的情況是當存在大高頻信號時 一個小信號。

在現代無線電通信系統中,通常情況是多個 載波信號存在于輸入中,感興趣的單個信號是 在DSP中濾波以匹配信號帶寬。在許多情況下,一個大的, 一個頻率的不需要的信號會與時鐘噪聲混合并降低性能 ADC通帶中其他頻率下的可用SNR。在這樣的一個 在這種情況下,感興趣的SNR是所需信號帶寬中的SNR。另外 信噪比抖動上面的值實際上是相對于最大振幅 信號,通常是不需要的信號或阻塞器。

目標信號頻帶內的輸出噪聲由下式決定:

計算時鐘噪聲較大且較大時的ADC性能下降 給定輸入頻率下的不需要的信號;例如,計算 ADC全帶寬中的信噪比。

使用所需信號帶寬相對于完整帶寬的比率 數據轉換器帶寬,用于計算所需信號中的SNR 帶寬。

根據不需要的信號的幅度提高值 低于滿量程。

步驟b的結果只是將先前顯示的SNR方程修改為: 遵循:

信 噪 比抖動:SNR貢獻時鐘抖動,進入fBW,在頻率鰭片存在大信號的情況下,采樣率,fs。

f在:滿量程不需要的信號的輸入頻率,以赫茲為單位。

T抖動:ADC 時鐘的輸入抖動,以秒為單位。

fBW:所需輸出信號的帶寬,以 Hz 為單位。

fs:數據轉換器的采樣率,單位:Hz。

信 噪 比直流:帶直流輸入的數據轉換器的信噪比,單位為dB

最后,在目標信號頻帶中可用的最大SNR,具有 全量程阻塞器的存在,只是抖動和噪聲功率的總和 DC貢獻。

例如,500 MSPS數據轉換器,在直流時ENOB為12.5位,或 相當于 75 dB SNR,在采樣率一半的帶寬上進行評估, 在 250 兆赫時。如果目標信號的寬度為 5 MHz,則 SNR 可能接近 直流,在具有完美時鐘的 5 MHz 帶寬中,將為 75 + 10 × log10(250/5) = 92 dB。

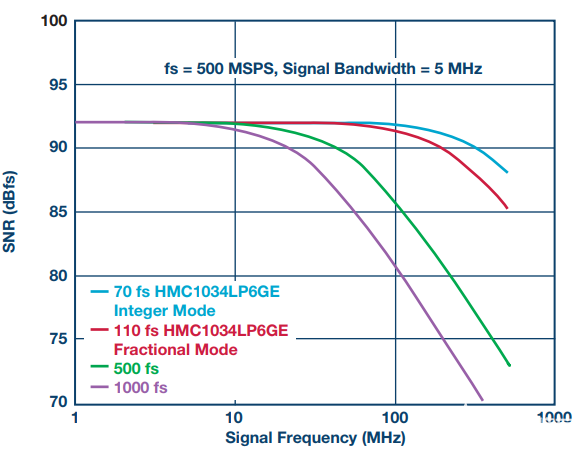

但是,ADC時鐘并不完美,圖3顯示了 5 MHz 所需信號帶寬的衰減,作為 在 x 軸上的頻率處輸入大的不需要的信號。的影響 隨著時鐘抖動的增加,不需要的信號更加嚴重,并且隨著 輸入頻率增加。如果不需要的信號的幅度減小, 可用的信噪比將按比例增加。

例如,對滿量程、5 MHz 不需要的 W-CDMA 信號進行采樣 在 200 MHz 輸入下,具有高質量的 500 MHz 時鐘,例如 HMC1034LP6GE在整數模式下運行時具有70 fs抖動,然后 附近5 MHz信道中的SNR約為91 dB。相反,如果 時鐘抖動降低到500 fs,相同的數據轉換器和信號將 僅表現出 81 dB 的 SNR,這表示 性能。

以400 MHz(70 fs時鐘)將相同的信號輸入數據轉換器 將產生 88 dB 的信噪比。同樣,對于 500 fs 時鐘,SNR 值 將降級到僅 75 dB。

圖3.ADC SNR 與時鐘抖動和輸入頻率的關系

結論

為時鐘生成和數據轉換選擇正確的組件 使設計人員能夠從給定的體系結構中提取最佳性能。 選擇時鐘發生器時要考慮的重要標準是相位 抖動和相位本底噪聲,影響數據轉換器的SNR 打卡。如分析所示,所選的低相位本底噪聲 時鐘發生器及其低集成相位抖動有助于最大限度地減少 在多載波應用中,ADC 輸入頻率較高時 SNR 會降低。 HMC1032LP6GE和HMC1034LP6GE時鐘發生器均采用設計 考慮到數據轉換器應用,并與ADI的高速配合良好 模數轉換器器件。

審核編輯:郭婷

-

轉換器

+關注

關注

27文章

8507瀏覽量

145988 -

驅動器

+關注

關注

51文章

7998瀏覽量

145026 -

adc

+關注

關注

97文章

6300瀏覽量

542459

發布評論請先 登錄

相關推薦

時鐘發生器性能對數據轉換器的影響

時鐘發生器的相位噪聲和抖動性能為什么會影響到數據轉換器?

MAX3679A高性能四路輸出時鐘發生器(Maxim)

數據轉換器中時鐘發生器件對系統性能的影響

Cypress時鐘發生器的分類,它有哪些應用

時鐘發生器性能對數據轉換器的影響

時鐘發生器性能對數據轉換器的影響

時鐘發生器性能對數據轉換器的影響

評論