作者:Rob Reeder、Duncan Bosworth、Ronak Shah和Dan Pritsker

現(xiàn)代電子戰(zhàn) (EW) 系統(tǒng)開(kāi)發(fā)人員正面臨多重挑戰(zhàn),包括頻譜擁塞增加和以更高的檢測(cè)靈敏度監(jiān)視更寬帶寬。此外,系統(tǒng)開(kāi)發(fā)人員減少開(kāi)發(fā)時(shí)間的推動(dòng)使許多現(xiàn)有開(kāi)發(fā)模型不堪重負(fù),導(dǎo)致定制硬件和固件設(shè)計(jì)在尺寸、重量和功耗限制下實(shí)現(xiàn)更高的性能水平。

新的每秒千兆采樣 (GSPS) 高速轉(zhuǎn)換器、高性能 FPGA 和 FPGA IP 內(nèi)核正在改變現(xiàn)狀,為設(shè)計(jì)人員提供現(xiàn)成的解決方案和可配置的構(gòu)建模塊,以應(yīng)對(duì)下一代挑戰(zhàn)。參考設(shè)計(jì)采用ADI公司的GSPS ADC,采用Altera FPGA和通道化IP,將展示設(shè)計(jì)人員如何利用最先進(jìn)的電子智能和數(shù)字RF存儲(chǔ)器系統(tǒng)解決方案加快上市時(shí)間。

電子戰(zhàn)概述

電子戰(zhàn)系統(tǒng)識(shí)別和應(yīng)對(duì)監(jiān)視和跟蹤雷達(dá)等電子威脅。電子戰(zhàn)系統(tǒng)通常分為電子支持(ES),電子攻擊(EA)或電子保護(hù)(EP)。

ES系統(tǒng)攔截和測(cè)量信號(hào)參數(shù),以識(shí)別信號(hào)源并執(zhí)行威脅分析。EA 系統(tǒng)產(chǎn)生干擾信號(hào)以壓倒真實(shí)脈沖。數(shù)字射頻存儲(chǔ)器 (DRFM) 是一種欺騙雷達(dá)的欺騙技術(shù)。EP系統(tǒng)專(zhuān)注于處理和存儲(chǔ)傳入信號(hào)以構(gòu)建信號(hào)數(shù)據(jù)庫(kù)。該數(shù)據(jù)庫(kù)是一個(gè)不斷更新的查找表,用于識(shí)別未來(lái)的雷達(dá)系統(tǒng)。傳統(tǒng)上,這些系統(tǒng)是在模擬平臺(tái)上開(kāi)發(fā)的。現(xiàn)代系統(tǒng)的數(shù)字化程度明顯更高,以利用可編程邏輯器件中可用的信號(hào)處理功能。

來(lái)自這些系統(tǒng)中未知目標(biāo)的威脅檢測(cè)需要一個(gè)接收器,該接收器可以在寬頻帶上運(yùn)行,以識(shí)別和啟動(dòng)針對(duì)威脅的對(duì)策。典型的電子戰(zhàn)系統(tǒng)可以在直流至20 GHz的范圍內(nèi)工作。 除了寬帶寬要求外,實(shí)用的電子戰(zhàn)系統(tǒng)還需要高動(dòng)態(tài)范圍、高靈敏度和精確的脈沖表征,因?yàn)樾孪到y(tǒng)正被推到以更高的檢測(cè)靈敏度更快地檢查目標(biāo)帶寬。當(dāng)輸入電子戰(zhàn)系統(tǒng)的信號(hào)可能來(lái)自多個(gè)來(lái)源時(shí),會(huì)出現(xiàn)更復(fù)雜的情況,每個(gè)來(lái)源都需要識(shí)別和區(qū)分。除了來(lái)自對(duì)手的故意干擾之外,頻譜擁塞的增加,特別是通信基礎(chǔ)設(shè)施的快速擴(kuò)張,使得有效檢測(cè)變得更加具有挑戰(zhàn)性。

具有更小尺寸、重量和功耗目標(biāo)的復(fù)雜系統(tǒng)正在推動(dòng)更長(zhǎng)的開(kāi)發(fā)周期。然而,下一代現(xiàn)成的解決方案與可編程構(gòu)建模塊相結(jié)合,為這些挑戰(zhàn)提供了解決方案。將進(jìn)一步研究對(duì)任何電子戰(zhàn)系統(tǒng)至關(guān)重要的兩個(gè)關(guān)鍵構(gòu)建模塊,即模數(shù)轉(zhuǎn)換器和實(shí)時(shí)通道化IP,以說(shuō)明如何應(yīng)對(duì)這些挑戰(zhàn)。

電子戰(zhàn)系統(tǒng)中的ADC瓶頸

在許多情況下,從模擬域到數(shù)字域的高速ADC轉(zhuǎn)換是ES、EA和EP系統(tǒng)的限制因素,在這些系統(tǒng)中,系統(tǒng)架構(gòu)師經(jīng)常面臨難題。雖然最小化成本和系統(tǒng)尺寸通常是重中之重,但系統(tǒng)設(shè)計(jì)人員還必須在增加瞬時(shí)監(jiān)控帶寬以最大限度地提高攔截概率的需求與如何最大限度地減少帶內(nèi)高功率信號(hào)對(duì)系統(tǒng)脫敏的影響之間取得最佳平衡。這些要求對(duì)轉(zhuǎn)換器設(shè)計(jì)和將信號(hào)內(nèi)容耦合到轉(zhuǎn)換器的前端設(shè)計(jì)提出了挑戰(zhàn)。即使轉(zhuǎn)換器本身具有出色的性能,前端也必須能夠保持信號(hào)質(zhì)量,這導(dǎo)致對(duì)性能和成本的不斷推動(dòng),達(dá)到高速ADC的極限。

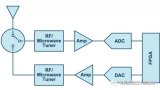

圖1顯示了一個(gè)簡(jiǎn)單的電子戰(zhàn)系統(tǒng)。該系統(tǒng)的主要特性包括RF接收器(用于下變頻和選擇目標(biāo)頻段進(jìn)行詢(xún)問(wèn))、ADC用于將數(shù)據(jù)從模數(shù)域轉(zhuǎn)換到數(shù)字域,以及數(shù)字信號(hào)處理引擎,通常是配置為檢測(cè)、確定、分析和管理目標(biāo)信號(hào)存儲(chǔ)的FPGA。DRFM和EA系統(tǒng)還包括使用高速DAC的相應(yīng)發(fā)射鏈。

圖1.典型的電子戰(zhàn)架構(gòu)信號(hào)鏈。

從歷史上看,增加瞬時(shí)帶寬同時(shí)保持所需的線(xiàn)性度需要使用多個(gè)重疊接收器或交錯(cuò)架構(gòu)。每個(gè)重疊的接收器通過(guò)數(shù)字信號(hào)處理將所需帶寬的一部分?jǐn)?shù)字化,用于重新組合來(lái)自每個(gè)通道的數(shù)據(jù)和可觀察頻譜。對(duì)于交錯(cuò)式架構(gòu),它通常與所需的校準(zhǔn)一起使用,以最小化轉(zhuǎn)換器之間的相位、失調(diào)和增益差異。這兩種方案的實(shí)現(xiàn)成本通常都很高,但數(shù)字信號(hào)處理通常是根據(jù)實(shí)現(xiàn)方案定制的。

ADI公司的新型RF采樣ADC(如AD9625)為下一代系統(tǒng)提供了解決方案,提供更大的瞬時(shí)帶寬,但具有更高的線(xiàn)性度,以保持所需的靈敏度水平。AD9625是一款2.5 GSPS、12位ADC,旨在提高高帶寬交流性能,采用1 GHz輸入時(shí),典型SNR/SFDR分別為57 dB/80 dB,前所未有。該ADC還支持多個(gè)轉(zhuǎn)換器的同步,這通常是確定到達(dá)角所必需的,并集成了數(shù)字下變頻器(DDC),以抽取和觀察輸出頻譜的較小部分。

AD9625能夠支持超過(guò)3 GHz的小信號(hào)模擬帶寬,為系統(tǒng)設(shè)計(jì)人員提供了極大的IF定位靈活性。憑借第一和第二奈奎斯特采樣選項(xiàng)以及超過(guò) 1 GHz 的可用帶寬,設(shè)計(jì)人員能夠最大限度地利用前端接收器架構(gòu),以實(shí)現(xiàn)濾波和系統(tǒng)復(fù)雜性的最佳平衡。

ADI公司的器件支持并行和串行接口,包括JESD204B標(biāo)準(zhǔn)。這對(duì)于支持許多電子戰(zhàn)系統(tǒng)中的高數(shù)據(jù)速率和低延遲要求非常重要。

為了便于快速原型設(shè)計(jì)和系統(tǒng)開(kāi)發(fā),AD9625作為VITA 42/FPGA夾層卡(FMC)平臺(tái)提供(見(jiàn)圖2)。該平臺(tái)提供有關(guān)如何優(yōu)化ADC前面的信號(hào)調(diào)理以?xún)?yōu)化性能的參考設(shè)計(jì),并確保ADC和處理單元之間的數(shù)據(jù)處理接口具有足夠的帶寬,以支持來(lái)自轉(zhuǎn)換器的實(shí)時(shí)全速率數(shù)據(jù),同時(shí)仍使用CoTs架構(gòu)。其結(jié)果是一個(gè)高效的架構(gòu),集成了 2.5 GSPS ADC COTS 解決方案,以最小的占用空間提供高速導(dǎo)管。

圖2.AD9625,2500 MSPS,12位FMC板,支持同步。(PN: AD-FMCADC2-EBZ)

通道器概述

盡管 EA、ES 和 EP 系統(tǒng)中具有特定的信號(hào)特性,但一個(gè)常見(jiàn)的組件是數(shù)字信道化接收器或信道選擇器。通道選擇器將寬帶寬分成較小的帶寬,以將目標(biāo)信號(hào)與噪聲和干擾源分開(kāi),從而可以在各個(gè)子通道中可靠地檢測(cè)低SNR和時(shí)間敏感信號(hào)。大多數(shù)數(shù)字通道化接收器由濾波器組和快速傅里葉變換(FFT)組成。

作為設(shè)計(jì)工程師,這里的挑戰(zhàn)之一是每個(gè)新的電子戰(zhàn)設(shè)計(jì)或升級(jí)通常需要開(kāi)發(fā)更復(fù)雜的通道器。這是因?yàn)樾略O(shè)計(jì)通常會(huì)帶來(lái)必要的硬件升級(jí),提供更高速的轉(zhuǎn)換器和更高的處理性能,這對(duì)于跟上不斷變化的全球威脅至關(guān)重要。為了加速通道選擇器的開(kāi)發(fā)并降低內(nèi)部研發(fā)(IRAD)成本,Altera開(kāi)發(fā)了能夠處理多GSPS轉(zhuǎn)換器輸入的超采樣率FFT IP和FIR濾波器IP核。這些 IP 核將根據(jù)各種輸入?yún)?shù)為您優(yōu)化解決方案,如圖 3 所示。

圖3.Altera 超采樣率 FFT 配置。

圖4描述了信道選擇器在一般電子戰(zhàn)系統(tǒng)框圖中的作用,其中數(shù)字化的輸入射頻(RF)寬帶信號(hào)被下變頻,并在饋入信道化接收器之前進(jìn)行數(shù)字化處理。對(duì)單個(gè)通道輸出執(zhí)行信號(hào)檢測(cè)和估計(jì),以從中立和友好信號(hào)中識(shí)別威脅。一旦識(shí)別出威脅并基于數(shù)據(jù),某些電子戰(zhàn)系統(tǒng)將通過(guò)干擾來(lái)應(yīng)對(duì)威脅。在此過(guò)程中,接收器可能會(huì)產(chǎn)生各種干擾信號(hào)。這些干擾信號(hào)可以以缺口白噪聲或再生的假反射信號(hào)(即DRFM)的形式出現(xiàn)給敵對(duì)發(fā)射器。干擾信號(hào)通過(guò)逆信道器,其作用是重建寬帶反射信號(hào)。反射信號(hào)在上變頻后發(fā)射回?cái)硨?duì)發(fā)射器。

圖4.通用電子戰(zhàn)系統(tǒng)框圖。

硬件演示

該項(xiàng)目演示了ADC接口和通道選擇器功能。信號(hào)發(fā)生器產(chǎn)生正弦音作為AD9625輸入。AD9625 ADC輸出使用行業(yè)標(biāo)準(zhǔn)FMC接口連接到Arria-V SoC開(kāi)發(fā)套件。JESD204B標(biāo)準(zhǔn)定義了各種通道配置中邏輯器件的數(shù)據(jù)速率。本演示中的JESD204B接口配置為使用8通道收發(fā)器模式,如圖5A和圖5B所示。

圖5A.AD9625通過(guò)JESD204B接口連接Altera Arria V。

圖 5B.通道選擇器JESD204B輸入和Avalon存儲(chǔ)器映射,用于Altera系統(tǒng)在環(huán)。

通過(guò)JESD204B接口接收的樣本被饋入通道選擇器IP,該IP配置為使用16根輸入線(xiàn)同時(shí)接收16個(gè)樣本(圖4中的參數(shù)M)。根據(jù)FFT點(diǎn)的數(shù)量,完整的FFT幀分為多個(gè)時(shí)隙。例如,1024 點(diǎn) FFT 需要 1024/16 = 64 個(gè)時(shí)隙才能完成。濾波器組系數(shù)和FFT處理階段根據(jù)時(shí)隙自動(dòng)切換。

Channelizer IP是使用DSP builder advanced(DSPBA)開(kāi)發(fā)的,DSPBA是Altera基于模型的設(shè)計(jì)流程工具。它使信號(hào)處理工程師能夠在 MATLAB/Simulink 環(huán)境中設(shè)計(jì)、評(píng)估和驗(yàn)證其算法。一旦算法達(dá)到最佳狀態(tài),DSPBA就會(huì)生成一個(gè)可以部署在Altera FPGA上的代碼。

通道選擇器輸出存儲(chǔ)在片上存儲(chǔ)器中,并通過(guò)Altera系統(tǒng)在環(huán)(SIL)工具進(jìn)行驗(yàn)證。SIL 使用 MATLAB API 觸發(fā)片上寄存器,開(kāi)始記錄數(shù)據(jù)可視化。一旦觸發(fā),將執(zhí)行FFT處理的單次迭代,并將結(jié)果數(shù)據(jù)存儲(chǔ)到片上SRAM中。MATLAB API 通過(guò) Altera Avalon 內(nèi)存映射將數(shù)據(jù)從 SRAM 提取到 MATLAB 主機(jī)。上傳到 MATLAB 后,樣本將繪制在屏幕上。

IP的集成是在Qsys中完成的。Qsys是Altera的集成工具,通過(guò)提供集成框架可以顯著加快開(kāi)發(fā)過(guò)程。它支持使用圖形用戶(hù)界面的分層 IP 重用和互連基礎(chǔ)設(shè)施。

創(chuàng)建Qsys項(xiàng)目以集成信道器IP和JESD204B IP。除了通道選擇器IP集成外,該項(xiàng)目還集成了控制功能,以支持ADC的SPI配置接口。

通道選擇器可以通過(guò) MATLAB 設(shè)置腳本輕松切換到不同的 FFT 尺寸。這種靈活性確保了未來(lái)的升級(jí)路徑和跨不同系統(tǒng)配置的潛在設(shè)計(jì)重用。例如,圖6顯示了SIL的4096點(diǎn)FFT輸出。

圖6.通過(guò)SIL顯示的4k-FFT通道選擇器輸出示例。

結(jié)論

下一代高速轉(zhuǎn)換器提供的解決方案可在不影響系統(tǒng)靈敏度的情況下提供更高的瞬時(shí)帶寬,并在頻率規(guī)劃方面提供更大的靈活性,或減輕前端RF條上的混頻下級(jí)。然而,在1 GHz范圍內(nèi)實(shí)現(xiàn)帶寬數(shù)據(jù)分析可能會(huì)給設(shè)計(jì)高性能系統(tǒng)帶來(lái)挑戰(zhàn)。

為了解決這個(gè)問(wèn)題,可以使用通道選擇器來(lái)分析這些寬帶寬,同時(shí)保持高性能。這些新型GSPS RF ADC與新型可配置通道選擇器IP核相結(jié)合,為下一代系統(tǒng)設(shè)計(jì)人員提供了應(yīng)對(duì)不斷變化的電子戰(zhàn)環(huán)境的更快解決方案。

審核編輯:郭婷

-

轉(zhuǎn)換器

+關(guān)注

關(guān)注

27文章

8639瀏覽量

146897 -

adc

+關(guān)注

關(guān)注

98文章

6452瀏覽量

544148 -

RF

+關(guān)注

關(guān)注

65文章

3042瀏覽量

166831

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

如何利用射頻采樣ADC來(lái)破解寬帶難題?

RF采樣ADC 可對(duì)寬帶寬進(jìn)行數(shù)字化處理

RF采樣ADC為系統(tǒng)設(shè)計(jì)帶來(lái)的好處

RF采樣:全新的采樣速率數(shù)據(jù)轉(zhuǎn)換器

基于射頻采樣ADC破解寬帶難題

利用采樣保持放大器和RF ADC從根本上擴(kuò)展帶寬以突破X波段頻率

RF采樣ADC簡(jiǎn)化并加速設(shè)計(jì)

RF采樣ADC給系統(tǒng)設(shè)計(jì)帶來(lái)的好處介紹

RF采樣ADC的優(yōu)勢(shì)

利用FPGA控制ADC0809采樣電壓

ADC08DJ5200RF射頻采樣千兆采樣模數(shù)轉(zhuǎn)換器(ADC)數(shù)據(jù)表

ADC12D1800RF一款RF采樣GSPS ADC數(shù)據(jù)表

ADC12D500RF, ADC12D800RF 12位1.6/1.0 GSPS RF采樣ADC數(shù)據(jù)表

ADC12D1x00RF 12位、3.2 GSPS和2 GSPS RF采樣ADC數(shù)據(jù)表

基于TI射頻直接采樣ADC(ADC32RF80)的RX鏈路設(shè)計(jì)

利用RF采樣ADC解決寬帶難題

利用RF采樣ADC解決寬帶難題

評(píng)論