本文提出了一種緊湊、精確、低于1V、低阻抗、低壓差帶隙基準電壓源。這里介紹的電路概念是一個低于1V(設計示例中為0.9V)的帶隙基準電壓源,可以從高于V的位開始設置是,具體取決于工作溫度范圍,并達到正常帶隙電壓。該電路理念在90nm BiCMOS技術中實現。仿真結果表明,在200°C的溫度范圍內,所提電路在線路和負載調整率上可以實現15ppm。該內核可以在CMOS工藝中使用寄生pnp器件實現。

基準電壓源是大多數模擬電路中的關鍵構建模塊。在電池供電的便攜式應用中,最小系統電壓不斷降低,以延長電池壽命。模擬電路所需的理論最小電源是一個閾值加上電流源的飽和電壓,通常為VDSSAT.對于BiCMOS工藝或具有寄生pnp晶體管的CMOS工藝,最小工作電壓將為V是+ VDSSAT,假設CMOS VT閾值低于V是.

在本文中,介紹了一種新的帶隙基準內核,可以設置在略高于V之間的任何位置是到 VBG.最低輸出電壓(V0) 取決于需要覆蓋的最低溫度。下面的設計示例將表明,在-50°C至+150°C范圍內,這些配置接近理論最小工作電壓50mV至100mV。

低于1V的基準電壓源以前以不同的方式實現。工程師已記錄1–5電流模式下的各種架構,其中產生CTAT和PTAT電流并將其一起添加到電阻器中以產生基準電壓。但是,它被顯示6由于電流鏡,這些配置具有高噪聲。由于反射鏡不匹配,與普通帶隙配置相比,使用電流鏡很難獲得相同的精度。無需調整,設計良好的帶隙電路通常可以在-40°C至+125°C范圍內實現3%至5%的6δ精度。 即使具有相當高的過載,當前的反射鏡也很難達到這種精度水平。如果增加過驅以獲得更好的匹配,則也會增加必要的裕量,如VDSSAT增加。

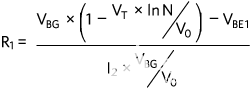

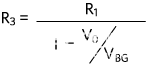

還有另一種方式6, 7以產生低于 1V 的基準電壓源。基準電壓由公式1表示:

V裁判= 千伏是+ δv是= 千伏是+ VTln(N)

其中N是兩個發射器的面積之比。

如公式1所示,電壓設定在100mV至200mV范圍內。2006年的演講7給出的設計示例為 N = 10, V裁判= 130mV。

不需要靠近地電位的基準電壓,因為下一級的噪聲和失調將成比例地大于基準電壓。因此,整體精度會下降。本文介紹了一種解決上述問題并提供卓越性能的新方法。例如,根據負載的不同,采用1.0V或更低電源時可以產生0.9V基準。

用于低于1V基準的新建議內核

具有 npns 的 BiCMOS 工藝

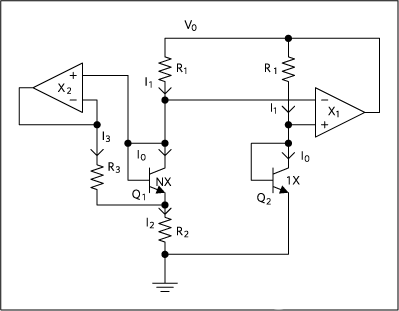

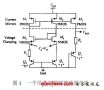

圖 1 顯示了建議的內核。

圖1.新的帶隙內核。

在數學上,可以證明 V0變為帶隙電壓的縮放版本,VBG:

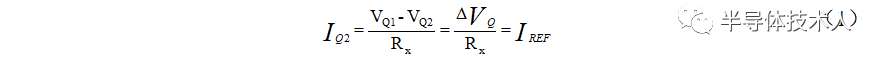

我2×·2= δv是= VTln(N)

V0= (1 - R1/R3) × VBG

哪里:

VBG= (VBG1+ VT× lnN × R3/R2× ((R1( 12)/(R3, s1))

電源裕量要求為 V0+ VDSSAT,輸出為低阻抗。

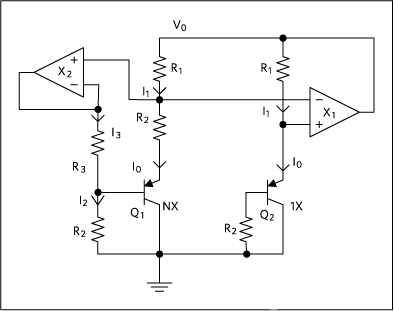

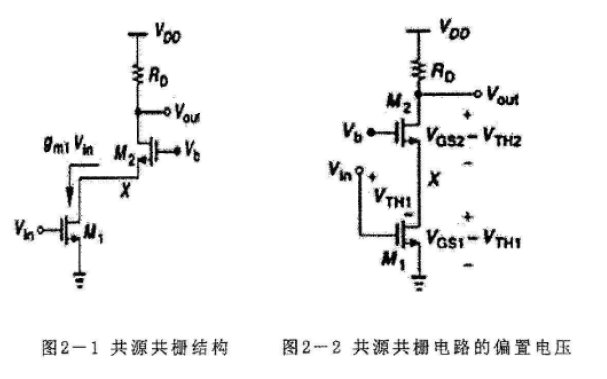

一種具有寄生pnps的CMOS工藝

可能的 pnp 版本如圖 2 所示。

圖2.CMOS 進程的 pnp 版本。

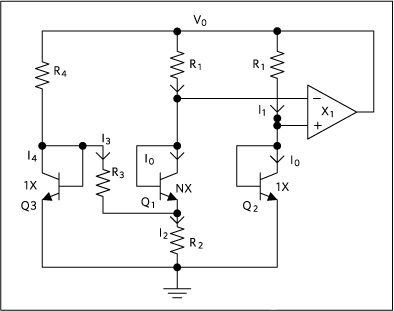

包含仿真結果的設計示例

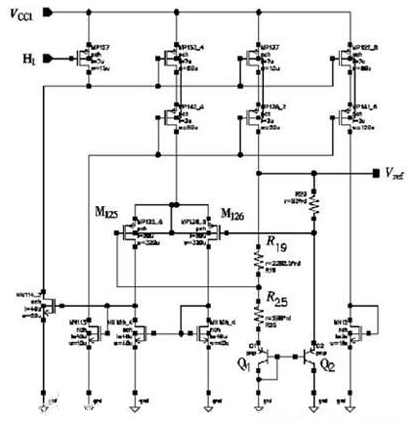

圖 1 的簡化版本如圖 3 所示;它節省了一個運算放大器(X2)。我3電流可以通過添加兩個電阻和Q來產生3.在這種情況下,我4可以設置為 I0在室溫下通過選擇合適的R4,大約等于R1/2.在其他溫度下,I4將不等于 I0,這將引入錯誤項。但自從 V是是 I 的一個非常弱的函數0,因此,誤差可以忽略不計。參見圖 4。

圖3.擬議的 npn 核心的簡化版本。

作為該內核的設計示例,V0= 0.9V選擇。

對于低功耗應用,靜態電流(IQ) 的目標范圍為 μA。根據圖 3 中的配置,我們有三個變量,R1, R2和 R3和兩個方程(公式 3 和公式 4),由 V 定義0和 VBG.因此,選擇I2是為了得到另一個方程,以得出所有三個電阻值。

由公式3:

R2= (VT× lnN)/I2

從公式4和5:

沒有單獨的旋鈕來單獨控制輸出電壓及其TC。以下是將電路微調至零TC點并獲得所需輸出電壓的過程。

找到確切的 VBE1仿真中的電壓。

查找 VBG通過調整 R2直到 V0為零 TC。現在按照以下過程操作:增加 R2如果 V0TC 呈陽性;降低 R2如果 V0TC 呈陰性。注意零 TC V 的值0,則:

VBG= V0/(1 - R1/R3)

使用新的 V 重新計算 R1、R2 和 R3BG和 V是值。

五BG= 1.203V

VBE1= 0.58V

I2= 1.0μA

N = 8

R4= 1/2R1= 206kΩ。

最終計算出的設計參數如表1所示:

| °C | -55 | 25 | 150 |

| VBE1 | 0.74 | 0.58 | 0.33 |

| VBG | 1.203 | 1.203 | 1.203 |

| VT | 0.019 | 0.026 | 0.036906 |

| 我2 | 7.32E-07 | 1.00E-06 | 1.42E-06 |

| 我3 | 4.52E-07 | 3.55E-07 | 2.02E-07 |

| 我0 | 2.79E-07 | 6.45E-07 | 1.22E-06 |

| 我1 | 2.79E-07 | 6.45E-07 | 1.22E-06 |

| R1 | 4.120E+05 | 4.120E+05 | 4.120E+05 |

| R2 | 5.407E+04 | 5.407E+04 | 5.407E+04 |

|

R3 R4 |

1.636E+06 2.060E+05 |

1.636E+06 2.060E+05 |

1.636E+06 2.060E+05 |

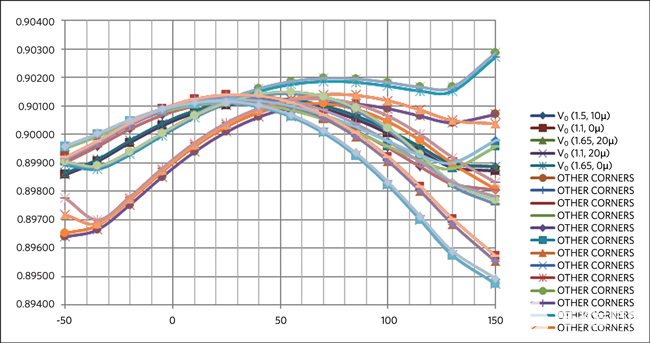

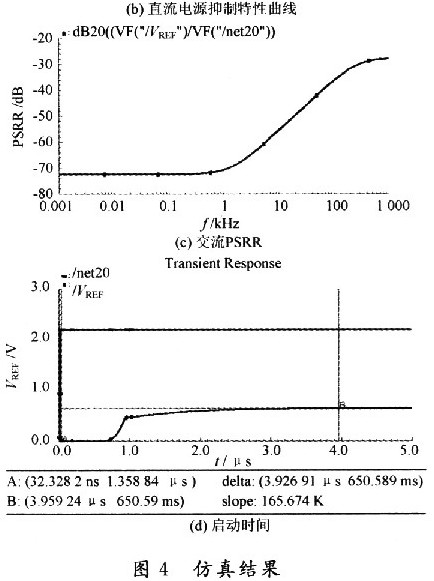

在采用晶體管電路的90nm BiCMOS工藝中實現圖3,仿真結果如圖4所示。典型情況為:電源電壓=1.5V;輸出負載 = 10μA;具有線路和負載組合的所有工藝轉角(雙極性、CMOS、電阻器、電容器),電源電壓 = (V0+ 0.1V)和1.65V;輸出負載 = 0μA 和 20μA。該電路具有溫度補償和0.1% LSB調整。結果表明,V0保持在 2.6mV 以內,在 -50°C 至 +150°C 范圍內小于 ±0.15%,或在整個線路和負載范圍內小于 15ppm。通過工藝變化和0.1%LSB調整,該帶隙基準電壓源可在200°C溫度范圍內實現±0.45%的精度。

圖4.NPN巖心仿真結果.

性能比較

表 2 將建議內核的性能與現有設計進行了比較:

| 擬議的核心 | 參考文獻 5 | 參考文獻3 | 參考文獻 6 | |

|---|---|---|---|---|

| 技術/米 |

90n BiCMOS |

500n CMOS |

600n CMOS |

500n BiCMOS |

| VDD/V | 1-1.65* | 0.93-5 | 0.98-1.5 | 1 向上 |

| V裁判.mw | 900 | 228 | 603 | 190.9 |

| 總電偶/千米 | 15 | 34 | 34.7 | 11 |

| 我Q/微安 | 6 | 28 | 18 | 20 |

|

PSRR/dB @100Hz @10kHz @1MHz |

-84 -62.2 -28.6 |

-58 – -12 |

– -44 – |

– |

| 噪聲/(nV/√Hz) @100Hz | 1573 | 200 | – | 40 |

| 面積/毫米2 | 0.023** | 0.0464 | 0.24 | 0.4 |

|

*它使用1.65V設備,因此最大電壓為1.65V。如果使用4.5V器件,它可以達到4.5V。 **模具尺寸基于將所有組件放置在清潔DRC的相應孔中。 |

||||

結論

本文介紹了一種在低壓差和低阻抗配置中創建緊湊、低于1V帶隙基準的優雅方法。該解決方案在負載、線路調整率和溫度變化方面具有約20ppm的卓越精度。凈空要求接近理論最小值。芯片尺寸與傳統帶隙基準相當,具有另外三個元件(2個電阻和1個npn)。這種設計很小,可以增強電路在較低電池電壓下工作,這對便攜式設計是有益的,甚至至關重要。

審核編輯:郭婷

-

電源

+關注

關注

184文章

17579瀏覽量

249483 -

發射器

+關注

關注

6文章

843瀏覽量

53399 -

電壓源

+關注

關注

1文章

410瀏覽量

32713

發布評論請先 登錄

相關推薦

高電源抑制的帶隙基準源設計方案

基于LDO穩壓器的帶隙基準電壓源設計

AD1580精密帶隙基準的中文資料

CMOS帶隙基準電壓源曲率校正方法

基于CMOS工藝設計低溫漂高PSRR帶隙基準源

在低壓差和低阻抗配置中創建緊湊、低于1V帶隙基準的電源方法

在低壓差和低阻抗配置中創建緊湊、低于1V帶隙基準的電源方法

評論