DS1624的2線時序規格與I2C不同。本應用筆記詳細介紹了其中的區別。SDA不由DS1624內部保持。總線主站有責任保持SDA,直到SCL的下降沿完成。

介紹

本應用筆記詳細介紹了DS1624通信時序與I2C規格之間的差異。在I2C下,允許SCL和SDA線路同時轉換,因為SDA被從器件在內部延遲至少300ns。DS1624不會延遲相對于SCL的SDA信號,因此總線主機必須將SDA保持在正確的邏輯狀態,直到SCL完全轉換到邏輯低電平,以防止錯誤生成START或STOP操作。

適當的時機

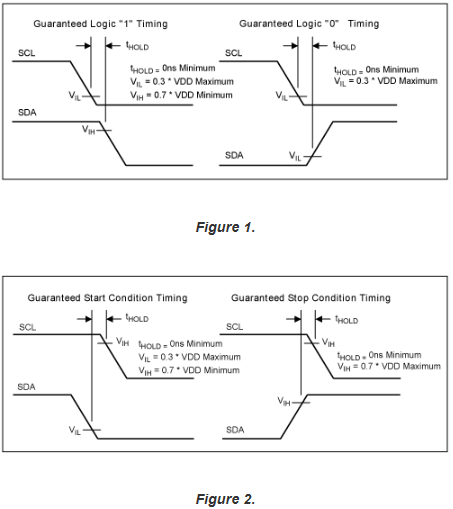

DS1624的SDA線相對于SCL沒有內部延遲。因此,SDA邏輯電平必須保持在DS1624外部,直到寫入數據時SCL轉換到邏輯低電平;否則,可能會識別啟動或停止條件。在2線總線上寫入邏輯“1”時,SCL必須達到保證邏輯低閾值V伊利諾伊州(0.3 x VDD 最大值),SDA 轉換到保證邏輯高閾值 V 以下之前IH(最小 0.7 x VDD)。寫入邏輯“0”時,SCL 必須達到 V伊利諾伊州在 SDA 轉換到 V 以上之前伊利諾伊州.生成啟動條件時,SDA 必須達到 V伊利諾伊州在 SCL 過渡到 V 以下之前IH.生成停止條件時,SDA 必須達到 VIH在 SCL 過渡到 V 以下之前IH.兩個 V伊利諾伊州和 VIH關卡在每個設備上都經過生產測試。這保證了在整個電壓和溫度范圍內(包括器件制造公差)使用此時序的正常運行。

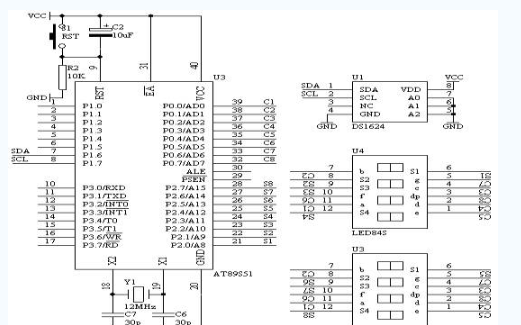

圖1.

圖2.

總結

DS1624的時序和I2C規格存在差異。DS1624不會在內部延遲SDA相對于SCL。因此,系統主機需要在 SCL 的下降沿期間維護 SDA,以防止邏輯“1”被解釋為 START 條件,而邏輯“0”被解釋為 STOP 條件。

審核編輯:郭婷

-

總線

+關注

關注

10文章

2869瀏覽量

87995 -

時序

+關注

關注

5文章

386瀏覽量

37288 -

SCL

+關注

關注

1文章

239瀏覽量

17040 -

Start

+關注

關注

0文章

73瀏覽量

10249

發布評論請先 登錄

相關推薦

帶有存儲器功能的數字溫度計-DS1624技術應用

請問大神我的ds1624程序芯片為什么不行

基于數字溫度計和256字節的E2存儲器組成的DS1624

DS1624 pdf datasheet (digital

帶有存儲器功能的數字溫度計-DS1624技術應用

美信推出DS1624數字溫度計

DS1624數字溫度計的資料簡介和應用源代碼概述

DS1624+ DS1624+ - (Maxim Integrated) - 溫度傳感器 - 模擬和數字輸出

DS1624 DS1624 - (Maxim Integrated) - 溫度傳感器 - 模擬和數字輸出

DS1624S DS1624S - (Maxim Integrated) - 溫度傳感器 - 模擬和數字輸出

DS1624通信時序與I2C規格之間的差異

DS1624通信時序與I2C規格之間的差異

評論