使用高頻開關(guān)穩(wěn)壓器時(shí),汽車電源的良好PCB布局將提供干凈的輸出電源,并節(jié)省調(diào)試電磁干擾(EMI)室中輻射問(wèn)題的時(shí)間。本應(yīng)用筆記解釋了如何布局MAX16903/MAX16904開關(guān)穩(wěn)壓器,以最大限度地提高性能并降低輻射。

介紹

當(dāng)使用MAX16903/MAX16904等高頻開關(guān)穩(wěn)壓器時(shí),良好的汽車電源PCB布局將提供干凈的輸出電源,并節(jié)省調(diào)試電磁干擾(EMI)室中輻射問(wèn)題的時(shí)間。本應(yīng)用筆記以MAX16903和MAX16904為例,概述了電路的一些關(guān)鍵設(shè)計(jì)問(wèn)題,優(yōu)化布局最有利。

一般布局指南

最小化輸入電容 (C3)、電感 (L1) 和輸出電容 (C2) 的走線環(huán)路面積。

將偏置輸出電容 (C4) 盡可能靠近引腳 13 (BIAS) 和引腳 14 (GND),引腳和電容器之間不要有任何過(guò)孔。這是IC的模擬電源;此連接上的任何電感都會(huì)增加偏置電源上的噪聲,進(jìn)而增加LX輸出的抖動(dòng)。

較短的跡線比較寬的跡線更好。

優(yōu)化交流-直流電流路徑

為了最大限度地降低輻射,MAX16903/MAX16904無(wú)源元件的布局至關(guān)重要。存在電流階躍變化的路徑被視為交流電流路徑,可以通過(guò)消除電流在開關(guān)周期的ON和OFF部分流動(dòng)的路徑來(lái)查看它們。在ON和OFF周期內(nèi)有電流流過(guò)的路徑被視為直流電流路徑。

交流電流路徑

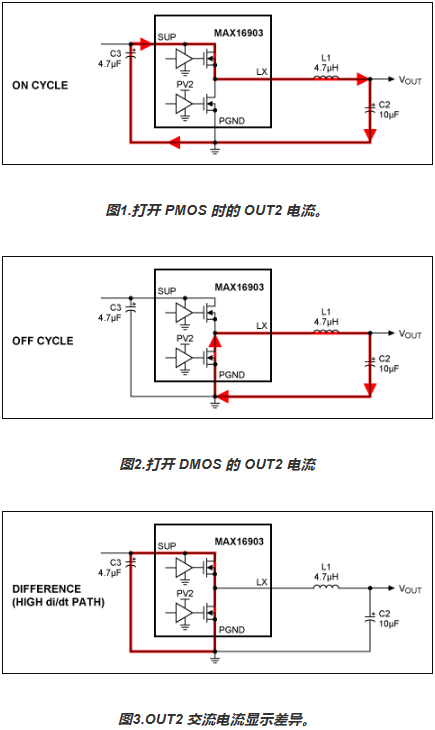

MAX16903同步DC-DC轉(zhuǎn)換器在開關(guān)電流路徑中直接具有三個(gè)無(wú)源元件(C2、C3和L1)。這三個(gè)組件對(duì)排放和設(shè)備性能的影響最大。圖1和圖2顯示了ON和OFF周期期間的開關(guān)電流路徑;圖3顯示了di/dt最高的兩條電流路徑之間的差異。優(yōu)化組件 C3 的布局是最高優(yōu)先級(jí),其次是針對(duì) L1 和 C2 進(jìn)行優(yōu)化。

升壓交流電流路徑

MAX16903/MAX16904 DC-DC轉(zhuǎn)換器采用高邊DMOS器件,要求LX引腳(DMOS的源極)上方提供5V電源電壓。為了產(chǎn)生該電壓,在 LX 和 BST 引腳之間連接了一個(gè)升壓電容器(圖 4)。在DMOS的關(guān)斷周期內(nèi),升壓電容(C1)由5V BIAS穩(wěn)壓器充電。偏置輸出也用于為誤差放大器供電。因此,BIAS必須盡可能保持安靜,以消除對(duì)誤差放大器電路產(chǎn)生負(fù)面影響的多余噪聲。實(shí)現(xiàn)此目的的最佳方法是將C4與MAX16903/MAX16904連接之間的電感降至最低。因此,將C4放置在盡可能靠近引腳14(GND)和引腳13(偏置)的位置,而不增加任何過(guò)孔。

圖4.升壓電容器交流電流。

擴(kuò)頻

當(dāng)良好的布局不足以通過(guò)客戶要求的輻射測(cè)試時(shí),可以訂購(gòu)啟用擴(kuò)頻時(shí)鐘的MAX16903/MAX16904。與標(biāo)準(zhǔn)版本相比,支持?jǐn)U頻的器件可將FM頻段噪聲降低15dB。有關(guān)如何訂購(gòu)支持?jǐn)U頻的版本的信息,請(qǐng)參見(jiàn)數(shù)據(jù)手冊(cè)。

示例:使用 TSSOP 封裝的兩層 PCB 布局

圖 5 和圖 6 顯示了使用上述指南的兩層布局示例。

圖5.使用 TSSOP 封裝的兩層 PCB 布局示例 — 頂層。

圖6.使用 TSSOP 封裝的兩層 PCB 布局示例 — 底層。

示例:使用 TDFN 封裝的兩層 PCB 布局

圖 7 和圖 8 顯示了使用上述指南的兩層布局示例。

圖7.使用 TDFN 封裝的兩層 PCB 布局示例 — 頂層。

圖8.使用 TDFN 封裝的兩層 PCB 布局示例 — 底層。

主電源濾波

主電源上的濾波也非常重要,因?yàn)檫@是在離開模塊之前可以減少傳導(dǎo)輻射的最后一點(diǎn)。對(duì)于MAX16903等高頻開關(guān)穩(wěn)壓器,F(xiàn)M無(wú)線電頻段(76MHz至108MHz)通常出現(xiàn)傳導(dǎo)輻射問(wèn)題。為了減少這些輻射,請(qǐng)?jiān)诖祟l率范圍內(nèi)添加具有高阻抗的鐵氧體磁珠和/或自諧振頻率高于108MHz的電感器。

結(jié)論

正確布局MAX16903開關(guān)穩(wěn)壓器的關(guān)鍵無(wú)源元件(圖9)將有助于最大限度地降低源頭的噪聲和輻射。這將在項(xiàng)目的資格認(rèn)證階段節(jié)省寶貴的時(shí)間和精力。

| 指定 | 數(shù)量 | 描述 |

| C1 | 1 | 0.1μF、10V ±10% X7R 0402 陶瓷電容器 |

| C2 | 1 | 10μF、10V ±10% X7R 1206 陶瓷電容器 |

| C3 | 1 | 4.7μF、50V ±10% X7R 1210 陶瓷電容器 |

| C4 | 1 | 2.2μF、10V ±10% X7R 0805 陶瓷電容器 |

| R1、R2 | 1 | 20kΩ ±1% 0402 電阻 |

| L1 | 1 | LPS3015-472MLB 4.7μH 電感器 |

| U1 | 1 | MAX16903/MAX16904低I電平Q直流-直流轉(zhuǎn)換器 |

圖9.用于PCB布局的原理圖。

審核編輯:郭婷

-

電源

+關(guān)注

關(guān)注

184文章

17605瀏覽量

249558 -

穩(wěn)壓器

+關(guān)注

關(guān)注

24文章

4218瀏覽量

93642 -

emi

+關(guān)注

關(guān)注

53文章

3583瀏覽量

127376

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

通過(guò)精心的IF信號(hào)鏈設(shè)計(jì)最大限度地提高16位 105Msps ADC的性能

如何最大限度地減少DUT上的電流負(fù)載?

機(jī)器監(jiān)測(cè):通過(guò)性能測(cè)量,最大限度提高生產(chǎn)質(zhì)量

Plunify推出Kabuto_可最大限度地減少和消除性能錯(cuò)誤

最大限度提高∑-? ADC驅(qū)動(dòng)器的性能

布局指南可最大限度地提高汽車電源性能并減少排放

布局指南可最大限度地提高汽車電源性能并減少排放

評(píng)論