本應用筆記解釋了輸入端相同值電阻的不同容差如何改變全差分ADC的THD性能。電阻器的成本隨著容差每降低一次而顯著變化

概述

MAX11905為20位、全差分SAR模數轉換器(ADC),采樣速率為1.6Msps。在輸入端選擇容差最低的電阻可以實現最佳的THD性能。但是,如果最低公差不具有成本效益怎么辦?如果選擇更高容差的電阻,THD是否合理?為了回答這些問題,我們將進行設計測試,并在本應用筆記中注明研究結果。

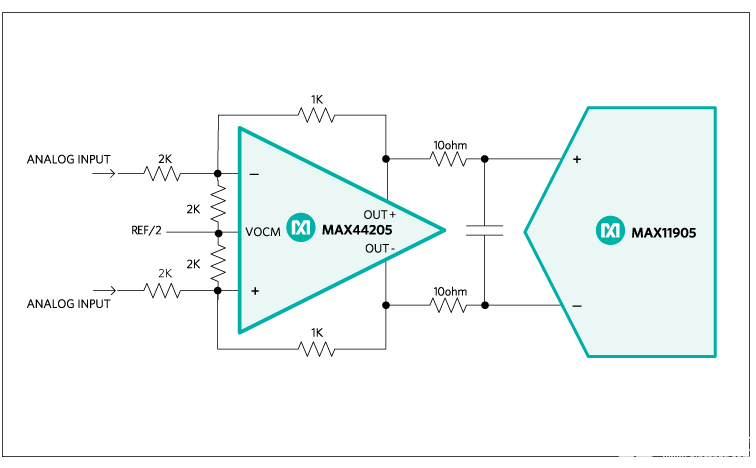

模擬前端(AFE)由半增益級組成,采用MAX44205差分放大器。差分放大器使用6個電阻,MAX11905輸入端需要另外兩個電阻。圖1顯示了ADC的輸入電路。通過改變八個電阻的容差,我們可以看到THD的變化。

圖1.模數轉換器輸入電路。

模擬輸入和ADC的測試條件

表1和表2顯示了測試設計中的電源和基準電壓源。

表 1.MAX11905電壓電源和基準輸入

| MAX11905電源 | 電壓 (V) |

|---|---|

| AVDD | 1.8 |

| OVDD | 3.3 |

| REFVDD | 3.3 |

| REFIN | 3.0 |

表 2.MAX44205電壓電源

| MAX44205電源 | 電壓 (V) |

|---|---|

| VS+ | +5 |

| VS- | -5 |

MAX44205的模擬輸入端施加接近滿量程的10kHz正弦波輸入。我們以1.5Msps的采樣率收集了32,768個樣本。設備和系統設置為相干采樣,以獲得THD結果。

結果

表3顯示了電阻測試容差的THD。表中還包括每個電阻的成本乘數,使用±5%作為基準容差。

表 3.不同電阻容差下的 THD 性能

| 電阻容差 (%) | 總諧波失真 (分貝) | 成本因素 |

|---|---|---|

| ±5(基礎) | -108 | x 1 |

| ±1 | -113 | x 1.5 |

| ±0.1 | -118.4 | x 25 |

| ±0.05 | -120 | x 45 |

由于AFE由8個電阻組成,因此成本乘以設計電路板上的電阻數量。如果設計需要容差為 ±0.05% 的電阻,則電阻器的成本因數為 360,而采用容差為 ±5% 的電阻器的設計中為 8。

結論

設計人員需要了解更改AFE電阻容差時所涉及的成本。預期的THD性能基于設計人員愿意花費的費用,因為每個設計都有預算。

審核編輯:郭婷

-

電阻器

+關注

關注

19文章

3690瀏覽量

61803 -

adc

+關注

關注

97文章

6300瀏覽量

542459 -

差分放大器

+關注

關注

8文章

434瀏覽量

51912

發布評論請先 登錄

相關推薦

高速差分ADC驅動器設計指南

高速差分ADC驅動器設計指南(一)

請問全差分ADC與偽差分ADC相比優勢在哪里?

AD5291/AD5292 具有業界最佳電阻容差的數字電位計

LTC2415:24位無延遲Delta Sigma ADC,帶差分輸入和差分參考數據表

LTC2410:24位無延遲Delta Sigma ADC,帶差分輸入和差分參考數據表

差分ADC中不同電阻容差對THD性能的影響

差分ADC中不同電阻容差對THD性能的影響

評論