本應用筆記提供了一個急需的高速I2C工作示例。應用筆記給出了一個應用電路,并提供了將MAXQ2000微控制器(MAXQ20內核)連接至MAX1239所需的全部固件,轉換速率為91ksps。示例固件是使用 MAX-IDE 1.0 版開發的。

MAX1239概述

MAX1239為12通道、12位、低功耗ADC,具有1.7MHz高速I2C兼容串行接口。MAX1239支持快速/標準模式(FS模式,400kHz)和高速模式(HS模式,1.7MHz),轉換速率高達94.4ksps。需要HS模式才能實現從26ksps到94.4ksps的轉換率。40ksps至94.4ksps的轉換速率需要外部時鐘模式。

硬件概述

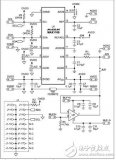

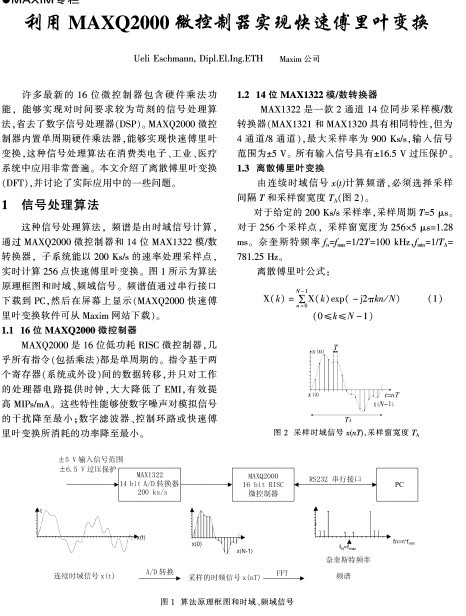

簡化的系統框圖如圖1所示。應用電路采用兩塊評估(EV)板:安裝MAX1239的MAX1238評估板(代替MAX1238)和MAXQ2000-KIT。選擇MAX1239是因為數字邏輯電壓范圍。MAXQ2000微控制器的通用輸入/輸出(GPIO)端口僅接受高達+3.3V的電壓;使用具有高速I2C的電平轉換器會使電路過于復雜。MAX1238評估板上沒有MAXQ2000,因此通過在兩塊板上連接SCL、SDA和GND將其添加到系統中。此外,將+3.3V(而不是+5V)施加到V非常重要DD在MAX1238評估板上。免費訂購MAX1239EEE或MAX1239EEE+樣品,焊接到MAX1238評估板上。修改后的MAX1238評估板原理圖如圖2所示。

圖1.簡化的系統框圖。

圖2.使用MAX1239修改MAX1238評估板原理圖。

MAX1239的引腳排列允許模擬電路與數字電路輕松隔離;模擬電路在電路板的左側組合在一起,數字電路在電路板的右側組合在一起。將兩塊板連接在一起時請記住這一點。將MAXQ2000評估板上的J2-52 (SDA)連接到MAX1238評估板上的SDA焊盤。同樣,將 J2-54 (SCL) 連接到 SCL 焊盤。兩個板的接地必須連接在一起。此外,R5和R7都必須配備2.2kΩ 5%電阻。MAX1238評估板已有47kΩ I2C上拉電阻,MAXQ2000評估板具有10kΩ I2C上拉電阻。增加R5和R7將在I2C總線上提供約1.6kΩ的上拉電阻。

MAXQ2000評估板包含一套完整的硬件、軟件、示例代碼和文檔,用于MAXQ2000設計。MAXQ2000評估板的原理圖可在數據資料中提供。

固件概述

示例固件是使用免費的MAX-IDE版本1.0開發的。下載最新版本的MAX-IDE。

主源文件是 ,它是用匯編方式編寫的,以優化 HS 模式 I2C 接口的時序。源代碼執行以下操作:hsi2c.asm

a) 初始化MAX2000的8-N-1UART,速率為115.2kbps

b) 初始化MAX1239 CONF BYTE,用于單端通道AIN0

c) 初始化MAX1239內部基準、外部時鐘和單極性操作

的設置字節 d) 初始化MAX1239的I2C HS模式 e) 在I2C HS

模式下

從MAX1239回讀12位采樣 f) 通過串行端口傳輸 12 位樣本

示例匯編程序通過對MAXQ2000的GPIO端口上的HS模式I2C接口進行位敲擊,從MAX1239采集樣本。MAXQ2000的16MHz系統時鐘允許位沖擊HS模式I2C接口工作頻率高達1.7MHz。

該文件默認為MAX1239EEE或MAX1239EEE+的從地址。必須為系列中的每個不同部件定制固件。例如,使用MAX1239KEEE、MAX1239KEEE+、MAX1239LEEE、MAX1239LEEE+、MAX1239MEEE或MAX1239MEEE+時,遵循以下兩個步驟:hsi2c.asm

編輯I2C_ADDR定義語句以反映所用器件的I2C地址。這些變量必須是實際地址的補充。例如,地址 0111 111 (r/w) 需要編碼為:

I2C_ADDR7等式 1

I2C_ADDR6 等式 0

I2C_ADDR5 等式 0

I2C_ADDR4 等式 0

I2C_ADDR3 等式 0

I2C_ADDR2 等式 0 I2C_ADDR1 等式 0

源代碼要求使用16MHz系統時鐘(MAXQ2000晶體)。

下圖顯示了本應用筆記中實現的FS模式(圖

3

)和HS模式(

圖4

)I2C幀。

圖3.FS 模式雙字節寫入操作。

圖4.HS 模式接收操作。

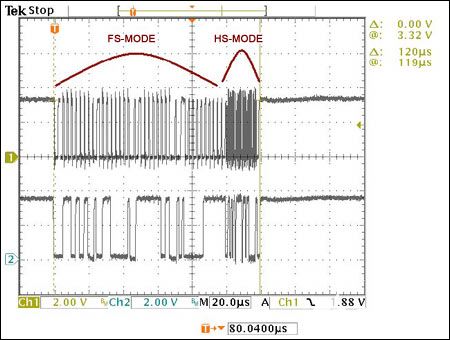

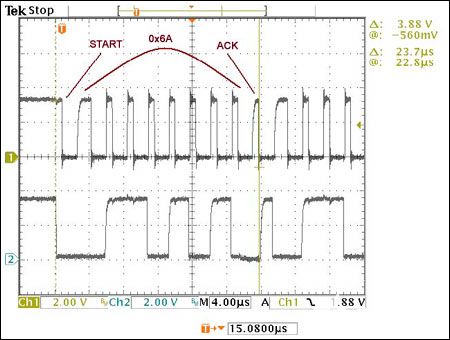

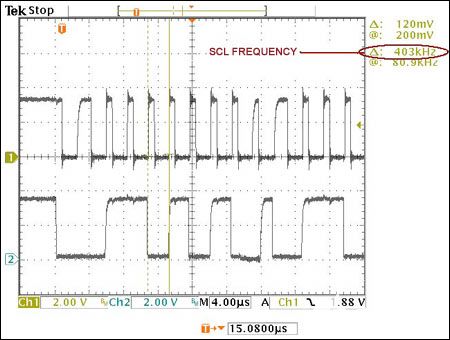

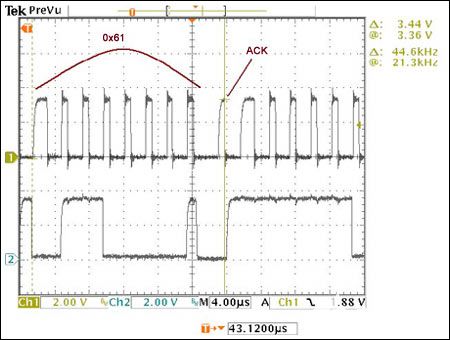

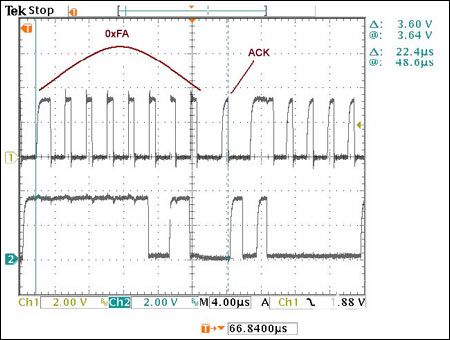

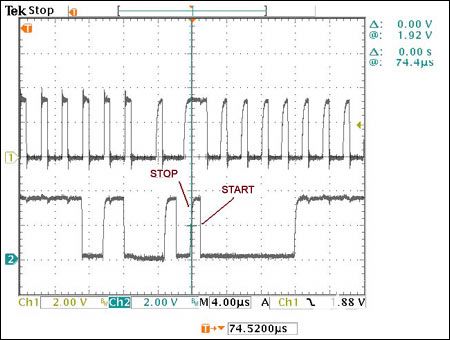

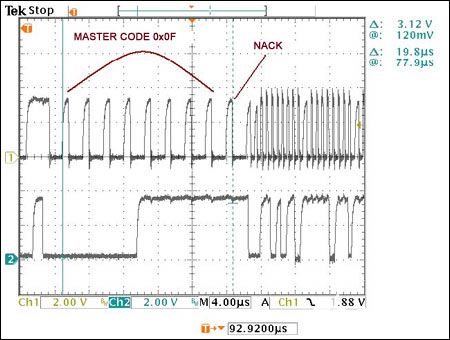

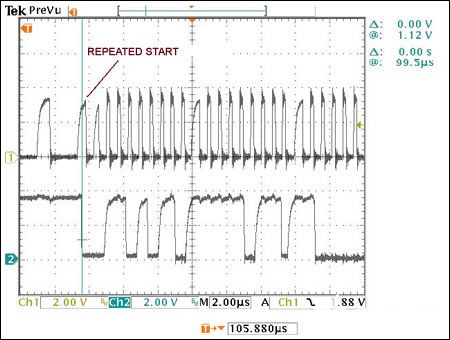

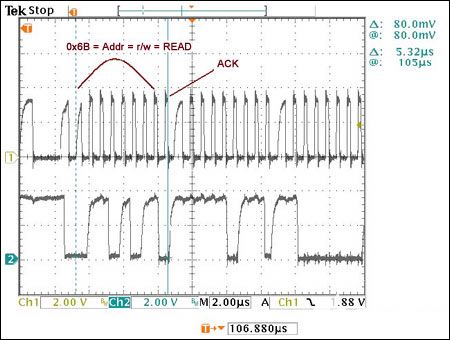

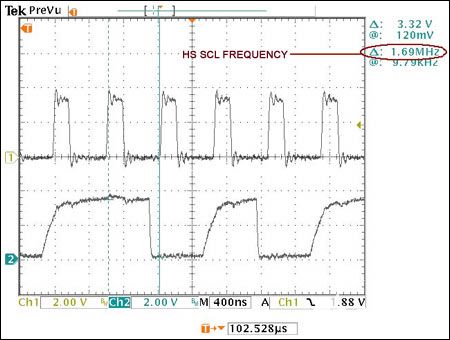

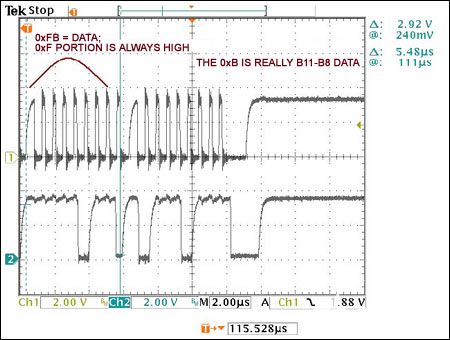

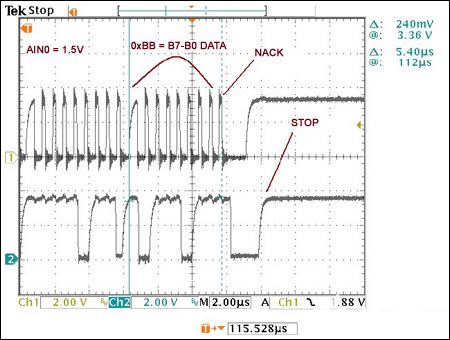

圖5至圖16是本應用筆記中實現的FS模式(圖3)和HS模式(圖4)I2C幀的示波器。通道 1 是 SCL,通道 2 是所有瞄準鏡鏡頭的 SDA。

圖5.所有I2C通信的完整幀(FS模式和HS模式操作)。

圖6.FS 模式操作,字節 1(start + Addr = 0x6A + ACK)。

圖7.FS 模式下的 SCL 時鐘頻率約為 400kHz。

圖8.FS 模式操作,字節 2(conf 字節 = 0x61 + ACK)。

圖9.FS 模式操作,字節 3(設置字節 = 0xFA + ACK)。

圖 10.FS模式操作,停止和開始下一個操作(停止和啟動)。

圖 11.FS 模式操作,字節 4(主代碼 = 0x0F + NACK)。

圖 12.HS模式操作,重復啟動。

圖 13.HS 模式操作,字節 5(Addr = 0x6B + ACK)。

圖 14.HS 模式下的 SCL 時鐘頻率約為 1.7MHz。

圖 15.HS 模式操作,字節 6(數據 = 0xFB + ACK)。

圖 16.HS 模式操作,字節 7(數據 = 0xBB + NACK + FS 停止)。

高速I2C的規范自2000年1月起就已經存在。盡管如此,目前很少有微控制器具有內部高速I2C外設。這是一個不幸的情況,因為ADC、DAC、編解碼器甚至電源等多種器件被設計為支持高速I2C接口。本應用筆記提供了一個急需的工作高速I2C示例。

審核編輯:郭婷

-

微控制器

+關注

關注

48文章

7336瀏覽量

150131 -

adc

+關注

關注

97文章

6300瀏覽量

542466 -

I2C總線

+關注

關注

0文章

14瀏覽量

2113

發布評論請先 登錄

相關推薦

采用MAXQ2000進行音頻濾波

選擇MAXQ2000微控制器和MAX1132 ADC接口的S

MAXQ2000微控制器軟件I2C驅動

利用MAXQ2000設計電壓表

采用MAXQ2000進行音頻濾波

采用MAXQ2000實現與MAX1169的高速I²

采用MAXQ2000微控制器和MAX6970 LED驅動器顯

采用MAXQ2000實現與MAX1169的高速I2C接口

使用MAX6951/MAX6950 LED顯示驅動器與MAXQ2000微控制器通信

采用MAXQ2000微控制器和MAX6970 LED驅動器顯示不同的LED排序

高速I2C用于MAX1239 ADC,采用MAXQ2000微控制器

高速I2C用于MAX1239 ADC,采用MAXQ2000微控制器

評論