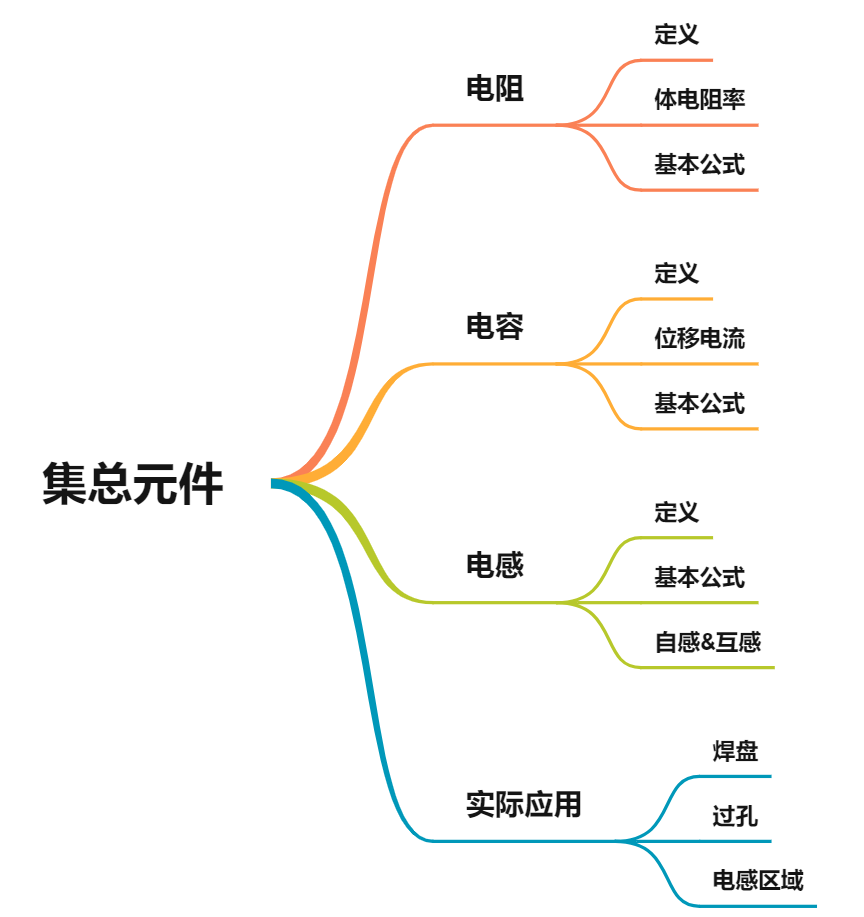

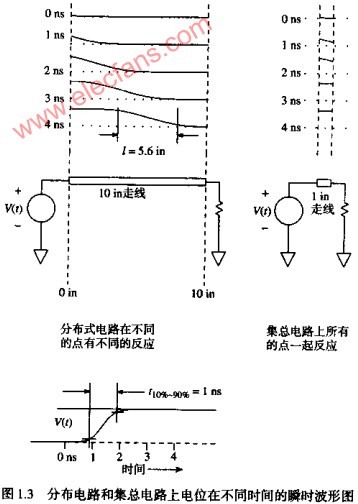

產品的設計中,研發選用很多無源器件,其中最為常用三大件:電阻、電容、電感。相對于分布元件(傳輸線),集總元件(電阻、電容、電感)是基于空間的點來做分析,信號完整性中的互連模型都是基于集總元件和分布元件來加以描述。

集總元件在硬件工程師看來,他們關注于其電氣參數:電阻器(額定功率,負荷特性,溫度系數等),電容器(額定電壓,耐壓值,頻率特性等),電感器(額定電流,品質因數等)。

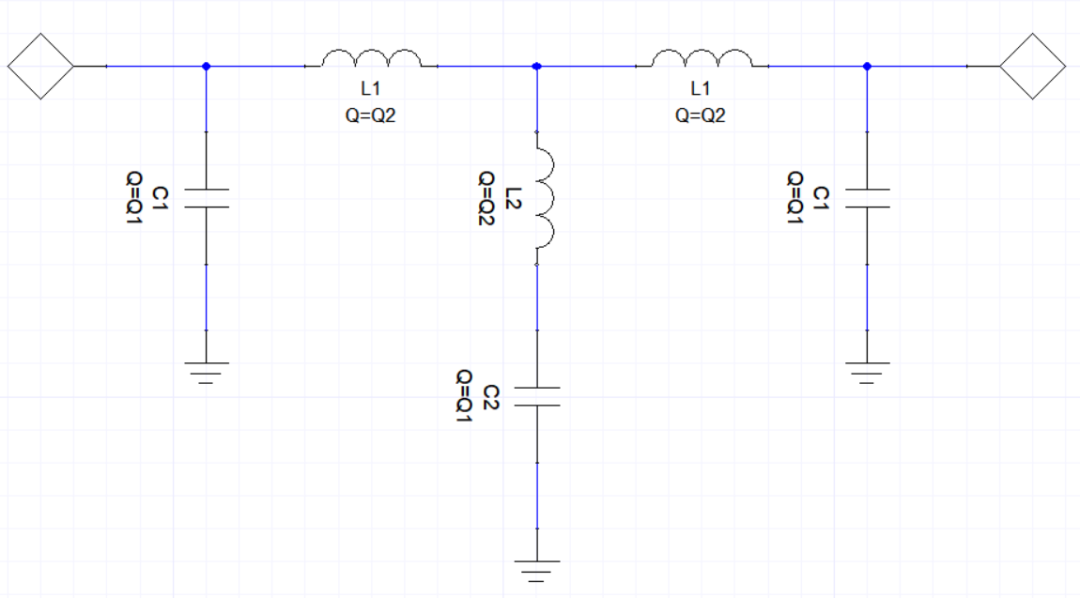

我們更關注于其對信號鏈路的影響,額外寄生參數(寄生電阻,寄生電容,寄生電感)的影響,也就是仿真中的參數提取。同時關注其能量損耗(電能變為熱能,電磁能變為熱能等),對應協議中相關損耗標準。

01

電阻

導體對電流阻礙作用的大小。

電阻(Resistor,通常用“R”表示)是一個物理量,電阻是導體本身的一種性質。不同的導體,電阻一般不同,因為導體的電阻隨長度、截面大小、溫度和導體成分的不同而改變。所以,電阻沒有一個固定值。電阻的單位是歐姆,符號為?。

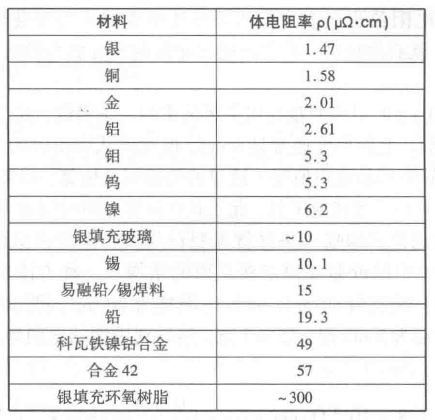

體電阻率:

不同于電阻會隨著物理尺寸(長度,寬度等)而改變,體電阻率與其無關。

體電阻率是一種材料特性,材料不同,體電阻率也不同。

體電阻率和電導率互為倒數。

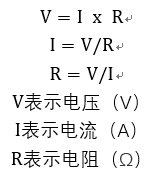

電阻作用是分壓和分流,是基于歐姆定律:

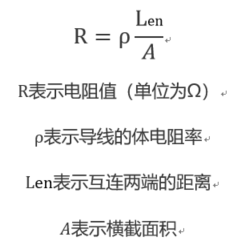

集總元件的電阻,將版圖設計中的走線(銅)兩點之間看成一個電阻,假設這段走線的橫截面恒定,近似公式:

02

電容

兩個導體,中間夾一層絕緣介質(包括空氣),給定一定電壓下的自由電荷量。

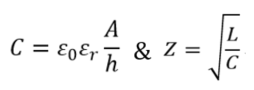

電容(Capacitance,通常用“C”表示)表示容納電荷多少的物理量。電容量的大小和幾何結構以及周邊介質的材料屬性有關。

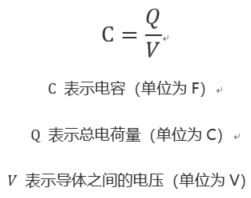

電容的基本公式:

需要注意的是:電壓值增大,異性相吸的規則,電荷量也會增大,所以比值一般保持不變。

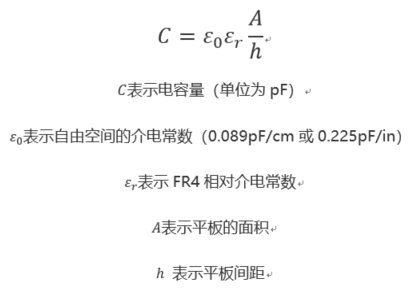

我們更多關注電容公式,如下:

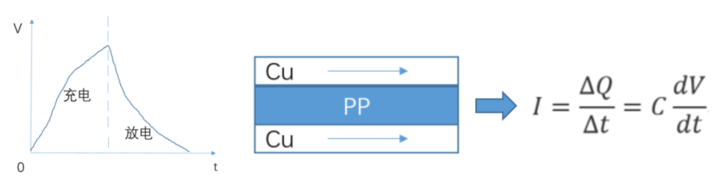

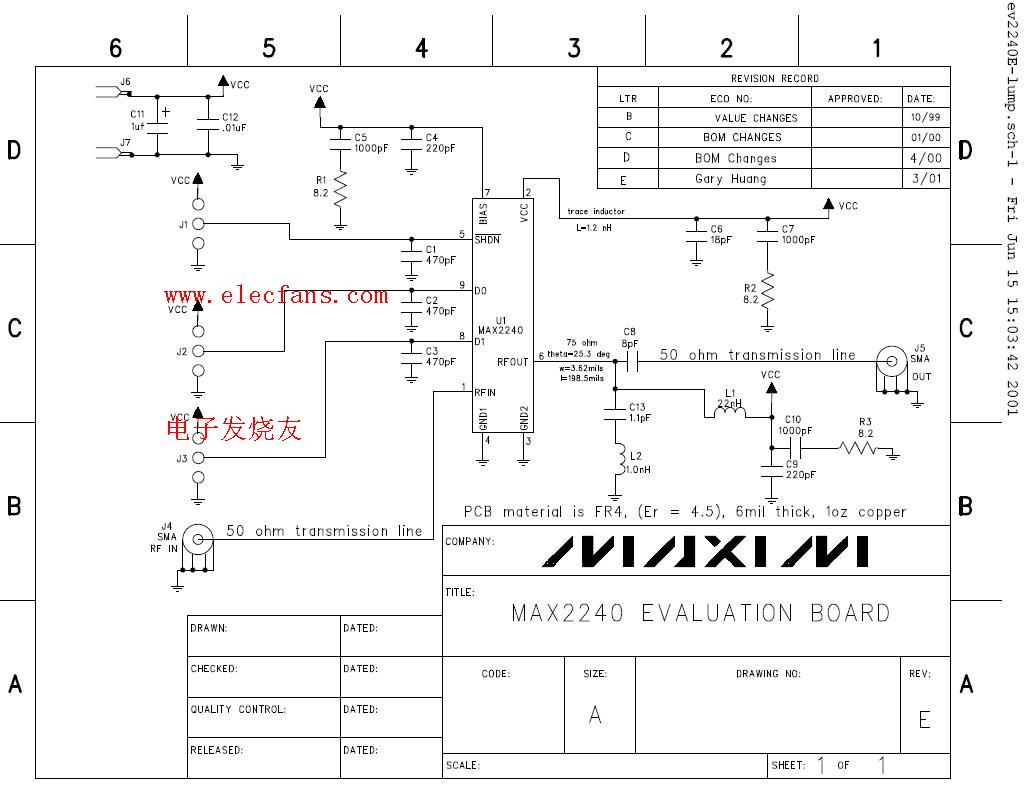

實際的版設計中,電容功能的充放電關注比較少。更多關注的是:PCB像平行電容,信號在銅線中流過,電流的變化,特別是交流信號,隨著頻率的不同,引起的串擾和信號完整性相關的問題。

需要注意的是,因為中間的絕緣介質,引出了“位移電流”的概念,這個不同于傳導電流。

電容除了電源儲能,信號濾波等作用。電源的軌道塌陷的解決之道,便是在電源和地之間多加去耦電容,降低PDN的阻抗,來保證電源壓降的需求。

03

電感

流過單位安培電流時,環繞在導體周圍的磁力線匝數。

當電流通過線圈后,在線圈中形成磁場感應,感應磁場又會產生感應電流來抵制通過線圈中的電流。

電感(Inductor,通常用“L”表示),閉合回路的一種屬性,即周圍環形磁力線圈。

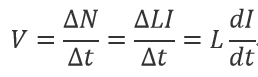

電感的電流發生變化,電感兩端就會產生電壓,也稱之為感應電動勢,該電壓產生的感應電流會阻礙原電流的變化。

這個由電流變化產生的感應電壓是我們需要避免的,它產生大多數電磁干擾源(串擾,地彈等)。

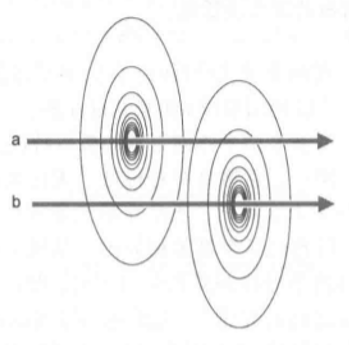

自感和互感

一個導體流過單位電流,產生自身的磁力線圈匝數,是自感。

產生在別的導體周圍的磁力線圈匝數,是互感。

04

實際應用

在實際過程中,集總元件本身不需要太多關注,更多關注于寄生電阻,寄生電容,寄生電感等。

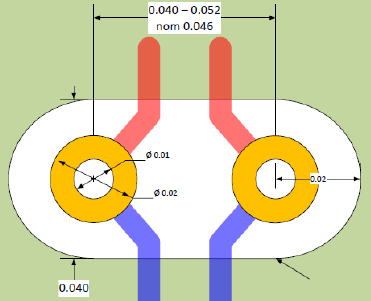

器件的引腳,亦或是焊錫絲的影響(體電阻率:銅是1.58,錫是10.1)等所引起的阻抗突變,在版圖設計中的處理,更多是對焊盤的優化。

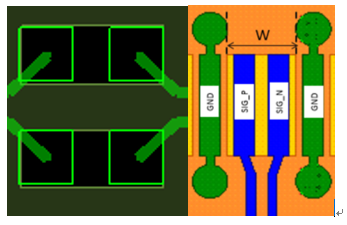

焊盤面積比走線大,面積增大,電容變大,阻抗變小。焊盤下方挖空,距離變大,電容變小,阻抗變大。通過這樣的處理,來抑制阻抗的突變,降低反射,盡量保證阻抗匹配。

版圖設計中,8Gbps以上速率的信號過孔,就是加大焊盤到銅皮的間距,來改變寄生電容的大小,同時盡量保持過孔寄生電感,來管控過孔阻抗。

當然,過孔的殘樁也是需要考慮的主要因素,這里就不做展開了。

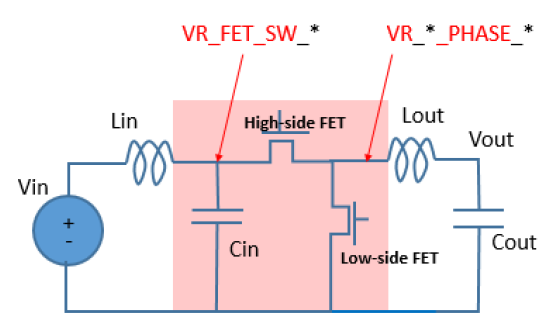

版圖設計中,設計指導也會提出HSD(高速信號差分線)走線路徑盡量遠離電感,距離上每個產品會有不同的要求。很多產品都是15mils起。

特別是開關電源的輸入,輸出電感區域,是禁布區域。

很多設計規則都是考慮其信號完整性,設計規則就是規避這些風險,規則的優化和判定正是信號完整性工程師職責所在。所以信號完整性工程不僅僅是仿真工程師,更是產品的PCB板級信號質量的優化工程師。

審核編輯:劉清

-

電阻器

+關注

關注

21文章

3763瀏覽量

62051 -

電感器

+關注

關注

20文章

2325瀏覽量

70420 -

寄生電阻

+關注

關注

1文章

20瀏覽量

2279

原文標題:集總元件的基礎知識

文章出處:【微信號:CloudBrain-TT,微信公眾號:云腦智庫】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

如何在Momentum模擬中使用集總元件

功率變換器中的功率磁性元件分布參數

數字設計基礎知識--集總與分布系統

集總元件和分布元件描述

集總元件和分布元件描述

評論