本文介紹DS3112多路復用成幀器如何從高速多路復用信號中恢復低速時鐘信號,以用于器件的三種多路復用工作模式。第一種工作模式是在M13和C位奇偶校驗模式下從DS3信號中恢復28個DS1時鐘信號。第二種模式是從E13模式下的E3信號中恢復16個E1時鐘信號。第三種模式是在G.747模式下從DS3信號中恢復21個E1時鐘信號。恢復低速時鐘時,需要注意的是,高速信號中存在的實際數據會影響恢復過程。因此,當術語“信號”單獨使用時,它指的是組合的時鐘、數據和使能信號。將術語“時鐘”、“數據”或“啟用”與信號結合使用的任何內容均指單個信號組件。

用于M13和C位奇偶校驗模式的DS1時鐘恢復

從DS3信號中恢復28個獨立的DS1時鐘是一個復雜的三階段過程。

第一級,即M23級,將DS3信號解復用為7個獨立的DS2信號。不是恢復單個DS2時鐘,而是創建DS2使能。七個DS2使能中的每一個都處于活動狀態,每個DS3幀的DS3時鐘周期為84 x 7 +(84或83)。恢復最后的84或83個DS3時鐘周期的決定基于DS2填充位控制。

第二級是M12級,它將7個DS2信號中的每一個解復用為4個DS1信號,總共28個DS1信號。與 M23 級一樣,M12 級不會恢復單個 DS1 時鐘,而是創建 DS1 使能。四個 DS1 使能中的每一個都處于活動狀態,持續 48 x 5 +(48 或 47)DS2 使能周期。恢復最后 48 或 47 DS2 使能周期的決定基于 DS1 填充位控制。

第三個也是最后一個階段是FIFO級,它實際上重新創建各個DS1時鐘。每個DS1時鐘都是通過將DS3時鐘(HRCLK)除以28或29來創建的。除數的選擇基于當前存儲在FIFO中的數據量。FIFO使用DS1使能將數據寫入FIFO,使用DS1時鐘(LRCLKx)從FIFO讀取數據。正確的DS1時鐘速率由FIFO恢復,試圖將FIFO中的數據量保持在半滿標記的中心。如果數據量超過半滿標記,則選擇“除以 28”。如果數據量低于半滿標記,則選擇“除以 29”。時鐘恢復機制的完整示意圖如圖1所示。

圖1.M13 和 C 位奇偶校驗模式。

E13 模式的 E1 時鐘恢復

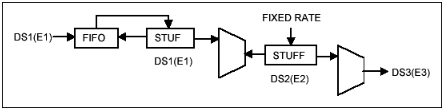

從E3信號中恢復16個單獨的E1時鐘也是一個復雜的三階段過程。

第一級是E23級,它將E3信號解復用為四個E2信號。不是恢復單個 E2 時鐘,而是創建 E2 啟用。四個 E2 使能中的每一個都處于活動狀態,每個 E3 幀的 E3 時鐘周期為 93 + 95 x 2 +(95 或 94)。恢復最后 95 或 94 個 E3 時鐘周期的決定基于 E2 填充位控件。

第二級是E12級,它將四個E2信號中的每一個解復用為四個E1信號,總共16個E1信號。與 E23 級一樣,E12 級不會恢復單個 E1 時鐘,而是創建 E1 使能。四個 E1 使能中的每一個都處于活動狀態,持續 50 + 52 x 2 +(52 或 51)個 E2 使能周期。恢復最后 52 或 51 個 E2 啟用周期的決定基于 E1 填充位控件。

第三級,也是最后一級,是FIFO級,它實際上重新創建了各個E1時鐘。每個 E1 時鐘都是通過將 E3 時鐘 (HRCLK) 除以 16 或 17 來創建的。除數的選擇基于當前存儲在FIFO中的數據量。FIFO使用E1使能設備將數據寫入FIFO,并使用E1時鐘(LRCLKx)從FIFO讀取數據。正確的E1時鐘速率由FIFO恢復,FIFO試圖將FIFO中的數據量保持在半滿標記的中心。如果數據量超過半滿標記,則選擇“除以 16”。如果數據量低于半滿標記,則選擇“除以 17”。時鐘恢復機制的完整示意圖如圖2所示。

圖2.E13 模式。

G.747 模式的 E1 時鐘恢復

從DS3信號中恢復21個獨立的E1時鐘也是一個復雜的三階段過程。

第一級是M23級,它將DS3信號解復用為7個DS2信號。不是恢復單個DS2時鐘,而是創建DS2使能。七個DS2使能中的每一個都處于活動狀態,每個DS3幀的DS3時鐘周期為84 x 7 +(84或83)。恢復最后的84或83個DS3時鐘周期的決定基于DS2填充位控制。

第二級是G.747級,它將7個DS2信號中的每一個解復用為3個E1信號,總共21個E1信號。與 M23 級一樣,G.747 級不會恢復單個 E1 時鐘,而是創建 E1 使能。三個 E1 使能中的每一個都處于活動狀態,持續 53 + 55 x 3 +(55 或 54)DS2 使能周期。恢復最后 55 或 54 DS2 使能周期的決定基于 E1 填充位控件。

第三個也是最后一個階段是FIFO階段,它實際上重新創建各個E1時鐘。每個 E1 時鐘都是通過將 DS3 時鐘 (HRCLK) 除以 21 或 22 來創建的。除數的選擇基于當前存儲在FIFO中的數據量。FIFO使用E1使能設備將數據寫入FIFO,并使用E1時鐘(LRCLKx)從FIFO讀取數據。正確的E1時鐘速率由FIFO恢復,FIFO試圖將FIFO中的數據量保持在半滿標記的中心。如果數據量超過半滿標記,則選擇“除以 21”。如果數據量低于半滿標記,則選擇“除以 22”。時鐘恢復機制的完整示意圖如圖3所示。

圖3.G.747 模式。

審核編輯:郭婷

-

fifo

+關注

關注

3文章

387瀏覽量

43561 -

時鐘

+關注

關注

10文章

1721瀏覽量

131378

發布評論請先 登錄

相關推薦

DS3 / E3 / STS成幀器設計用于多標準網絡和傳輸系統

DS3150 業內首款單端口T3/E3 LIU,集成了抖動衰

DS3112 LRCLKx Low Speed Clock

Bit Error Rate Testing the DS3

DS3112 Clock Rates and Frequen

DS3112 接口 - 電信

DS3112 DS3/E3多路復用成幀器如何恢復低速時鐘信號

DS3112 DS3/E3多路復用成幀器如何恢復低速時鐘信號

評論