數(shù)字門級(jí)電路可分為兩大類:組合邏輯和時(shí)序邏輯。鎖存器是組合邏輯和時(shí)序邏輯的一個(gè)交叉點(diǎn),在后面會(huì)作為單獨(dú)的主題處理。

組合邏輯描述了門級(jí)電路,其中邏輯塊的輸出直接反映到該塊的輸入值的組合,例如,雙輸入AND門的輸出是兩個(gè)輸入的邏輯與。如果輸入值發(fā)生變化,輸出值將反映這一變化,組合邏輯的RTL模型需要反映這種門級(jí)行為,這意味著邏輯塊的輸出必須始終反映該邏輯塊當(dāng)前輸入值的組合。

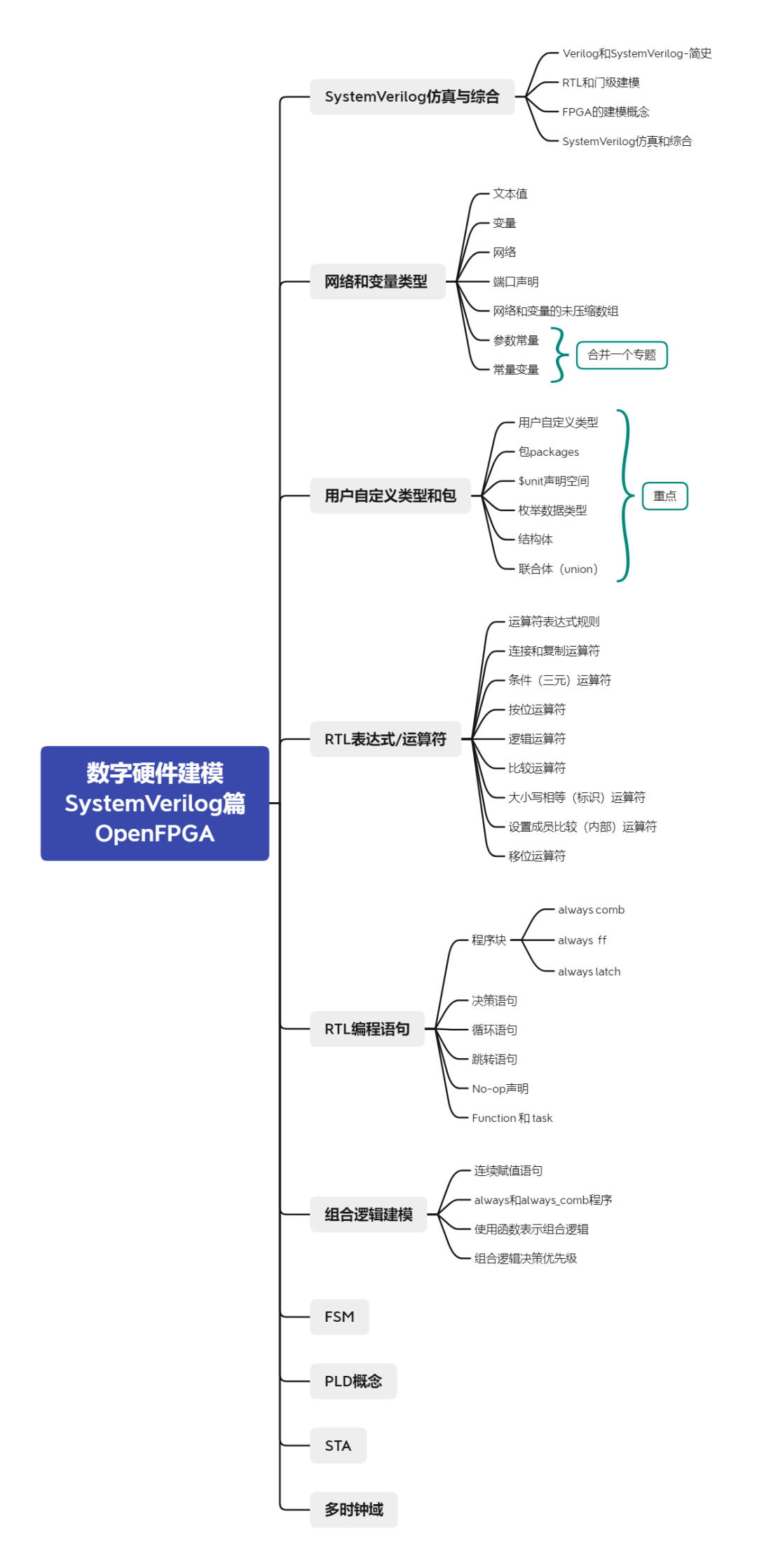

SystemVerilog有三種在可綜合RTL級(jí)別表示組合邏輯的方法:連續(xù)賦值語(yǔ)句、always程序塊和函數(shù)。接下來(lái)幾篇文章將探討每種編碼風(fēng)格,并推薦最佳實(shí)踐編碼風(fēng)格。

時(shí)序邏輯概念

時(shí)序邏輯描述了一種重要的門級(jí)電路,其中輸出反映了一個(gè)由門的內(nèi)部狀態(tài)存儲(chǔ)的值。只有特定的輸入變化,如時(shí)鐘沿,才會(huì)導(dǎo)致存儲(chǔ)的變化。對(duì)于D觸發(fā)器,時(shí)鐘輸入的特定邊沿將改變觸發(fā)器的存儲(chǔ),但D輸入值的變化并不直接改變存儲(chǔ)。相反,特定的時(shí)鐘沿會(huì)使觸發(fā)器的內(nèi)部存儲(chǔ)更新為時(shí)鐘沿的D輸入值。

時(shí)序邏輯的RTL模型需要反映這種門級(jí)行為,也就是說(shuō),邏輯塊的輸出必須在一個(gè)或多個(gè)時(shí)鐘周期內(nèi)存儲(chǔ)一個(gè)值,并且只為特定的輸入變化而更新存儲(chǔ)的值,而不是所有輸入變化。在RTL層面,一個(gè)always或always_ff過(guò)程被用來(lái)模擬這種時(shí)序行為。本系列文章主要研究:

RTL時(shí)序邏輯的綜合要求

always_ff 時(shí)序邏輯建模

時(shí)序邏輯時(shí)鐘到Q的傳播和建立/保持時(shí)間

使用非阻塞賦值來(lái)模擬時(shí)鐘到Q的傳播效應(yīng)

同步和異步復(fù)位

多個(gè)時(shí)鐘和時(shí)鐘域交叉(CDC)。

在時(shí)序邏輯RTL模型中使用單元延時(shí)

建立有限狀態(tài)機(jī)(FSM)模型

對(duì)Mealy和Moore FSM架構(gòu)進(jìn)行建模

狀態(tài)解碼器,并使用獨(dú)熱碼的獨(dú)特情況

對(duì)內(nèi)存設(shè)備進(jìn)行建模,如RAM

觸發(fā)器和寄存器的RTL模型

觸發(fā)器和寄存器被用來(lái)在一段時(shí)間內(nèi)存儲(chǔ)信息。術(shù)語(yǔ)觸發(fā)器和寄存器經(jīng)常被當(dāng)作同義詞使用,盡管它們?cè)诩虞d和復(fù)位的方式上可能存在差異。觸發(fā)器是一種存儲(chǔ)元件,在時(shí)鐘沿上改變存儲(chǔ)的狀態(tài)。各種各樣的硬件應(yīng)用都可以由觸發(fā)器構(gòu)建,如計(jì)數(shù)器、數(shù)據(jù)寄存器、控制寄存器、移位寄存器和狀態(tài)寄存器。寄存器可以由任何類型的數(shù)據(jù)存儲(chǔ)設(shè)備構(gòu)建,包括觸發(fā)器、鎖存器和RAM。大多數(shù)硬件寄存器是由觸發(fā)器建立的。

時(shí)序邏輯觸發(fā)器和寄存器的RTL模型是用一個(gè)帶有靈敏度列表的always或always_ff過(guò)程建模的,該過(guò)程使用時(shí)鐘邊沿來(lái)觸發(fā)過(guò)程的評(píng)估。一個(gè)RTL觸發(fā)器的例子是:

一般來(lái)說(shuō),RTL模型被寫(xiě)成在時(shí)鐘輸入的正邊沿觸發(fā)觸發(fā)器。所有的ASIC和FPGA器件都支持在時(shí)鐘的上升沿(正邊沿)觸發(fā)的觸發(fā)器。一些ASIC或FPGA器件還支持在時(shí)鐘的下降沿觸發(fā)的觸發(fā)器。觸發(fā)器和由觸發(fā)器組成的寄存器可以是不可復(fù)位或可復(fù)位的。復(fù)位可以是同步的,也可以是與時(shí)鐘觸發(fā)不同步的。一些觸發(fā)器也有一個(gè)異步復(fù)位輸入。

在門級(jí)設(shè)計(jì)中,有幾種類型的觸發(fā)器,例如。SR, D,JK和T觸發(fā)器。RTL模型可以從這個(gè)實(shí)現(xiàn)細(xì)節(jié)中抽象出來(lái),并被寫(xiě)成通用的觸發(fā)器。

在RTL建模中,重點(diǎn)是設(shè)計(jì)功能,而不是設(shè)計(jì)實(shí)現(xiàn)。綜合編譯器的作用是將抽象的RTL功能描述映射到具體的門級(jí)實(shí)現(xiàn)。大多數(shù)ASIC和FPGA器件使用D型觸發(fā)器,所以本文假設(shè)綜合編譯器從RTL觸發(fā)器中推斷出的觸發(fā)器類型。

RTL時(shí)序邏輯的綜合要求

當(dāng)always程序的敏感度列表包含關(guān)鍵字posedge或negedge時(shí),綜合編譯器將嘗試推斷出一個(gè)觸發(fā)器。然而,綜合編譯器還要求滿足以下額外的代碼限制,以便推斷出一個(gè)觸發(fā)器。

程序靈敏度列表必須指定時(shí)鐘的哪個(gè)邊沿觸發(fā)更新觸發(fā)器的狀態(tài)(posedge或negedge)。

靈敏度列表必須指定任何異步設(shè)置或復(fù)位信號(hào)的前緣(posedge或negedge)(同步設(shè)置或復(fù)位不在靈敏度列表中列出)。

除了時(shí)鐘、異步設(shè)置或異步復(fù)位外,靈敏度列表不能包含任何其他信號(hào),如D輸入或使能輸入。

該過(guò)程應(yīng)該在零仿真時(shí)間內(nèi)執(zhí)行。綜合編譯器會(huì)忽略#延遲,并且不允許@或等待時(shí)間控制。這條規(guī)則的一個(gè)例外是使用分配單元內(nèi)的延遲(后續(xù)詳解)。

在時(shí)序邏輯程序中賦值的變量不能被任何其他程序或連續(xù)賦值所賦值(允許在同一程序中多次賦值)。

在一個(gè)時(shí)序邏輯程序中,一個(gè)被賦值的變量不能有阻塞和非阻塞的混合賦值。例如,復(fù)位分支不能用阻塞賦值建模,而時(shí)鐘分支則用非阻塞賦值建模。

審核編輯:劉清

-

RAM

+關(guān)注

關(guān)注

8文章

1367瀏覽量

114531 -

RTL

+關(guān)注

關(guān)注

1文章

385瀏覽量

59706 -

觸發(fā)器

+關(guān)注

關(guān)注

14文章

1996瀏覽量

61052 -

時(shí)序邏輯

+關(guān)注

關(guān)注

0文章

39瀏覽量

9148 -

門級(jí)電路

+關(guān)注

關(guān)注

0文章

15瀏覽量

1955

原文標(biāo)題:數(shù)字硬件建模SystemVerilog-時(shí)序邏輯建模(1)RTL時(shí)序邏輯的綜合要求

文章出處:【微信號(hào):Open_FPGA,微信公眾號(hào):OpenFPGA】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

淺談IC設(shè)計(jì)中邏輯綜合

[啟芯工作室] 邏輯綜合 02 Design and Technology File

[啟芯工作室] 邏輯綜合 03 Design Objects

[啟芯工作室] 邏輯綜合 05 Environment Attributes

[啟芯工作室] 邏輯綜合 05-03 Environment Attributes

[啟芯工作室]邏輯綜合 06 Timing Analysis

[啟芯][公開(kāi)課]數(shù)字邏輯綜合 02 Design and Technology File

[啟芯][公開(kāi)課] 數(shù)字邏輯綜合 03 Design Objects

[啟芯][公開(kāi)課] 數(shù)字邏輯綜合 04 Timing constraints

[啟芯][公開(kāi)課] 數(shù)字邏輯綜合 04-1 Timing constraints

[啟芯][公開(kāi)課] 數(shù)字邏輯綜合 05 Environment Attributes

時(shí)序邏輯等效性的RTL設(shè)計(jì)和驗(yàn)證流程介紹

邏輯綜合與物理綜合

什么是邏輯綜合?邏輯綜合的流程有哪些?

RTL時(shí)序邏輯的綜合要求

RTL時(shí)序邏輯的綜合要求

評(píng)論