包含2-Wire總線的應用(如I2C或SMBus?)需要在上升時間、功耗和抗擾度之間進行權衡。由于這種漏極開路總線上從低到高轉換的上升時間由上拉電阻和總線電容決定,因此在添加外設、布線走線和連接器時,很難保持干凈、快速的邊沿。為了解決這些上升時間問題,本應用筆記介紹了一種上升時間加速器電路,該電路提供了一種加快上升時間、提高抗擾度和最小化功耗的簡單方法。

電路說明

在某些2-Wire總線應用中,正確尺寸的上拉電阻可提供足夠快的上升時間,以實現良好的抗噪性以及可接受的功耗。然而,具有高總線電容的大型系統或具有嚴格功率要求的便攜式系統可能需要有源電路來實現更短的漏極開路信號上升時間。

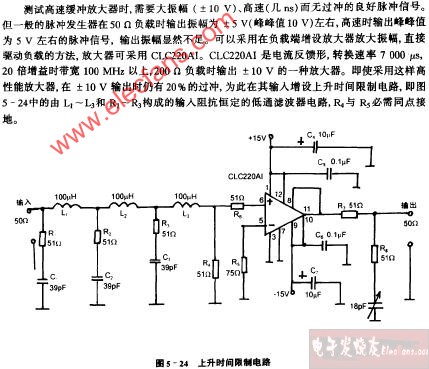

圖1所示為上升時間加速器電路,該電路利用MAX3373加快上升時間,同時提高抗擾度并降低功耗。這里使用MAX3373低壓電平轉換器,是因為它具有加速上升時間的能力,而不是作為轉換器的能力。當該IC檢測到I/O引腳上的電壓上升時,它會短暫開啟內部強上拉(pFET),從而快速為寄生總線電容充電。然后,加速器電路在短時間后被禁用,僅留下內部10kΩ上拉電阻(加上任何外部上拉電阻)來維持高邏輯電平。

圖1.MAX3373利用上升時間加速電路在快速總線上驅動高電容。

績效評估

MAX3373作為上升時間加速器的有效性使用圖2所示電路進行測試,其中分立式漏極開路FET同時驅動兩條獨立的線路。通道1由MAX3373加速,通道2端接簡單的上拉電阻和寄生電容(兩條線路的C相同)。MAX3373的有效上拉電阻僅為5kΩ,因為其輸入和輸出包括內部10kΩ上拉電阻(I/O V抄送和 I/O VL引腳)。結果顯示了110pF的良性情況(圖3)和I2C總線上允許的最大400pF(圖4)。(請注意這些圖中不同的時間尺度。

圖2.該電路用于評估MAX3373電路的上升時間、電容和時鐘速率。通道1利用MAX3373加速上升時間,而通道2的上升時間由簡單的上拉電阻和寄生電容決定。

為了判斷MAX3373電路的優勢,可以考慮2線總線常見的時鐘速度:100kHz和400kHz。在100kHz時,周期為10μs,高電平狀態僅為5μs。因此,~110pF電容和5kΩ上拉電阻(圖3)的上升時間為~1.25μs,僅為周期的12%。對于這些條件,在沒有上升時間加速的情況下,性能應該是可以接受的。

圖3.圖解MAX3373電路(通道1)與非加速電路(通道2)在5kΩ上拉、100kHz時鐘和110pF寄生電容下的上升時間。

然而,對于400pF的寄生電容,上升時間為~4μs,這是周期的40%,在許多100kHz系統中是不可接受的。在400pF系統中,使用MAX3373加快上升時間可在500ns內上升90%,僅為10μs周期的5%(圖4)。

圖4.圖解MAX3373電路(通道1)與非加速電路(通道2)在5kΩ上拉、100kHz時鐘和400pF寄生電容下的上升時間。

對于400kHz總線(在2.5μs周期內提供1.25μs的高狀態),上述5kΩ和~110pF條件提供的上升時間僅為1.25μs,這是周期的50%,通常不可接受。將電容提高到400pF會產生5μs的上升時間,這是周期的兩倍,顯然是不可接受的。然而,使用具有~110pF負載電容的MAX3373電路可提供250ns的90%上升時間,僅為2.5μs周期的10%;在400pF時,它的上升時間僅為~500ns,或周期的20%。

總結

使用MAX3373電路作為上升時間加速器是解決2線總線上升時間與時鐘問題的幾種方法之一。在某些情況下,只需降低上拉電阻即可加快上升時間。然而,MAX3373提供了一種簡單的方法來加快上升時間,同時提高抗擾度并最大限度地降低功耗。

審核編輯:郭婷

-

轉換器

+關注

關注

27文章

8639瀏覽量

146897 -

總線

+關注

關注

10文章

2869瀏覽量

87997 -

I2C總線

+關注

關注

0文章

14瀏覽量

2122

發布評論請先 登錄

相關推薦

I2C等雙線總線上升時間加速電路

上升時間加速器LTC4311相關資料下載

2線總線上升時間加速電路

淺談振蕩上升時間及影響

上升時間加速器LTC4311的作用及性能分析

LTC4311 - 400kHz 上升時間加速器改善了重負載 I<sup>2</sup>C/SMBus 系統可靠性

信號頻率和上升時間的關系

TCA39416具有上升時間加速器的超低電壓I3C轉換器數據表

具有上升時間加速器的TCA9416超低電壓I2C轉換器數據表

用于2-Wire總線應用的上升時間加速器電路

用于2-Wire總線應用的上升時間加速器電路

評論