低壓差分信號(LVDS)已廣泛用于高速數字信號互連。一種流行的總線拓撲將多個LVDS接收器連接到由LVDS發送器驅動的100Ω差分雙絞線,稱為多點LVDS總線。交流耦合方法通常用于多點總線。本應用筆記探討了多點總線的傳統故障安全偏置電路,并確定了其最常見的弱點是元件變化。本文提出了一種用于故障安全偏置的替代魯棒電路結構。

LVDS信令廣泛用于高速數字信號互連,特別是在數字視頻和相機信號中。多點LVDS總線是常用的總線拓撲之一,它將多個LVDS接收器連接到由LVDS發送器驅動的100Ω差分雙絞線。這種總線結構是形成LVDS信號路由多路復用的便捷方法。此外,更多的LVDS互連使用交流耦合,以避免接地電平偏移和共模干擾。

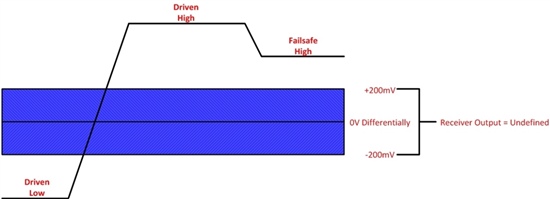

圖1顯示了典型多點LVDS總線的框圖。總線和接收器輸入之間的連接長度應盡可能短。圖1所示的故障安全偏置電路提供約1.2V的共模偏置。當總線不受Tx驅動,或總線長時間沒有狀態轉換時,電路還會設置一個50mV至100mV的小差分電壓,以驅動LVDS接收器輸出到確定的邏輯狀態。有關LVDS故障安全電路的一般討論,請參考應用筆記3662:了解LVDS故障安全電路。

圖1.交流耦合LVDS多點總線的總線和接收器輸入之間應使用短連接。

多點總線和點對點連接之間的偏置存在顯著差異:多點總線中的接收器必須是高阻抗的,而點對點連接中的接收器輸入阻抗必須與差分鏈路的100Ω阻抗匹配。因此,電阻值的變化是傳統故障安全偏置電路的一個常見弱點。本應用筆記探討了傳統的故障安全電路設計,討論了元件變化的問題,并提出了一種新的魯棒偏置電路。

傳統偏置電路及其弱點

最常見的傳統故障安全偏置電路由兩個LVDS輸入引腳上的兩個電阻分壓器組成。實現如圖2a所示。選擇電阻值時,兩個輸入引腳的電壓約為1.2V,兩個輸入引腳的電壓差為-50mV。這兩個輸入引腳的電壓根據圖2A所示的標稱電阻值計算得出。當總線未被驅動時,該電壓差將使接收器輸出邏輯低電平。

但是,如果考慮電阻容差,差分電壓的值可能會發生顯著變化。假設使用所有容差為1%的電阻,圖2b顯示電壓差可以達到-90mV,這是最壞情況下的負變化。或者,在相反的極端,圖2c顯示電壓差可以低至-16mV。因此,當電阻變化±1%時,故障安全差分輸入可能會在-80%至+68%之間變化。

圖2.常用的故障安全偏置電路(a)標稱電阻值,(b)在±1%容差下產生最大電壓差的設計,以及(c)在±1%容差下產生最小電壓差的設計。

較大的差分故障安全電壓是這種傳統電路設計的一個顯著弱點。較大的電壓差會引起多種反應:邏輯高電平或低電平的占空比變得不平衡;觸發閾值在輸入的一側向上移動,并降低觸發點的慢速速率,從而導致接收器的固有抖動增加。此外,如圖2c所示,低壓差值可能不足以激活故障安全功能。

為了克服傳統偏置電路中提到的弱點,請考慮以下新的偏置電路,該電路對電阻變化非常魯棒。

新型故障安全偏置電路

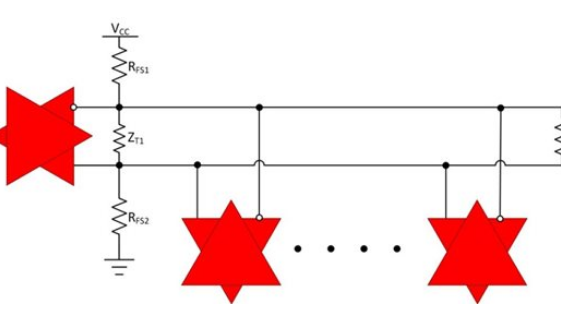

故障安全偏置電路的新拓撲結構可產生相對恒定的差分電壓,而與電阻變化無關。圖3所示為新電路示意圖。

圖3.圖中顯示了魯棒的故障安全偏置電路(a)標稱電阻值,(b)在±5%容差下產生最大電壓差的設計,以及(c)在±5%容差下產生最小電壓差的設計。

在新電路中,共模電壓從公共電源提供給兩個輸入引腳。差分電壓由一個輸入引腳上的下拉(或上拉)電阻產生。從圖3所示的值可以看出,即使使用±5%的電阻,故障安全差分電壓也僅在-15%至+15%之間變化,這比圖2所示電路要魯棒得多。該新電路可用于具有內部公共上拉故障保護電路的LVDS產品,如MAX9169/MAX9170和MAX9174/MAX9175,或具有弱內部共模偏置的電路,如MAX9242/MAX9244/MAX9246/MAX9254、MAX9218和MAX9248解串器產品。

審核編輯:郭婷

-

接收器

+關注

關注

14文章

2458瀏覽量

71797 -

總線

+關注

關注

10文章

2867瀏覽量

87987 -

lvds

+關注

關注

2文章

1036瀏覽量

65703

發布評論請先 登錄

相關推薦

差分總線的故障安全偏置如何實現

Ameya360故障安全電機控制解決方案

影響電路魯棒性的設計因素思考

差分總線的故障安全偏置功能設計如何實現?

魯棒性是什么意思_Robust為什么翻譯成魯棒性

Linux的魯棒性度量詳解及魯棒性關聯測試分析

獲得連接:對那些會被爭用的總線進行故障安全偏置

西門子F-AI 4xU電壓型故障安全模塊的使用

對那些會被爭用的總線進行故障安全偏置

基于故障安全的雙手操作指令介紹

用于故障安全偏置的替代魯棒電路結構介紹

用于故障安全偏置的替代魯棒電路結構介紹

評論